PARWANCPU状态机设计Word格式.docx

PARWANCPU状态机设计Word格式.docx

- 文档编号:19761831

- 上传时间:2023-01-09

- 格式:DOCX

- 页数:16

- 大小:474.56KB

PARWANCPU状态机设计Word格式.docx

《PARWANCPU状态机设计Word格式.docx》由会员分享,可在线阅读,更多相关《PARWANCPU状态机设计Word格式.docx(16页珍藏版)》请在冰豆网上搜索。

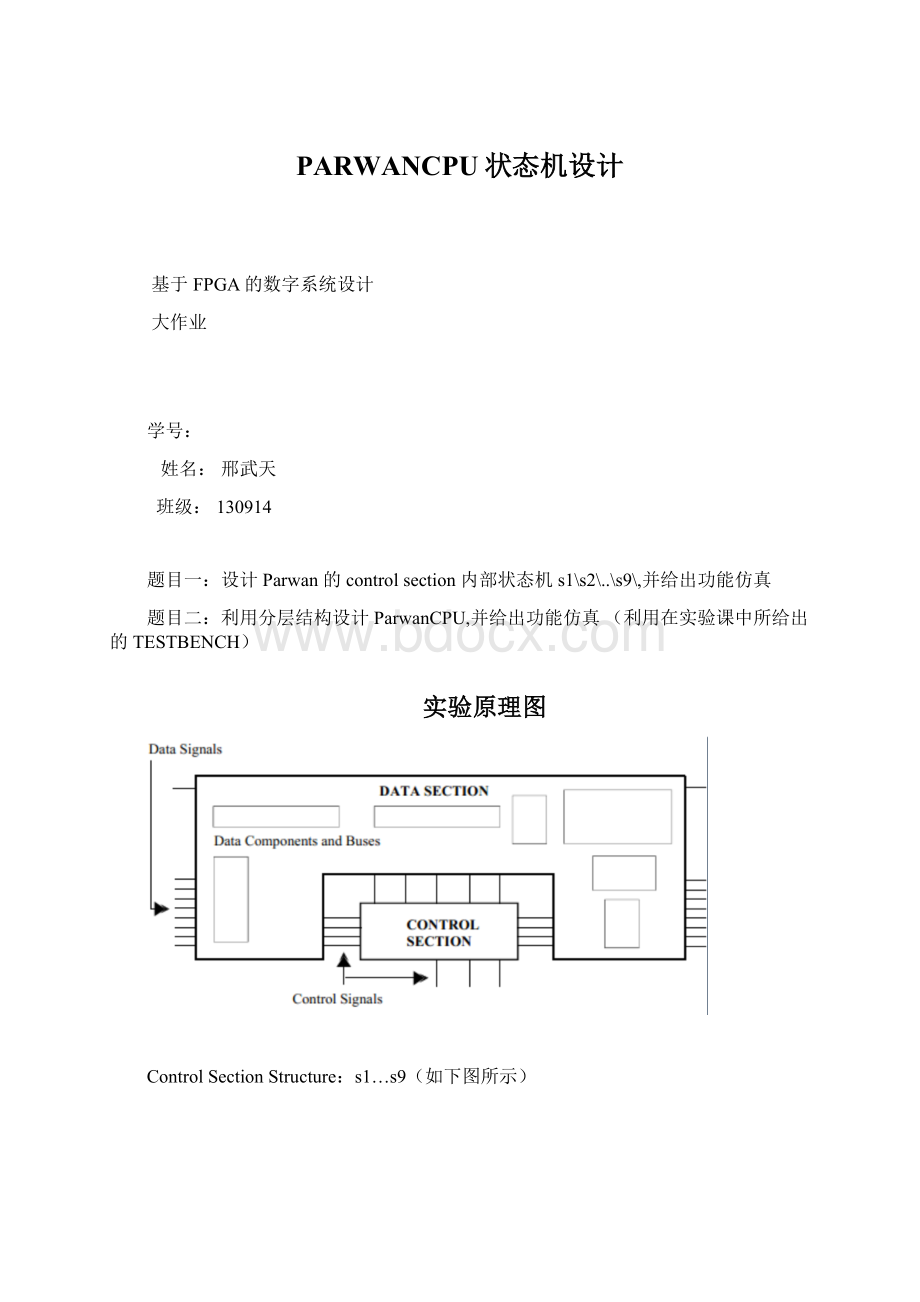

(1)选择菜单栏中的Project->

NewSource。

(2)在SelectSourceType窗口中,选择左侧的VHDLTestBench,在右侧FileName栏中输入文件名par_control_unit_tb

(3)单击Next按钮,选择关联文件。

实验截图

实验代码

在实现过程中,除了定义CPU的信号接口外,还设置了一个输出类型的接口,名字叫present_state_value,主要是用来在调试或仿真的过程中输出CPU所处的状态,便于调试分析。

整个状态机的实现过程主要使用了case…IS…when逻辑结构。

用了present_state和next_state两个状态变量。

详细的实现代码如下所示:

LIBRARYIEEE;

USE

--

ENTITYpar_control_unitIS

PORT(clk:

INstd_logic;

--registercontrolsignals:

load_ac,zero_ac,

load_ir,

increment_pc,load_page_pc,load_offset_pc,reset_pc,

load_page_mar,load_offset_mar,

load_sr,cm_carry_sr,

--busconnectioncontrolsignals:

pc_on_mar_page_bus,ir_on_mar_page_bus,

pc_on_mar_offset_bus,dbus_on_mar_offset_bus,

pc_offset_on_dbus,obus_on_dbus,databus_on_dbus,

mar_on_adbus,

dbus_on_databus,

--logicunitfunctioncontroloutputs:

arith_shift_left,arith_shift_right:

OUTstd_logic;

alu_and,alu_not,alu_a,alu_add,alu_b,alu_sub:

outstd_logic;

--inputsfromthedatasection:

ir_lines:

INstd_logic_vector(7DOWNTO0);

status:

INstd_logic_vector(3DOWNTO0);

--memorycontrolandotherexternalsignals:

read_mem,write_mem:

interrupt:

--test

present_state_value:

outstd_logic_vector(3DOWNTO0)

);

ENDpar_control_unit;

ARCHITECTUREdataflow_synthesizableOFpar_control_unitIS

TYPEcpu_statesIS(s1,s2,s3,s4,s5,s6,s7,s8,s9);

SIGNALpresent_state,next_state:

cpu_states;

SIGNALnext_state_value:

std_logic_vector(3DOWNTO0);

BEGIN

clocking:

PROCESS(clk,interrupt)

BEGIN

IF(interrupt='

1'

)THEN

present_state<

=s1;

present_state_value<

="

0001"

;

ELSIFclk'

EVENTANDclk='

0'

THEN

=next_state;

=next_state_value;

ENDIF;

ENDPROCESSclocking;

--

sequencing:

PROCESS(present_state,ir_lines,status,

interrupt)

load_ac<

='

zero_ac<

load_ir<

increment_pc<

load_page_pc<

load_offset_pc<

reset_pc

<

load_page_mar<

load_offset_mar<

load_sr<

cm_carry_sr<

pc_on_mar_page_bus<

ir_on_mar_page_bus<

pc_on_mar_offset_bus<

dbus_on_mar_offset_bus<

=

'

pc_offset_on_dbus<

obus_on_dbus<

databus_on_dbus<

mar_on_adbus<

dbus_on_databus<

arith_shift_left<

arith_shift_right<

alu_and<

='

alu_not<

alu_a<

alu_add<

alu_b<

alu_sub<

read_mem<

write_mem<

CASEpresent_stateIS

WHENs1=>

-------------------------------------------1

reset_pc<

next_state<

next_state_value<

ELSE

=s2;

0010"

WHENs2=>

---------------------------------------2

--readmemoryintoir

alu_a<

load_ir<

=s3;

next_state_value<

0011"

WHENs3=>

--------------------------------------3

IF(ir_lines(7DOWNTO4)/="

1110"

=s4;

0100"

CASEir_lines(3DOWNTO0)IS

WHEN"

=>

--cla

--cmc

1000"

--asl

alu_b<

1001"

--asr

WHENOTHERS=>

NULL;

ENDCASE;

WHENs4=>

----------------------------------------4

--readmemoryintomaroffset

IF(ir_lines(7DOWNTO6)/="

11"

)THEN

ir_on_mar_page_bus<

IF(ir_lines(4)='

)

next_state<

=s5;

next_state_value<

0101"

ELSE

=s6;

0110"

ELSE--jsrorbra,donotaltermar

--page

IF(ir_lines(5)='

--jsr

=s7;

0111"

=s9;

WHENs5=>

---------------------------------------5

--readactualoperandfrommemoryintomar

--offset

mar_on_adbus<

WHENs6=>

--------------------------------------6

IF(ir_lines(7DOWNTO5)="

100"

)THEN--jmp

ELSIF(ir_lines(7DOWNTO5)="

101"

--maronadbus,acondatabus,write

--tomemory

alu_b<

ELSIF(ir_lines(7)='

)THEN------

--lda,and,add,sub

--maronadbus,readmemoryfor

--operand,performoperation

IF(ir_lines(6)='

)THEN

----lda,and

IF(ir_lines(5)='

THEN--lda

alu_a<

ELSE--and

alu_and<

ELSE----add,sub

THEN--add

alu_add<

ELSE--sub

alu_sub<

WHENs7=>

--------------------------------------------7

--writepcoffsettotopofsubroutine

=s8;

WHENs8=>

--------------------------------------8

WHENs9=>

-----------------------------------------9

IF(all_or(statusANDir_lines(3DOWNTO0))='

实验原理

2.1创建工程

2.2设计输入

选择Project->

Addcopyofsource,将实验的源代码添加到工程中。

2.3综合实现

(1)编写汇编测试代码

(2)用文本编辑器打开实验源代码中的文件。

(3)将测试代码转换为内存文件

(4)编译并执行程序

2.4设计仿真

2.5结果截图

编写testbench代码对以上的状态机进行功能仿真。

Testbench的核心代码如下:

stim_proc:

process

begin

--holdresetstatefor100ns.

waitfor10ns;

ir_lines<

="

01101111"

--SUBloc

waitforclk_period*10;

"

--JMPloc

--STAloc

--BRA_V_addr

--CLA

endprocess;

由上代码可见,在测试波形中,选取了4种ir_line的可能值来测试。

下面选择两处仿真波形进行分析:

图“STAloc”仿真波形图

从“STAloc”仿真波形图中,连续的时钟周期里,ir_line的值都为“”,可知该指令是“STA1111”。

结合parwan的状态转换关系来看,一开始CPU处于s1状态,由于interrupt=‘0’,转到s2状态,再转到s3状态,由于ir_line(7to4)!

=”1110”,转到s4状态,由于ir_line(7to4)=”11X0”转到s6状态,最后由于ir_line(7to5)=”1010”转回s1,完成一次循环周期。

还可以看到在相应的状态,相应的信号会被设为“1”,如s1中,信号load_page_mar、load_offset_mar、pc_on_mar_page_bus和pc_on_mar_offset_bus等信号为“1”,状态机的设计相符。

图“CLA”仿真波形图

从“CLA”仿真波形图中,我们主要从黄线部分开始往后看,在这的一个时钟周期后ir_line的值都为“”,parwan的指令集可知指令是“CLA”。

结合parwan的状态设计来看,一开始CPU处于s1状态,由于interrupt=‘0’,转到s2状态,再转到s3状态,由于ir_line(7to4)=”1110”,转到s2状态,最后在s2和s3中循环。

验证了程序的正确性。

实验总结:

本次作业以以前四次上机为基础,通过利用上机所得的实验能力和部分实验代码,进行本次的ParwanCPU设计,基本上来说,本次作业要比上机更有难度,首先,进行的一次综合性实验,其次,上机时均给出了实验步骤。

但不可否认的是,本次实验更能提高我们对ParwanCPU的理解,对提高我们的实验能力更有帮助。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- PARWANCPU 状态机 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx