串口硬件设计文档Word格式.docx

串口硬件设计文档Word格式.docx

- 文档编号:19750184

- 上传时间:2023-01-09

- 格式:DOCX

- 页数:16

- 大小:196.57KB

串口硬件设计文档Word格式.docx

《串口硬件设计文档Word格式.docx》由会员分享,可在线阅读,更多相关《串口硬件设计文档Word格式.docx(16页珍藏版)》请在冰豆网上搜索。

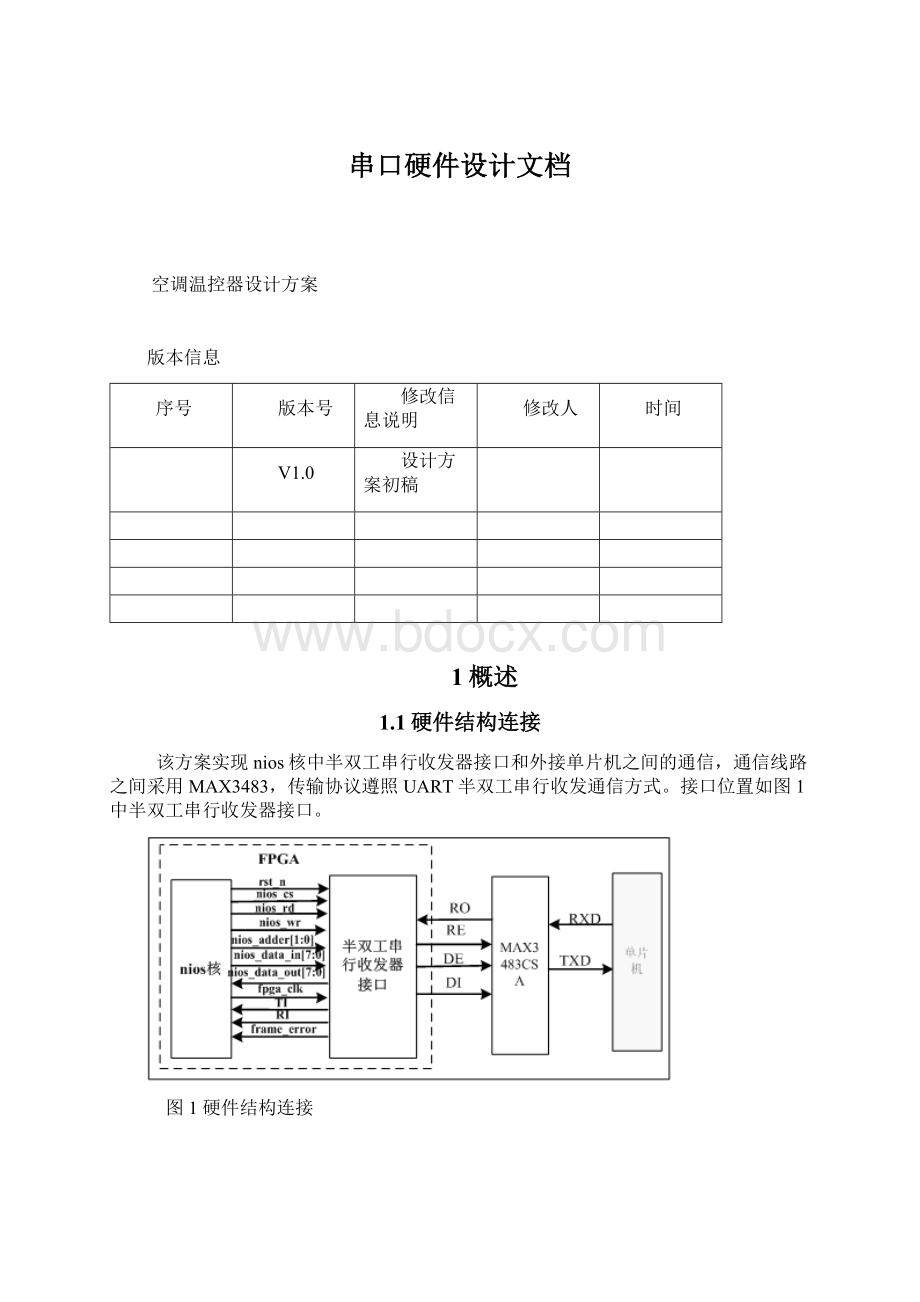

1.3MAX3483CSA介绍

MAX3483CSA采用半双工通信方式,RO和DI端分别为接收器的输出和驱动器的输入端,与单片机连接时只需分别与单片机的RXD端和TXD相连,/RE和DE端分别为接受和发送的使能端,/RE为逻辑0时,器件处于接收状态,当DE为逻辑1时,器件处于发送状态。

1.4软件访问接口函数流程图

图2发送接收数据过程

2.半双工串行收发器接口

2.1接口设计框图

图3半双工串行收发器结构图

2.2接口描述

收发器接口总结构如图4所示,在默认和复位情况下收发器处于发送状态。

在发送状态,查询到控制寄存器的值为0,并且tr_space为高时,则将DE和/RE清0,此时收发器从发送状态切换到接收状态。

在接收状态,查询到控制寄存器的值为1,并且r_space为高时,则将DE和/RE置1,收发器从接收状态切换到发送状态。

发送状态时,在发送空闲(tr_space为高)期间检测到发送数据缓冲寄存器有数据(tr_buf_empty_ind为低),首先将缓冲器的数据搬到移位寄存器,并且给高位加1,低位加0,同时将tr_buf_empty_ind信号置高,接着启动发送波特率计数器,同时将tr_space信号清0,然后每隔16个uart_clk时钟周期发送1位数据,发送完最后1位数据后,再次将tr_space置高,表示发送空闲。

接收状态时,首先检测下降沿,当检测到下降沿后,将re_space信号清0,同时启动接收数据波特率计数器,当计数器加到8时,采样RO的值,为低,表示此时是一个起始信号,然后每隔16个uart_clk时钟周期接收1位数据,当接收到第9位数据,也就是停止位时,判断停止位是否正确,若正确则将数据写到接收缓冲寄存器,同时将re_space信号置高,若停止位不正确则给出一个帧出错指示信号,并放弃数据输出。

当把数据从移位寄存器写到接收缓冲寄存器时,将re_buf_full_ind置高,当cpu把数据从接收缓冲寄存器读走,将re_buf_full_ind信号清0。

fpga_clk为cpu工作时钟,频率为66.66MHZ,uart_clk为串行收发器接口的采样时钟,频率为串口数据传送波特率的16倍,数据传送的波特率为9600bps。

2.3接口定义

引脚名称

I/O

功能描述

备注

1.

rst_n

I

复位信号,低有效

2.

fpga_clk

cpu工作时钟,频率为66.66MHZ

3.

nios_cs

cpu发送的片选信号,低有效

4.

nios_wr

cpu发送的写使能,低有效

5.

nios_rd

cpu发送的读使能,低有效

6.

nios_adder[1:

0]

cpu访问接口内部寄存器的地址

7.

nios_data_in[7:

cpu向外接单片机中发送的数据

8.

nios_data_out[7:

O

Cpu从外接单片机中接收的数据

9.

RO

串行数据接收引脚

10.

/RE

接收使能,低有效

11.

DI

串行数据发送引脚

12.

DE

发送使能,高有效

13.

TI

发送完成信号,高有效

14

RI

接收完成信号,高有效

15

fram_error

帧出错信号,高有效

3.控制模块

3.1功能描述

该模块主要实现以下功能:

●根据tr_space、re_space和控制寄存器的值改变DE和/RE,实现收发器状态的切换

●生成发送缓冲器写使能,接收缓冲器读使能,状态寄存器读使能信号。

3.2内部寄存器说明

寄存器名称

读/写

地址

寄存器说明

control_reg

读写

00

读写控制寄存器,最低位为读写判

断位,0,表示发送,1表示接收。

其它位保留。

uart_state

只读

01

状态寄存器,8位,低3位状态标

志位,bit0发送数据缓冲寄存器空

满标志位,1为空,0为满。

bit1

接收缓冲寄存器空满标志,1为满,

0为空。

bit2帧错误指示信号,1

表示有错误,0表示正确。

其它位

保留。

tran_buf_reg

只写

10

发送缓冲寄存器,8位,只有缓冲寄存器写使能有效时,cpu才能向该寄存器写数据。

rece_buf_reg

11

接收缓冲寄存器,8位,只有接收缓冲寄存器读使能有效时,cpu才能读该寄存器。

3.3结构框图

图4控制模块总体框图

3.4接口定义

Cpu工作时钟,频率为66.66mhz,上升沿采样,占空比为50%。

uart_clk

分频后产生的采样时钟,频率为波特率的16倍,上升沿采样,占空比为50%

14.

15.

tr_space

发送空闲状态指示信号,高有效

16.

trbuf_empty_ind

发送缓冲寄存器数据空指示信号,高有效

17.

trdata_reg_set

发送缓冲寄存器写使能信号,高有效

18.

rece_buf_reg[7:

接收缓冲寄存器数据输出

19.

rebuf_full_ind

接收缓冲寄存器数据满指示信号,好有效

20.

stopbit_err_ind

帧错误izhishi信号,高有效

21.

re_space

接收状态空闲指示信号,高有效

22.

state_reg_sel

状态寄存器读使能信号,高有效

23.

redata_reg_sel

接收缓冲寄存器读使能信号,高有效

4.接收模块

4.1功能描述

该部分主要完成以下功能:

●完成帧起始信号的检测

●按照uart协议正确接收RO上数据,并且写到接收缓冲寄存器内。

●当接收数据有误时,发送错误指示信号,等待CPU读取后,将错误指示信号清除。

●生成re_space、rebuf_full_ind指示信号

4.2设计框图

4.2.1总体设计框图

图5接收模块总体框图

图6中控制逻辑部分为状态机,具体状态转移如下所讲。

Uart_rece_begin为检测到下降沿的指示信号,re_frame_error和re_valid为状态机的输出信号,用fpga_clk时钟的上升沿分别检测re_frame_error和re_valid信号的下降沿,检测到下降沿的时候让stopbit_err_ind和rebuf_full_ind分别置1,当cpu把状态寄存器的值读走将stopbit_err_ind信号清0.当cpu把接收缓冲寄存器的数据读走,rebuf_full_ind信号清0。

4.2.2接收控制逻辑部分

图6接收部分状态机

re_idle接收空闲状态;

start接收帧起始信号状态,rece接收数据状态。

复位时处于接收空闲状态,当检测到下降沿后进入start状态,此时启动接收波特率计数器,当计数器计到8时,检测RO的值,为0,表示帧起始信号,则进入rece接收数据状态。

检测RO的值,为1,进入空闲状态。

接收完数据后跳到空闲状态。

在接收空闲状态re_space信号为高,其余状态信号都为低,即re_space=(re_state==re_idle)。

4.3接口定义

4.4接收时序图

图7正确数据

图8错误数据

5.发送模块

5.1功能描述

该模块实现以下功能

●把数据从发送缓冲寄存器搬到移位寄存器,按照uart协议,正确发送数据

●生成tr_space、trbuf_empty_ind指示信号

5.2设计框图

5.2.1总体设计框图

图7发送部分整体框图

图7中控制逻辑部分为状态机,具体状态转移如下所讲。

状态控制输出tr_space信号,用fpga_clk时钟的上升沿分别检测tr_space信号的下降沿,检测到下降沿的时候让trbuf_empty_ind信号置高,当cpu向缓冲寄存器写入数据,则把trbuf_empty_ind信号清0。

5.2.2发送控制逻辑部分

图8发送过程状态图

tr_idle发送空闲状态;

init发送初始化状态,tran发送数据状态。

复位时处于发送空闲状态,在发送状态检测到缓冲寄存器有数据,则进入init状态,完成数据从缓冲寄存器哦移位寄存器的搬移,然后跳转到发送状态,当发送完最后一位数据时,状态机到到发送空闲状态。

在发送状态(tran)tr_space为低,其他状态tr_space都为高,即tr_space=!

(tr_state==tran)。

5.3接口定义

5.4发送时序图

图9发送过程时序图

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 串口 硬件 设计 文档

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx