FPGA实验四VGA 显示的设计Word文档格式.docx

FPGA实验四VGA 显示的设计Word文档格式.docx

- 文档编号:19712151

- 上传时间:2023-01-09

- 格式:DOCX

- 页数:28

- 大小:1.15MB

FPGA实验四VGA 显示的设计Word文档格式.docx

《FPGA实验四VGA 显示的设计Word文档格式.docx》由会员分享,可在线阅读,更多相关《FPGA实验四VGA 显示的设计Word文档格式.docx(28页珍藏版)》请在冰豆网上搜索。

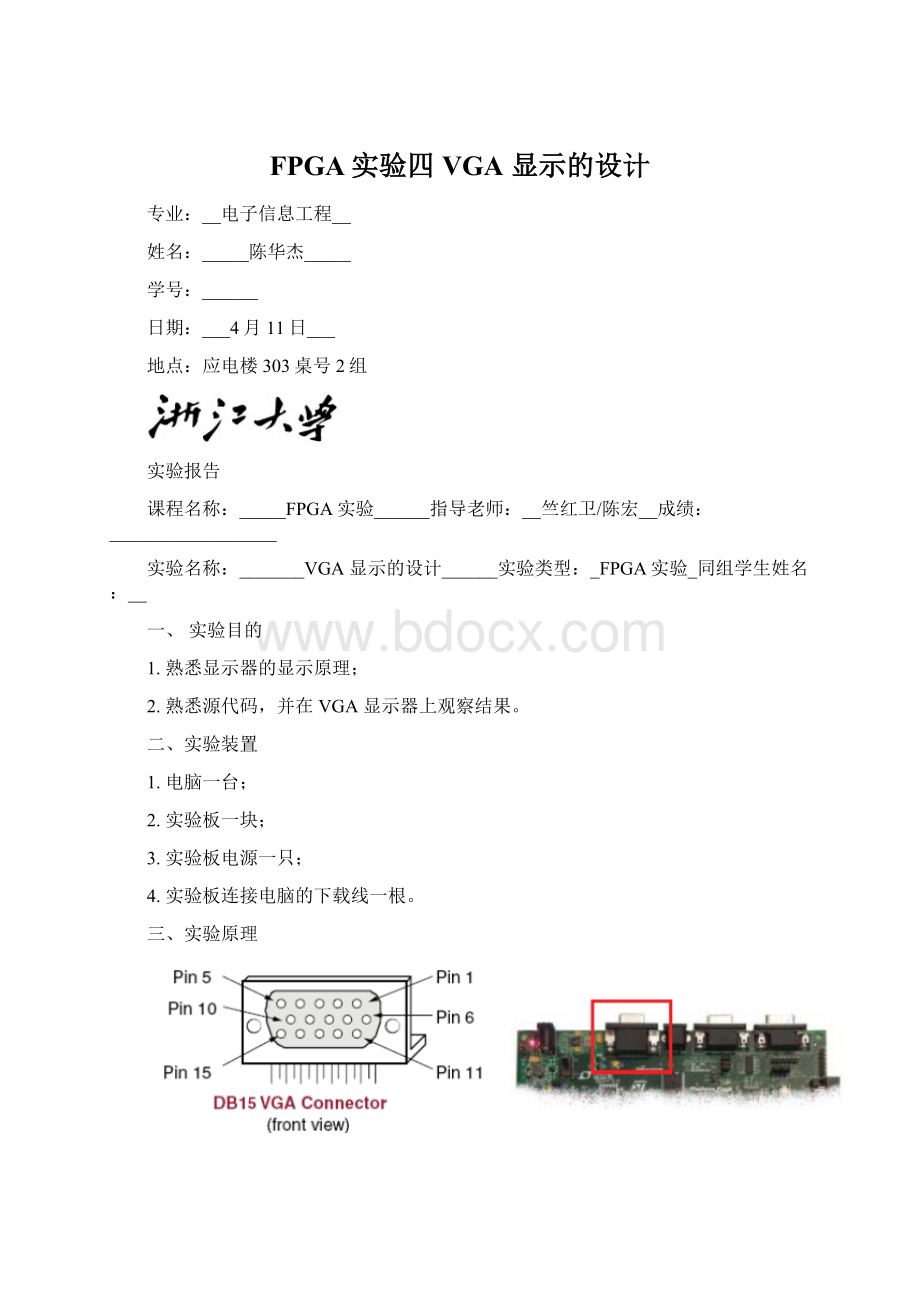

G15"

vga_g0"

H15"

vga_hs"

F15"

vga_r0"

H14"

vga_vs"

F14"

源代码如下:

modulevga_VibesIC(clk,rst_n,vga_hs,vga_vs,vga_r0,vga_g0,vga_b0);

inputclk;

inputrst_n;

outputvga_hs;

outputvga_vs;

outputvga_r0,vga_g0,vga_b0;

wirehsync;

wirevsync;

wirevalid;

wire[9:

0]x_cnt;

0]y_cnt;

0]char_sel;

wire[15:

0]char;

//设定屏幕分辨率:

800x600

0]xpos;

//[0...799]

0]ypos;

//[0...599]

regcolor;

assignxpos=x_cnt-10'

d180;

//确定X轴像素位置

assignypos=y_cnt-10'

d35;

//确定Y轴像素位置

sync_gen_50msync_gen_50m_int(

.clk(clk),

.rst_n(rst_n),

.hsync(hsync),

.vsync(vsync),

.valid(valid),

.x_cnt(x_cnt),

.y_cnt(y_cnt)

);

wiretable0=((ypos>

10'

d140&

&

ypos<

d460)&

(xpos>

d160&

xpos<

d640));

wireline0=((ypos==10'

d140||ypos==10'

d460)&

(xpos>

d640)||

(xpos==10'

d160||xpos==10'

d640)&

(ypos>

d460));

wireword0=((xpos>

d204)&

(xpos<

d588)&

(ypos>

d96)&

(ypos<

d128));

wireword=word0&

color;

assignvga_r0=valid?

(word?

1'

b1:

(line0?

(table0?

b0:

b0))):

b0;

assignvga_g0=valid?

assignvga_b0=valid?

b1))):

assignvga_hs=hsync;

assignvga_vs=vsync;

assignchar_sel=xpos-10'

d204;

char_rom_VibesICchar_rom_VibesIC_inst(

.addr({char_sel[9:

5],ypos[4:

1]}),//字符的Y轴由16pixel变为32pixel

.data(char)

always@(char_sel[4:

1]orchar)

begin

case(char_sel[4:

1])

4'

h0:

color=char[15];

h1:

color=char[14];

h2:

color=char[13];

h3:

color=char[12];

h4:

color=char[11];

h5:

color=char[10];

h6:

color=char[9];

h7:

color=char[8];

h8:

color=char[7];

h9:

color=char[6];

hA:

color=char[5];

hB:

color=char[4];

hC:

color=char[3];

hD:

color=char[2];

hE:

color=char[1];

hF:

color=char[0];

endcase

end

endmodule

modulesync_gen_50m(clk,rst_n,hsync,vsync,valid,x_cnt,y_cnt);

inputrst_n;

outputhsync;

outputvsync;

outputvalid;

output[9:

reghsync;

regvsync;

regvalid;

reg[9:

//---------------------------------------------------------------------------

//两个Always中可以使用相同的判断条件

always@(posedgeclkornegedgerst_n)

if(!

rst_n)

x_cnt<

=10'

d0;

elseif(x_cnt==10'

d1000)

else

=x_cnt+1'

b1;

y_cnt<

elseif(y_cnt==10'

d665)

=y_cnt+1'

//hsync<

=x_cnt<

d50;

中第一个"

<

="

为赋值语句,第二个"

为比较语句

//本代码的操作为:

比较后再赋值。

hsync<

=1'

vsync<

d50;

//产生hsync信号

=y_cnt<

d6;

//产生vsync信号

valid<

=((x_cnt>

d180)&

(x_cnt<

d980)&

(y_cnt>

d35)&

(y_cnt<

d635));

Endmodule

modulechar_rom_VibesIC(addr,data);

//字模产生模块

input[8:

0]addr;

output[15:

0]data;

reg[15:

//Amemoryisimplemented

//usingacasestatement

always@(addr)

case(addr)

9'

h000:

data=16'

H0040;

//威

h001:

H0050;

h002:

H0048;

h003:

H3FFC;

h004:

H2040;

h005:

H3F48;

h006:

H284C;

h007:

H2848;

h008:

H3F50;

h009:

H2930;

h00a:

H2920;

h00b:

H2620;

h00c:

H2552;

h00d:

H488A;

h00e:

H5304;

h00f:

H8000;

h010:

H0000;

//百

h011:

HFFFE;

h012:

H0300;

h013:

H0200;

h014:

H1FF0;

h015:

H1010;

h016:

h017:

h018:

h019:

h01a:

h01b:

h01c:

h01d:

h01e:

h01f:

h020:

h0840;

//仕

h021:

h0C40;

h022:

h1840;

h023:

h1040;

h024:

h3044;

h025:

h2FFE;

h026:

h6040;

h027:

hA040;

h028:

h2040;

h029:

h02a:

h02b:

h02c:

h2044;

h02d:

h02e:

h2000;

h02f:

h0000;

h030:

//

h031:

h032:

h033:

h034:

h035:

h036:

h037:

h038:

h039:

h03a:

h03b:

h03c:

h03d:

h03e:

h03f:

h040:

//F

h041:

h042:

h043:

hFC00;

h044:

h4200;

h045:

h4800;

h046:

h047:

h7800;

h048:

h049:

h04a:

h4000;

h04b:

h04c:

h04d:

hE000;

h04e:

h04f:

h050:

//P

h051:

h052:

h053:

h054:

h055:

h056:

h057:

h058:

h7C00;

h059:

h05a:

h05b:

h05c:

h05d:

h05e:

h05f:

h060:

//G

h061:

h062:

h063:

h3C00;

h064:

h4400;

h065:

h066:

h8000;

h067:

h068:

h069:

h8E00;

h06a:

h8400;

h06b:

h06c:

h06d:

h3800;

h06e:

h06f:

h070:

//A

h071:

h072:

h073:

h1000;

h074:

h075:

h1800;

h076:

h2800;

h077:

h078:

h2400;

h079:

h07a:

h07b:

h07c:

h07d:

hE700;

h07e:

h07f:

h080:

//开

h081:

h7FFE;

h082:

h0420;

h083:

h084:

h085:

h086:

hFFFE;

h087:

h088:

h089:

h08a:

h0820;

h08b:

h08c:

h1020;

h08d:

h2020;

h08e:

h4020;

h08f:

h090:

h0200;

//发

h091:

h2240;

h092:

h2230;

h093:

h2210;

h094:

h095:

h096:

h0400;

h097:

h07E0;

h098:

h0C20;

h099:

h0A20;

h09a:

h09b:

h1140;

h09c:

h2080;

h09d:

h4160;

h09e:

h861C;

h09f:

h1808;

h0a0:

h007C;

//系

h0a1:

h3F80;

h0a2:

h0220;

h0a3:

h0a4:

h0a5:

h1F80;

h0a6:

h0320;

h0a7:

h0C10;

h0a8:

h3FF8;

h0a9:

h108C;

h0aa:

h04A0;

h0ab:

h0890;

h0ac:

h1088;

h0ad:

h2084;

h0ae:

h4284;

h0af:

h0100;

h0b0:

//统

h0b1:

h0b2:

h23FE;

h0b3:

h0b4:

h4440;

h0b5:

hF888;

h0b6:

h0904;

h0b7:

h13FE;

h0b8:

h2094;

h0b9:

h7C90;

h0ba:

h0090;

h0bb:

h0bc:

h1D12;

h0bd:

hE112;

h0be:

h020E;

h0

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA实验四VGA 显示的设计 FPGA 实验 VGA 显示 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx