FPGA实验报告2Word文档下载推荐.docx

FPGA实验报告2Word文档下载推荐.docx

- 文档编号:19673357

- 上传时间:2023-01-08

- 格式:DOCX

- 页数:23

- 大小:391.28KB

FPGA实验报告2Word文档下载推荐.docx

《FPGA实验报告2Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《FPGA实验报告2Word文档下载推荐.docx(23页珍藏版)》请在冰豆网上搜索。

ARCHITECTUREoneOFor2aIS

BEGIN

c<

=aORb;

END;

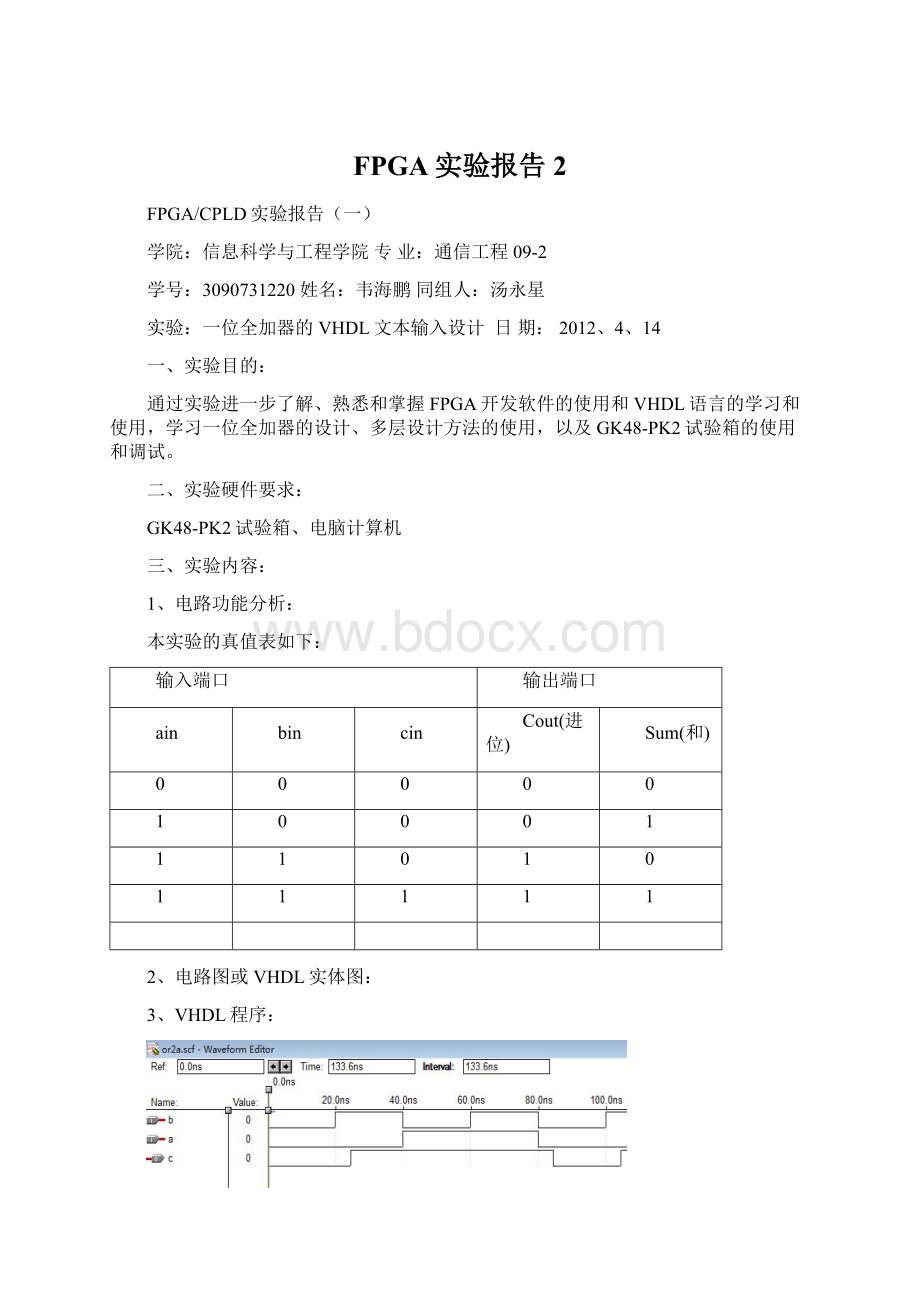

波形如图:

半加器描述:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYadderIS

INSTD_LOGIC;

co,so:

OUTSTD_LOGIC);

ENDadder;

ARCHITECTUREfh1OFadderis

BEGIN

so<

=NOT(aXOR(NOTb));

co<

=aANDb;

END;

1位二进制全加器顶层设计描述

ENTITYf_adderIS

PORT(ain,bin,cin:

cout,sum:

ENDf_adder;

ARCHITECTUREfd1OFf_adderIS

COMPONENTadder

PORT(a,b:

co,so:

ENDCOMPONENT;

COMPONENTor2a

PORT(a,b:

SIGNALd,e,f:

STD_LOGIC;

u1:

adderPORTMAP(a=>

ain,b=>

bin,

co=>

d,so=>

e);

u2:

e,b=>

cin,

f,so=>

sum);

u3:

or2aPORTMAP(a=>

d,b=>

f,c=>

cout);

ENDfd1;

仿真如图:

4、仿真波形图和波形解释:

(仿真见上图)

波形解释:

如真值表与波形图所示,ain、bin、cin都是输入端,cout是高位进位计数端,sum是全加和。

三个输入端有一个为1时,和sum值为1,进位cout值为0;

当三个输入端有两个为1时,和sum值为0,进位cout值为1;

当三个输入端都为1是,sum和cout的值均为1。

5、对应硬件选择和管脚分配关系:

在对应硬件芯片选择时,我们选择ACEX1K系列的EP1K30TC144-3芯片。

并选择试验电路结构图(6)来进行试验,用LED等D1、D2分别表示输出端sum和cout,它们对应的管脚是30、31;

分别用键3、4、5作为输入端ain、bin、cin。

它们的管脚分配分别是20、21、22。

管脚分配如下图:

6、试验结果说明:

将程序下载到试验箱之后,依照摁下键3、4、5,LED灯出现了对应的变化,如:

摁下三个键的其中一个,只有代表sum的D1亮;

摁下其中两个则只有代表cout的D2亮,如果三个都摁下了,则D1、D2都亮;

如果把输入键都摁灭,这D1、D2都不亮。

实验结果表明:

实验结果成功,虽然我们还是第一次真是接触正式的实验,可是在老师的指导下并经过我们的一番学习和摸索,我们成功把实验完成了。

FPGA/CPLD实验报告

(二)

2选1多路选择器VHDL设计日期:

通过实验进一步了解、熟悉和掌握FPGA开发软件的使用和加强VHDL语言的学习和使用,学习2选1多路选择器的设计以及掌握并加强GK48-PK2试验箱的使用和调试。

输入端

输出端

A

D0

D1

F

x

2、VHDL程序如下:

libraryieee;

useieee.std_logic_1164.all;

entityxuanzeqiis

port(a,b:

instd_logic;

s:

y:

outstd_logic);

endxuanzeqi;

architectureoneofxuanzeqiis

begin

process(a,b,s)

begin

ifs='

0'

then

y<

=a;

elsey<

=b;

endif;

endprocess;

endone;

3、仿真波形图和波形解释:

(1)、仿真波形图如下:

(2)、波形解释:

如真值表与波形图所示,s、a、b是信号输入端,y为信号输出端,其中s是选择输出端。

当s为低电平时,选择b输入端的信号在y端输出;

当s为高电平时,选择a输入端的信号在y端输出。

4、对应硬件选择和管分配关系:

并选择实验电路结构图(6),用LED灯D1来作为y端的输出显示,键3、4、5分别作为s、a、b输入端,它们实际分配情况如下:

5、实验结果说明:

将程序下载到实验箱之后,摁动键3、4、5,LED灯D1出现了相应的变化,如:

当键3没摁下去(即s=0),输出显示端LED灯由键4(即b)来控制,它的输出和键4的输入相同;

同理,当键3摁下去(即s=1),输出显示端LED灯由键5(即a)来控制,它的输出此时与键5相同。

FPGA/CPLD实验报告(三)

八位硬件加法器VHDL设计日期:

通过实验进一步了解、熟悉和掌握FPGA开发软件的使用和VHDL语言的学习和使用,学习八位硬件加法器VHDL设计方法的使用,以及GK48-PK2试验箱的使用和调试。

ENDENTITYf_adder;

COMPONENTh_adder

ENDCOMPONENT;

SIGNALd,e,f:

h_adderPORTMAP(a=>

bin,co=>

cin,co=>

ENDfd1;

我们的实验结果成功,虽然我们还是第一次真是接触正式的实验,可是在老师的指导下并经过我们的一番学习和摸索,我们成功把实验完成了。

FPGA/CPLD实验报告(四)

含异步清0和同步时钟使能的4位加法计数器日期:

通过实验进一步了解、熟悉和掌握FPGA开发软件的使用和VHDL语言的学习和使用,学习含异步清0和同步时钟使能的4位加法计数器VHDL设计方法的使用,以及GK48-PK2试验箱的使用和调试。

三、实验原理:

如图是一含计数使能、异步复位和计数值并行预置功能4位加法计数器,例1是其VHDL描述。

由图所示,图中间是4位锁存器;

rst是异步清信号,高电平有效;

clk是锁存信号;

D[3..0]是4位数据输入端。

当ENA为'

1'

时,多路选择器将加1器的输出值加载于锁存器的数据端;

时将"

0000"

加载于锁存器。

四、实验内容:

VHDL程序如下:

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT4BIS

PORT(CLK:

RST:

ENA:

OUTY:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

ENDCNT4B;

ARCHITECTUREbehavOFCNT4BIS

SIGNALCQI:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

P_REG:

PROCESS(CLK,RST,ENA)

IFRST='

THENCQI<

="

;

ELSIFCLK'

EVENTANDCLK='

THEN

IFENA='

=CQI+1;

ENDIF;

OUTY<

=CQI;

ENDPROCESSP_REG;

--进位输出

COUT<

=CQI(0)ANDCQI

(1)ANDCQI

(2)ANDCQI(3);

ENDbehav;

波形说明:

如图可知,RST为异步清零信号输入端,高电平有效,,ena为使能端,cout为溢出端,outy为输出计数端,CLK为锁存信号;

当rst为低电平时开始计数,高电平时复位清零,当使能端ena上升沿时,并且CLK上升沿时进行数据锁存,OUTY输出一个数,然后当四位计数达到最大(即16)时,溢出端COUT纪录一个数,然后从新开始计数。

五、实验结果:

由于使用的是时序仿真,因此输出波形有所延迟,但是仿真为题目所要求的结果,因此仿真正确。

FPGA/CPLD实验报告(五)

7段数码显示译码器设计日期:

学习7段数码显示译码器设计、多层次设计方法、和总线数据输入方式的仿真。

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用VHDL译码程序在FPGA或CPLD中实现。

本项实验很容易实现这一目的。

例2作为7段BCD码译码器的设计,输出信号LED7S的7位分别接如实验图2数码管的7个段,高位在左,低位在右。

例如当LED7S输出为"

1101101"

时,数码管的7个段:

g、f、e、d、c、b、a分别接1、1、0、1、1、0、1,接有高电平的段发亮,于是数码管显示“5”。

四、实验内容

VHDL程序如下:

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDecL7SIS

PORT(A:

INSTD_LOGIC_VECTOR(3DOWNTO0);

LED7S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

END;

ARCHITECTUREoneOFDecL7SIS

PROCESS(A)

CASEA(3DOWNTO0)IS

WHEN"

=>

LED7S<

0111111"

;

--X“3F”0

0001"

0000110"

--X“06”1

0010"

1011011"

--X“5B”2

0011"

1001111"

--X“4F”3

0100"

1100110"

--X“66”4

0101"

--X“6D”5

0110"

1111101"

--X“7D”6

0111"

0000111"

--X“07”7

1000"

1111111"

--X“7F”8

1001"

1101111"

--X“6F”9

1010"

1110111"

--X“77”10

1011"

1111100"

--X“7C”11

1100"

0111001"

--X“39”12

1101"

1011110"

--X“5E”13

1110"

1111001"

--X“79”14

1111"

1110001"

--X“71”15

WHENOTHERS=>

NULL;

ENDCASE;

ENDPROCESS;

(右图为:

共阴数码管及其电路

)

仿真说明:

如图,A为七段显示输入端,LED7S[6..0]为显示输出端,高电平显示,当为‘0’时,输出为‘0111111’即数码管g不亮,其余的全亮,显示输出为‘0’,依次进行,显示0~16.

实验结果符合题目要求。

FPGA/CPLD实验报告(六)

数控分频器的设计日期:

学习数控分频器的设计、分析和测试方法.

数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,例3的数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将计数溢出位与预置数加载输入信号相接即可。

输入不同的CLK时钟频率和预置值D,给出如例3的时序波形

VHDL程序如下

ENTITYPULSEIS

PORT(CLK:

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

FOUT:

END;

ARCHITECTUREoneOFPULSEIS

SIGNALFULL:

P_REG:

PROCESS(CLK)

VARIABLECNT8:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

IFCLK'

IFCNT8="

11111111"

THEN

CNT8:

=D;

--当CNT8计数计满时,输入数据D被同步预置给计数器CNT8

FULL<

='

--同时使溢出标志信号FULL输出为高电平

ELSECNT8:

=CNT8+1;

--否则继续作加1计数

--且输出溢出标志信号FULL为低电平

P_DIV:

PROCESS(FULL)

VARIABLECNT2:

IFFULL'

EVENTANDFULL='

THENCNT2:

=NOTCNT2;

--如果溢出标志信号FULL为高电平,D触发器输出取反

IFCNT2='

THENFOUT<

ELSEFOUT<

ENDPROCESSP_DIV;

当给出不同输入值D时,FOUT输出不同频率(CLK周期=50ns),clk为输入时钟信号

FPGA/CPLD实验报告(七)

74LS138译码器日期:

通过学习器件手册,掌握设计、仿真并实现74LS138器件功能。

进一步了解、熟悉和掌握FPGA开发软件的使用和VHDL语言的学习和使用

元器件真值表:

INPUT

output

Enable

select

G1

G2

C

B

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

X

H

L

libraryieee;

entityls138is

port(g1,g2:

instd_logic;

a:

instd_logic_vector(2downto0);

b:

outstd_logic_vector(7downto0));

end;

architectureoneofls138is

process(g1,g2,a)

if(g1='

org2='

)then

b<

="

elsif(g1='

andg2='

casea(2downto0)is

when"

000"

=>

b<

01111111"

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx