EDA实验指导书应用篇2+7Word格式.docx

EDA实验指导书应用篇2+7Word格式.docx

- 文档编号:19624429

- 上传时间:2023-01-08

- 格式:DOCX

- 页数:24

- 大小:153.57KB

EDA实验指导书应用篇2+7Word格式.docx

《EDA实验指导书应用篇2+7Word格式.docx》由会员分享,可在线阅读,更多相关《EDA实验指导书应用篇2+7Word格式.docx(24页珍藏版)》请在冰豆网上搜索。

其工作原理与LED灯相似。

步进电机:

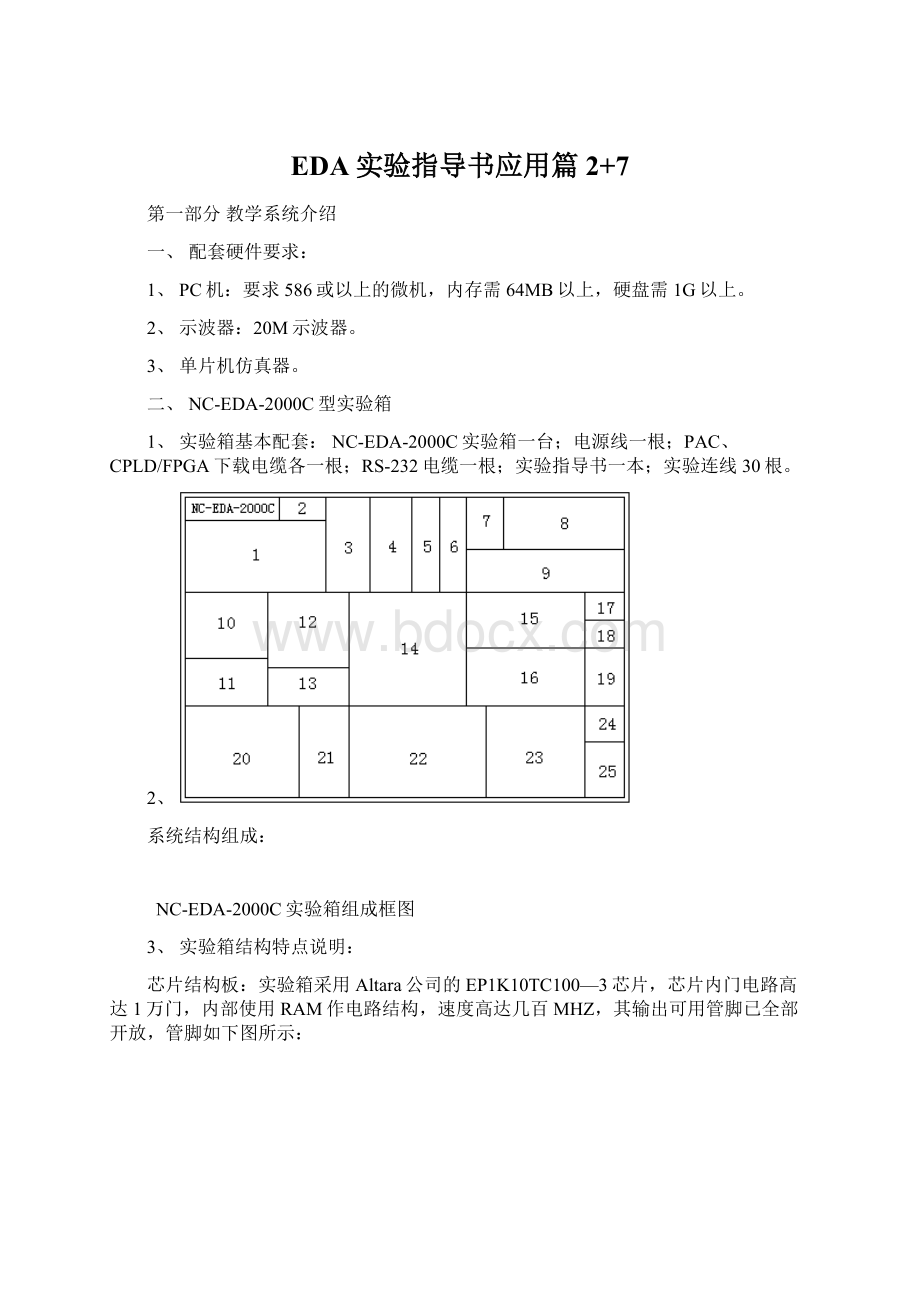

位于实验箱组成框图的10所示位置。

其工作原理将在实验中作详细介绍。

通过对模块下方的四个连接孔A、B、C、D输入控制信号来控制步进电机的转动。

其驱动电路如下所示:

步进电机驱动电路

蜂鸣器在实验箱组成框图中位于6所示位置,由一个蜂鸣器和一个喇叭组成。

通过对其输入不同的频率而发出不同的声音。

实验箱可以通过对中间的一个跳线的改变来选择蜂鸣器或喇叭。

当跳线帽位于左边时选择的是喇叭;

反之则选择的是蜂鸣器。

对模块下方的SPEAKER连接孔输入一个时钟信号使蜂鸣器或喇叭发声。

其工作原理如下图所示:

附图1:

1K10芯片管脚分布图

附图2:

第三部分实验部分

基础实验

实验一组合逻辑设计

实验四扫描显示电路的驱动

一、实验目的:

了解教学系统中8位七段数码管显示模块的工作原理,设计标准扫描驱动电路模块,以备后面实验调用。

二、硬件要求:

主芯片:

EP1K10TC100—3,时钟源,八位七段数码显示管,四位拨码开关。

三、实验内容:

1、用拨码开关产生8421BCD码,用CPLD产生字形编码电路和扫描驱动电路,然后进行仿真,观察波形,正确后进行设计实现,适配化分。

调节时钟频率,感受“扫描”的过程,并观察字符亮度和显示刷新的效果。

2、编一个简单的从0~F轮换显示十六进制的电路。

四、实验原理:

四位拨码开关提供8421BCD码,经译码电路后成为7段数码管的字形显示驱动信号。

(A…G)扫描电路通过可调时钟输出片选地址SEL[2..0]。

由SEL[2..0]和A..G决定了8位中的哪一位显示和显示什么字形.SEL[2..0]变化的快慢决定了扫描频率的快慢。

1、参考电路(时钟频率>

40HZ,如图2—4—1)

图2—4—1

参考电路(时钟频率<

2HZ,如图2—4—2)

图2—4—2

五、实验连线:

输入信号:

D3,D2,D1,D0所对应的管脚同四位拨码开关相连;

清零信号RESET所对应的管脚同按键开关相连;

时钟CLK所对应的管脚同实验箱上的时钟源相连;

输出信号:

代表扫描片选地址信号SEL2,SEL1,SEL0的管脚同四位扫描驱动地址的低3位相连,最高位地址接“0”(也可悬空);

代表7段字码驱动信号A,B,C,D,E,F,G的管脚分别同扫描数码管的段输入a,b,c,d,e,f,g相连。

六、实验报告:

1、字形编码的种类,即一个7段数码管可产生多少种字符,产生所有字符需多少根被译码信号线?

2、字符显示亮度同扫描频率的关系,且让人眼感觉不出光烁现象的最低扫描频率是多少?

实验五计数器及时序电路

1、了解时序电路的经典设计方法(D触发器和JK触发器和一般逻辑门组成的时序逻辑电路)。

2、了解通用同步计数器,异步计数器的使用方法。

3、了解用同步计数器通过清零阻塞法和预显数法得到循环任意进制计数器的方法。

4、理解时许电路和同步计数器加译码电路的联系,设计任意编码计数器。

5、了解同步芯片和异步芯片的区别。

二、硬件需求:

EP1K10TC100—3,时钟源,4位七段数码管。

1、用D触发器设计异步四位二进制加法计数器。

2、用JK触发器设计异步二—十进制减法计数器。

3、用74LS161两个宏连接成八位二进制同步计数器。

4、用74LS390两个宏连接成八位二—十进制异步计数器。

5、用74LS161清零和置数法组成六进制和十二进制计数器。

6、分别用D触发器和同步计数器加译码电路的方法构成7进制电路实现如下编码:

0,2,5,3,4,6,1。

四、实验原理及连线:

实验内容中的6个实验均要通过实验四的“扫描显示电路”内容进行显示,具体连线根据每个实验内容完成时的管脚化分和定义,同相应的输入、输出接口功能模块相连,扫描模块的连接参考实验四。

1、实验内容1的参考图2—5—1;

图2—5—1

说明:

计数时钟频率clk<1Hz;

扫描时钟频率ckdsp>40Hz;

四位D触发器接成异步计数器;

SEL0~SEL2为扫描地址(控制八位数码管的扫描顺序和速度);

A…G为显示译码输出,代表数码管的七个段位(a,b,c,d,e,f,g),

八位数码管同时顺序显示0~F。

应用实验

实验二梁祝音乐演奏实验

一、实验目的

1、了解普通扬声器的工作原理。

2、使用FPGA产生不同的音乐频率。

3、进一步体验FPGA的灵活性。

二、硬件要求

1、375KHz信号源。

2、FPGAEP1K10TC100—3主芯片。

3、扬声器。

三、实验原理

本实验是完成一小段音乐程序的开发,然后再用扬声器进行试听。

下面主要介绍一下完成本实验的几个主要部分的工作原理。

音符的产生:

音符的产生是利用计数器对输入的时钟信号进行分频,然后输出不同的频率来控制扬声器发不同的声音。

计数器必须是模可变的计数器,也就是其初始计数值可变,这样便可以对其进行初始化,使其从不同的初始值开始计数,实现对输入时钟信号的不同分频。

节拍的产生:

节拍也是利用计数器来实现,如果某一个音符需要维持的时间比较长,那么就可以在此计数器从计数值A到计数值B之间都维持该音符,很显然,A和B之间的间隔越大,那么该音符维持的时间也就越长。

乐谱的存储:

乐谱是一个固定的组合电路,根据不同的输入值,然后输出一个固定的值,该值就是音符产生计数器的分频的初始值。

适当的选择这些计数器和组合电路,便可完成不同的乐曲和不同节奏。

四、实验内容及步骤

本实验要完成的任务是设计一个驱动扬声器产生梁祝音乐的程序,设计步骤如下:

1、编写音乐输出的VHDL代码。

2、用MaxPlusII对其进行编译仿真。

3、在仿真确定无误后,选择芯片ACEX1KEP1K10TC100-3。

4、给芯片进行管脚绑定,在此进行编译。

5、根据自己绑定的管脚,在实验箱上对扬声器接口和FPGA之间进行正确连线。

6、给目标板下载代码,观看实验结果。

五、实验连线

如果是调用的本书提供的VHDL代码,则实验连线如下:

Clk:

时钟输入信号,接375KHz的时钟源。

Spk:

输出,接扬声器部分的输入端。

六、实验VHDL代码:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

--------------------------------------------------------------------

entitypmusicis

port(clk:

instd_logic;

--ClockSignal

spk:

bufferstd_logic);

--speakerdriver

endpmusic;

architecturebehaveofpmusicis

signaltone:

std_logic_vector(10downto0);

signaltone_count:

signaltone_index:

integerrange0to15;

signalclk10_count:

std_logic_vector(17downto0);

signaltime:

integerrange0to150;

signalclk10:

std_logic;

begin

process(clk)--generate10hzclocksignal

if(clk'

eventandclk='

1'

)then

clk10_count<

=clk10_count+1;

if(clk10_count=16#3fff#)then

clk10<

=notclk10;

endif;

endprocess;

process(clk10)

if(clk10'

eventandclk10='

if(time=150)then

time<

=0;

else

=time+1;

casetimeis

when0=>

tone_index<

=3;

when1=>

when2=>

when3=>

--

when4=>

=5;

when5=>

when6=>

when7=>

=6;

when8=>

=8;

when9=>

when10=>

when11=>

=9;

when12=>

when13=>

when14=>

when15=>

when16=>

=12;

when17=>

when18=>

when19=>

=15;

when20=>

=13;

when21=>

when22=>

=10;

when23=>

when24=>

when25=>

when26=>

when27=>

when28=>

when29=>

when30=>

when31=>

when32=>

when33=>

when34=>

when35=>

when36=>

=7;

when37=>

when38=>

when39=>

when40=>

when41=>

when42=>

when43=>

when44=>

when45=>

when46=>

when47=>

when48=>

when49=>

when50=>

when51=>

when52=>

when53=>

when54=>

when55=>

when56=>

when57=>

when58=>

when59=>

when60=>

when61=>

when62=>

when63=>

----

when64=>

when65=>

when66=>

when67=>

when68=>

when69=>

when70=>

when71=>

when72=>

when73=>

when74=>

when75=>

when76=>

when77=>

when78=>

when79=>

when80=>

when81=>

when82=>

when83=>

when84=>

when85=>

when86=>

when87=>

when88=>

when89=>

when90=>

when91=>

when92=>

when93=>

when94=>

when95=>

when96=>

when97=>

when98=>

when99=>

when100=>

when101=>

when102=>

when103=>

when104=>

when105=>

when106=>

when107=>

when108=>

when109=>

when110=>

when111=>

when112=>

when113=>

when114=>

when115=>

when116=>

when117=>

when118=>

when119=>

when120=>

when121=>

when122=>

when123=>

when124=>

when125=>

when126=>

when127=>

when128=>

when129=>

when130=>

when131=>

when132=>

when133=>

when134=>

when135=>

when136=>

when137=>

when138=>

when139=>

whenothers=>

endcase;

process(tone_index)

casetone_indexis

tone<

="

11111111111"

;

--nooutput

01100000101"

--773

01110010000"

--912

10000001100"

--1036

10010101101"

--1197

10100001010"

--1290

10101011100"

--1372

10110000010"

--1410

10111001000"

--1480

11000000110"

--1542

11001010110"

--1622

11010000100"

--1668

11011000000"

--1728

--others:

nooutput

process(clk)--controlthefrequenceofthespeaker

if(tone_count=16#7ff#)then

tone_count<

=tone;

if(tone<

2047)then

spk<

=notspk;

=tone_count+1;

endbehave;

一、实验报告

1、了解乐曲节拍产生的过程,注意每一音符的节拍长短的变化是由什么控制的?

2、改变时钟频率,看乐曲有什么改变?

3、熟悉音乐编程的过程,填入新的乐曲。

4、将两个或多个乐曲演奏电路合二为一,以一开关控制,可选择演奏不同的乐曲。

实验八步进电机控制实验

一、实验目的

1、了解步进电机的工作原理。

2、掌握用FPGA产生驱动步进电机的时序。

3、掌握用FPGA来控制步进电机转动的整个过程。

二、硬件要求

1、步进电机。

2、主芯片FPGAEP1K10TC100—3。

3、8个按键和一个拨挡开关。

4、可变时钟源。

三、实验原理

步进电机是工业过程控制及仪表中常用的控制元件之一,例如在机械装置中可以用丝杆把角度变为直线位移,也可以用步进电机带动螺旋电位器,调节电压或电源,从而实现对执行机械的控制。

步进电机可以直接用数字信号驱动,使用非常方便。

步进电机还具有快速启停、精确步进和定位等特点,因而在数控机床、绘图仪、打印机以及光学仪器中得到广泛的应用。

步进电机是工业控制及仪表中常用的控制元件之一,例如在机械装置中可以精确控制机械装置的旋转角度、移动距离等。

步进电机可以直接用数字信号来驱动,使用非常方便。

另外步进电机还具有快速起停、精确步进和定位的特点。

步进电机实际上是一个数据/角度转换器,三相步进电机的结构原理如下图所示:

三相步进电机的结构示意图

从图中可以看出,电机的定子有六个等分的磁极,A、A’、B、B’、C、C’,相邻的两个磁极之间夹角为60°

,相对的两个磁极组成一组(A—A’,B—B’,C—C’),当某一绕组有电流通过时,该绕组相应的两个磁极形成N极和S极,每个磁极上各有五个均分布的矩

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 实验 指导书 应用

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx