实验一门电路逻辑功能与测试Word文件下载.docx

实验一门电路逻辑功能与测试Word文件下载.docx

- 文档编号:19575558

- 上传时间:2023-01-07

- 格式:DOCX

- 页数:16

- 大小:415.10KB

实验一门电路逻辑功能与测试Word文件下载.docx

《实验一门电路逻辑功能与测试Word文件下载.docx》由会员分享,可在线阅读,更多相关《实验一门电路逻辑功能与测试Word文件下载.docx(16页珍藏版)》请在冰豆网上搜索。

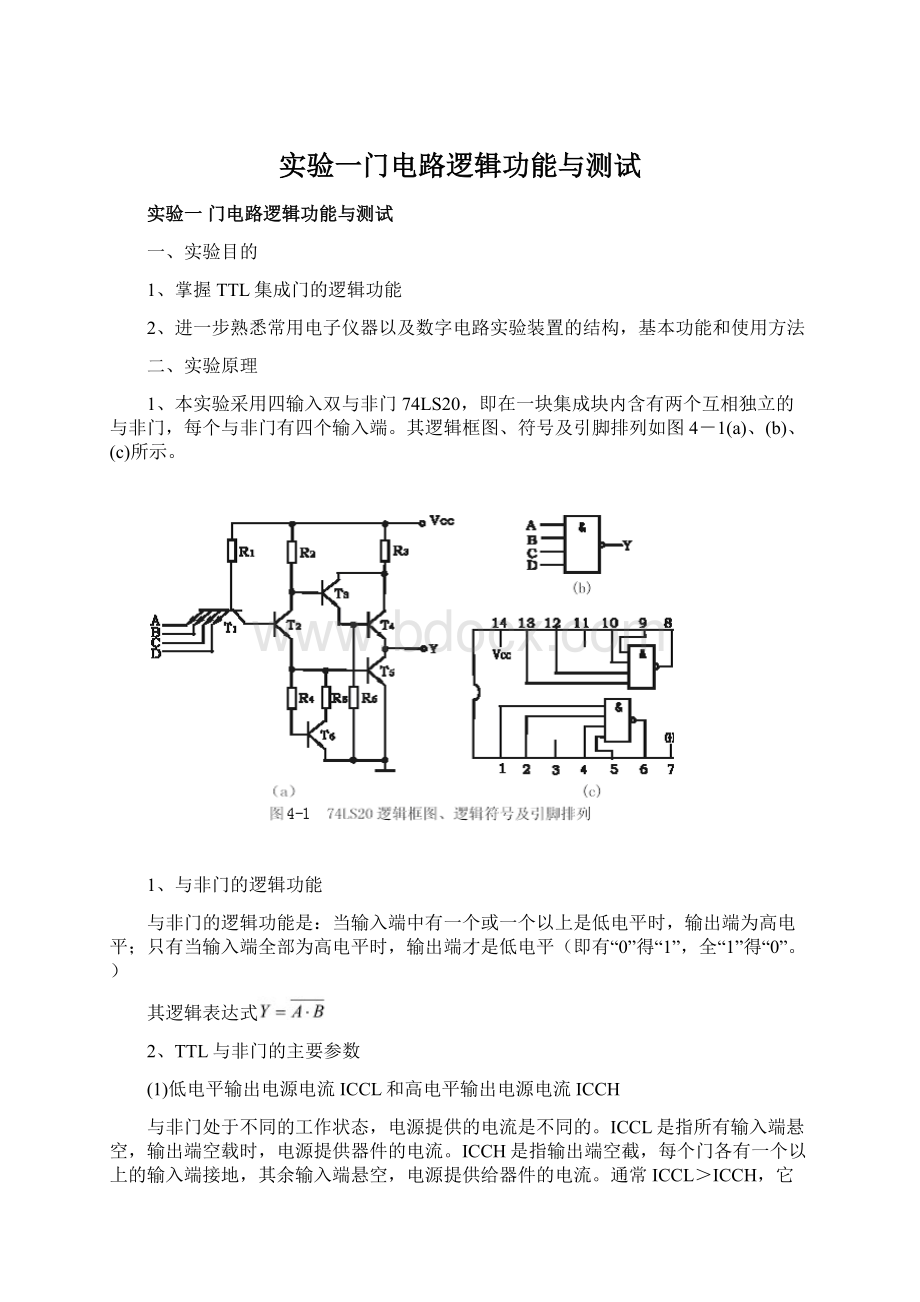

ICCL和ICCH测试电路如图4-2(a)、(b)所示。

[注意]:

TTL电路对电源电压要求较严,电源电压VCC只允许在+5V±

10%的范围内工作,超过5.5V将损坏器件;

低于4.5V器件的逻辑功能将不正常。

(2)低电平输入电流IiL和高电平输入电流IiH。

IiL是指被测输入端接地,其余输入端悬空,输出端空载时,由被测输入端流出的电流值。

在多级门电路中,IiL相当于前级门输出低电平时,后级向前级门灌入的电流,因此它关系到前级门的灌电流负载能力,即直接影响前级门电路带负载的个数,因此希望IiL小些。

IiH是指被测输入端接高电平,其余输入端接地,输出端空载时,流入被测输入端的电流值。

在多级门电路中,它相当于前级门输出高电平时,前级门的拉电流负载,其大小关系到前级门的拉电流负载能力,希望IiH小些。

由于IiH较小,难以测量,一般免于测试。

IiH与IiL的测试电路如图4-2(c)、(d)所示。

(3)扇出系数NO

扇出系数NO是指门电路能驱动同类门的个数,它是衡量门电路负载能力的一个参数,TTL与非门有两种不同性质的负载,即灌电流负载和拉电流负载,因此有两种扇出系数,即低电平扇出系数NOL和高电平扇出系数NOH。

通常IiH<IiL,则NOH>NOL,故常以NOL作为门的扇出系数。

NOL的测试电路如图4-3所示,门的输入端全部悬空,输出端接灌电流负载RL,调节RL使IOL增大,VOL随之增高,当VOL达到VOLm(手册中规定低电平规范值0.4V)时的IOL就是允许灌入的最大负载电流,则

通常

4)电压传输特性

门的输出电压vO随输入电压vi而变化的曲线vo=f(vi)称为门的电压传输特性,通过它可读得门电路的一些重要参数,如输出高电平VOH、输出低电平VOL、关门电平VOff、开门电平VON、阈值电平VT及抗干扰容限VNL、VNH等值。

测试电路如图4-4所示,采用逐点测试法,即调节RW,逐点测得Vi及VO,然后绘成曲线。

(5)平均传输延迟时间

是衡量门电路开关速度的参数,它是指输出波形边沿的0.5Vm至输入波形对应边沿0.5Vm点的时间间隔,如图4-5所示。

图4-5(a)中的tpdL为导通延迟时间,tpdH为截止延迟时间,平均传输延迟时间为

tpd的测试电路如图7-5(b)所示,由于TTL门电路的延迟时间较小,直接测量时对信号发生器和示波器的性能要求较高,故实验采用测量由奇数个与非门组成的环形振荡器的振荡周期T来求得。

其工作原理是:

假设电路在接通电源后某一瞬间,电路中的A点为逻辑“1”,经过三级门的延迟后,使A点由原来的逻辑“1”变为逻辑“0”;

再经过三级门的延迟后,A点电平又重新回到逻辑“1”。

电路中其它各点电平也跟随变化。

说明使A点发生一个周期的振荡,必须经过6级门的延迟时间。

因此平均传输延迟时间为

TTL电路的一般在10nS~40nS之间。

74LS20主要电参数规范如表7-1所示

三、实验设备与器件

1、数字电路实验箱2、数字万用表

四、实验内容

在合适的位置选取一个14P插座,按定位标记插好74LS20集成块。

1、验证TTL集成与非门74LS20的逻辑功能

按图7-6接线,门的四个输入端接逻辑开关输出插口,以提供“0”与

“1”电平信号,开关向上,输出逻辑“1”,向下为逻辑“0”。

门的输出端接由LED发光二极管组成的逻辑电平显示器(又称0-1指示器)的显示插口,LED亮为逻辑“1”,不亮为逻辑“0”。

按表2-2的真值表逐个测试集成块中两个与非门的逻辑功能。

74LS20有4个输入端,有16个最小项,在实际测试时,只要通过对输入1111、0111、1011、1101、1110五项进行检测就可判断其逻辑功能是否正常。

输入

输出

表7-2

2、74LS20主要参数的测试

(1)分别按图7-2、7-3、7-5(b)接线并进行测试,将测试结果记入表7-3中。

表7-3

(ns)

(2)接图7-4接线,调节电位器RW,使vi从OV向高电平变化,逐点测量vi和vO的对应值,记入表7-4中。

五、实验报告

1、记录、整理实验结果,并对结果进行分析。

2、画出实测的电压传输特性曲线,并从中读出各有关参数值。

六、集成电路芯片简介

数字电路实验中所用到的集成芯片都是双列直插式的,其引脚排列规则如图7-1所示。

识别方法是:

正对集成电路型号(如74LS20)或看标记(左边的缺口或小圆点标记),从左下角开始按逆时针方向以1,2,3,.依次排列到最后一脚(在左上角)。

在标准形TTL集成电路中,电源端VCC一般排在左上端,接地端GND一般排在右下端。

如74LS20为14脚芯片,14脚为VCC,7脚为GND。

若集成芯片引脚上的功能标号为NC,则表示该引脚为空脚,与内部电路不连接。

七、TTL集成电路使用规则

1、接插集成块时,要认清定位标记,不得插反。

2、电源电压使用范围为+4.5V~+5.5V之间,实验中要求使用Vcc=+5V。

电源极性绝对不允许接错。

3、闲置输入端处理方法

(1)悬空,相当于正逻辑“1”,对于一般小规模集成电路的数据输入端,实验时允许悬空处理。

但易受外界干扰,导致电路的逻辑功能不正常。

因此,对于接有长线的输入端,中规模以上的集成电路和使用集成电路较多的复杂电路,所有控制输入端必须按逻辑要求接入电路,不允许悬空。

(2)直接接电源电压VCC(也可以串入一只1~10KΩ的固定电阻)或接至某一固定电压(+2.4≤V≤4.5V)的电源上,或与输入端为接地的多余与非门的输出端相接。

(3)若前级驱动能力允许,可以与使用的输入端并联。

4、输入端通过电阻接地,电阻值的大小将直接影响电路所处的状态。

当R≤680Ω时,输入端相当于逻辑“0”;

当R≥4.7KΩ时,输入端相当于逻辑“1”。

对于不同系列的器件,要求的阻值不同。

5、输出端不允许并联使用(集电极开路门(OC)和三态输出门电路(3S)除外)。

否则不仅会使电路逻辑功能混乱,并会导致器件损坏。

6、输出端不允许直接接地或直接接+5V电源,否则将损坏器件,有时为了使后级电路获得较高的输出电平,允许输出端通过电阻R接至Vcc,R=3~5.1KΩ。

实验二组合逻辑电路

一、实验目的

1、学会组合逻辑电路的实验分析方法。

2、验证半加器、全加器的逻辑功能。

二、实验仪器及设备

1、数字逻辑实验箱

2、万用表

3、元器件:

74LS00、74LS20各一块、74LS54、74LS86各一、电阻及导线若干

三、实验线路图

四、实验内容

1、测试用与非门构成的电路的逻辑功能

按图3-1接线。

按下表要求输入信号,测出相应的输出逻辑电平,并填入表中。

分析电路的逻辑功能为半加器,写出逻辑表达式为:

Y=A⊕BZ=AB

2、测试用异或门和与非门组成的电路的逻辑功能

按图3-2接线。

分析电路的逻辑功能为半加器,写出逻辑表达式为

3、测试用异或门、非门和与或非门组成的电路的逻辑功能

按图3-3接线。

五、实验结果分析(回答问题)

1、总结用实验来分析组合逻辑电路功能的方法为:

按图接线,将输入的所有取值组合对应输出测出来,得到该电路的真值表,进而写出逻辑函数表达式,概述电路的逻辑功能

实验三触发器

一、实验目的

1.学会测试触发器逻辑功能的方法。

2.进一步熟悉RS触发器、集成JK触发器和D触发器的逻辑功能及触发方式。

3.熟悉数字逻辑实验箱中单脉冲和连续脉冲发生器的使用方法。

参看附录一。

二、实验器材

1.数字逻辑实验箱DSB-31台

2.万用表1只

3.二踪示波器XJ43281台

4.元器件:

74LS00(T065)1块74LS741块

74LS761块导线若干

三、实验说明

1.如何用二踪示波器XJ4328按时间对应关系同时显示两个信号?

请预习附录二相关内容。

2.74系列产品抗干扰能力很差,不用的输入控制端不可悬空,要接固定高电平。

可通过一个几KΩ电阻接5V电源,也可利用实验箱上的逻辑电平开关。

四、实验内容和步骤

1.基本RS触发器逻辑功能测试

利用数字逻辑实验箱测试由与非门组成的基本RS触发器的逻辑功能,将测试结果记录在表7-1中。

2.集成JK触发器74LS76逻辑功能测试

(1)直接置0和置1端的功能测试

(2)JK触发器逻辑功能的测试

按表7-3测试并记录JK触发器的逻辑功能(表中CP信号由实验箱操作板上的单次脉冲发生器P+提供,手按下产生0→1,手松开产生1→0)。

(3)JK触发器计数功能测试

使触发器处于计数状态(J=K=1),

CP信号由实验箱操作板中的连续脉冲(矩形波)发生器提供,可分别用低频(f=1~10HZ)和高频(f=20~150KHZ)两档进行输入,同时用实验箱上的LED电平显示器和XJ4328型二踪示波器观察工作情况,记入表7-4。

高频输入时,记录CP与Q的工作波形,并回答:

Q状态更新发生在CP的哪个边沿?

Q和CP信号的周期有何关系?

若R=0会怎样?

3.集成D触发器74LS74逻辑功能测试

(1)D触发器逻辑功能的测试

按表7-5测试并记录D触发器的逻辑功能(表中CP信号由实验箱操作板上的单次脉冲发生器P+提供)。

(2)D触发器计数功能测试

使触发器处于计数状态(D=

),

CP端由实验箱操作板中的连续脉冲(矩形波)发生器提供,可分别用低频(f=1~10HZ)和高频(f=20~150KHZ)两档进行输入,分别用实验箱上的LED电平显示器和SR8双踪示波器观察工作情况,记录CP与Q的工作波形,并回答:

若

会怎样?

四、实验报告要求

1.画出实验测试电路,整理实验测试结果,列表说明,回答所提问题,画出工作波形图。

2.比较各种触发器的逻辑功能及触发方式。

3.回答思考题

1)一个带直接置0/1端的JK触发器置为0或1有哪几种方法?

2)一个带直接置0/1端的D触发器置为0或1有哪几种方法

实验四MSI计数器的应用

1.熟悉中规模集成电路计数器的功能及应用。

2.进一步熟悉数字逻辑实验箱中的译码显示功能。

(参看附录1)

3.元器件:

74LS00(T065)一块

74LS20(T063)一块

74LS161一块

导线若干

三、实验内容和步骤

用74LS161及辅助门电路实现一个2~N~16任意进制计数器:

以N=10为例,请在预习时分别设计相应电路,自行拟出实验步骤。

分别安装并观察计数器的功能。

1.列出表述其功能的计数状态顺序表(参考表9-1的格式),记录实验数据。

可利用实验箱上的低频连续脉冲作CP,LED译码显示电路指示输出状态。

2.利用实验箱上的高频连续脉冲作CP,用示波器观察QD、QC、QB、QA的波形,并按时间对应关系记录下来。

1.整理实验测试结果,以N=10为例,分别画出电路图,列出计数状态顺序表,画出工作波形。

2.回答思考题

1)74LS161的置0端和置数端的工作情况有何不同?

2)若要求计数器具有暂时停止计数、过一段时间再继续计数的功能,有哪几种方法可以实现?

实验五电子秒表综合实验

一、实验目的

1.熟悉中规模集成电路计数器的功能及应用。

2.熟悉中规模集成电路译码器的功能及应用。

3.熟悉LED数码管及其驱动电路的工作原理。

4.熟悉集成555定时器组成的多谐振荡器

5.初步学会综合安装调试的方法。

名称

数量

NE555P

1

51k电阻

22K可调电位器

10k电阻

10uf电容

0.01uf电容(103)

74LS20四输入与非门

74LS21四输入与门

74LS162十进制计数器同步清零

3

74LS247译码器

WLGD5011数码管

0.3K电阻

21

导线

三、实验内容和步骤

1.熟悉集成555定时器功能并组成多谐振荡器,用示波器观测输出波形。

2.用162设计60进制计数器

3.连接译码器和显示器

4.参考电路见下图:

1.画出60进制计数、译码、显示的逻辑电路图。

2.说明实验步骤。

3.简要说明数码管自动计数显示的情况。

(可列省略中间某些计数状态的计数状态顺序表说明)

4.根据实验中的体会,说明综合安装调试较复杂中小规模数字集成电路的方法。

5.回答思考题

1)阴、共阳LED数码管应分别配用何种输出方式的译码器?

2)该如何确定数码管驱动电路中的限流电阻值?

3)如果60进制计数器采用高位接10进制、低位接6进制的方式,计数顺序又如何?

可列省略中间某些状态的计数状态顺序表说明。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 实验 门电路 逻辑 功能 测试

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx