分频器Word格式文档下载.docx

分频器Word格式文档下载.docx

- 文档编号:19533970

- 上传时间:2023-01-07

- 格式:DOCX

- 页数:17

- 大小:125.24KB

分频器Word格式文档下载.docx

《分频器Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《分频器Word格式文档下载.docx(17页珍藏版)》请在冰豆网上搜索。

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

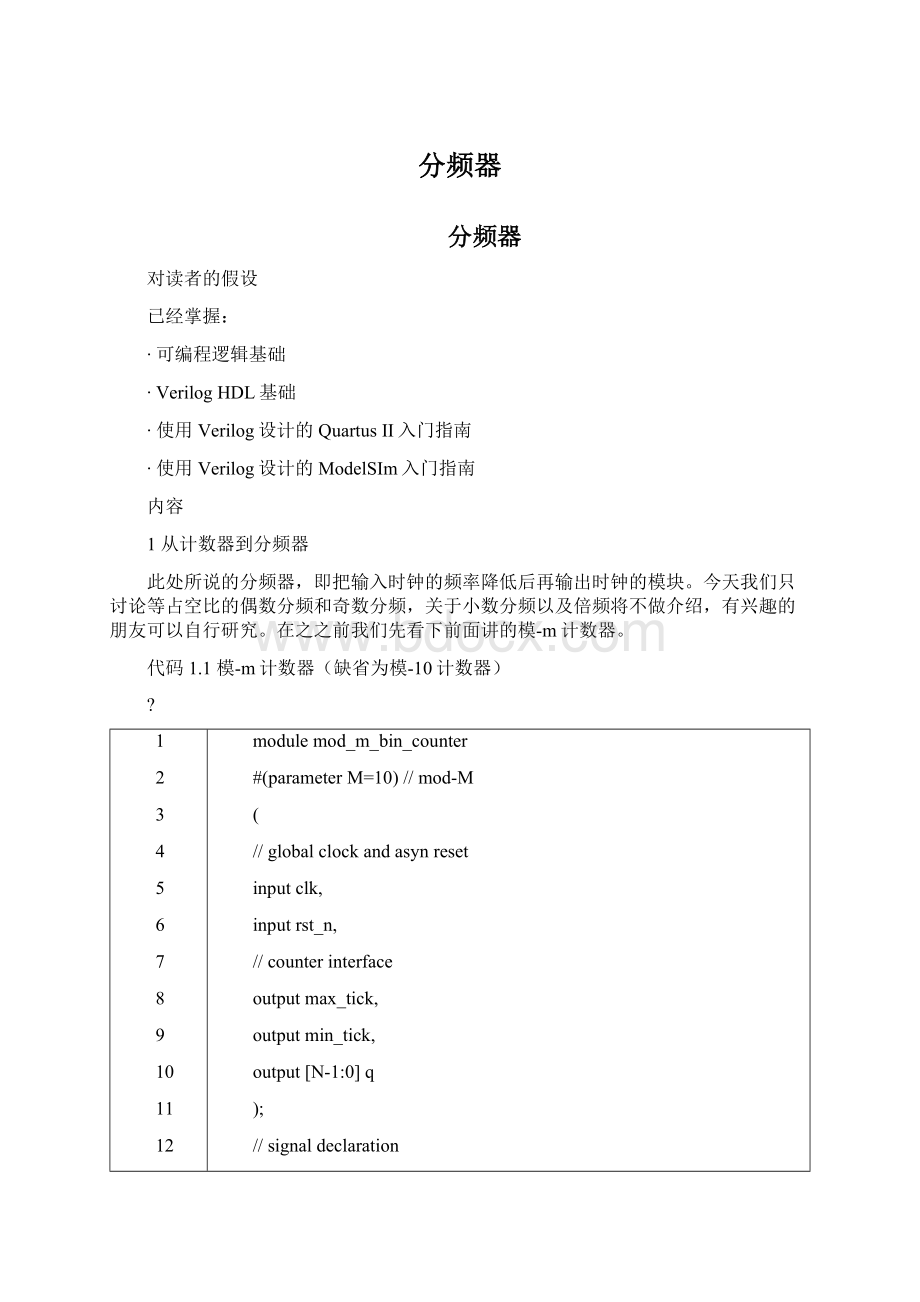

modulemod_m_bin_counter

#(parameterM=10)//mod-M

(

//globalclockandasynreset

inputclk,

inputrst_n,

//counterinterface

outputmax_tick,

outputmin_tick,

output[N-1:

0]q

);

//signaldeclaration

localparamN=log2(M);

//numberofbitsincounter

reg[N-1:

0]r_reg;

wire[N-1:

0]r_next;

//body

//register

always@(posedgeclk,negedgerst_n)

if(!

rst_n)

r_reg<

=0;

else

=r_next;

//next-statelogic

assignr_next=(r_reg==(M-1))?

0:

r_reg+1'

b1;

//outputlogic

assignq=r_reg;

assignmax_tick=(r_reg==(M-1))?

1'

b1:

b0;

//log2constantfunction

functionintegerlog2(inputintegern);

integeri;

begin

log2=1;

for(i=0;

2**i<

n;

i=i+1)

log2=i+1;

end

endfunction

endmodule

根据这个模-m计数器,我们再写一个testbench。

代码1.2模m-计数器的testbench(重新配置为模-10计数器)

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

`timescale1ns/1ns

modulef_div_tb;

localparamT=20;

//clockperiod

localparamM=10;

regclk,rst_n;

wireo_clk;

wiremax_tick,min_tick;

0]q;

endfunction

//clcok

always

clk=1'

#(T/2);

//reset

initial

rst_n=1'

#(T/2)

//inst

mod_m_bin_counter#(.M(M))m_inst

.clk(clk),

.rst_n(rst_n),

.max_tick(max_tick),

.min_tick(min_tick),

.q(q)

//stimulusbody

//initialinput

@(posedgerst_n);

//waittodeassertrst_n

@(negedgeclk);

//waitforaclock

//run1024cockcycle

repeat(1024)@(negedgeclk);

//last1024clockcycle

$stop;

但是我在使用QuartusII+Modelsim_Altera仿真的时候出现了下面的错误提示。

代码2的第10行,变量N未定义,然后第11行用N来索引的q数组也没有定义。

奇怪了,我在QuartusII都能综合通过,而且RTL视图也是正确的,为什么Modelsim_Altera就不可以这样定义呢?

咳,把常量(localparam)换成参数(parameter)即可。

代码1.3改进后的模-m计数器(重新配置为模-10计数器)

#(parameterM=10,N=log2(M))//mod-M

//localparamN=log2(M);

assignmin_tick=(r_reg==0)?

修改完,在QuartusII里再综合一下。

接下来就是按照[文档].艾米电子-使用Verilog设计的QuartusII入门指南再做一次仿真。

告诉大家一个技巧,如果执行完一次RTL级或门级的仿真,那么QuartusII会为我们的主模块及其testbench生成do文件的。

这样假如有错误,就无需重新启动Modelsim_Altera,只需重新load一下do文件即可。

(路径格式:

QuarterII工程文件夹\simulation\modelsim\mod_m_bin_counter_run_msim_rtl_verilog.do)

下面看下RTL级仿真波形。

下面讨论一下如何测量波形的长度,我们注意两个工具。

在Modelsim>

Windows处,打开

,对应的工具为

。

下面在波形上加(

)几个Cursor,使用鼠标调整其位置。

注意红色区域及标识,我们可以清楚地看到两个Cursor之间的距离为20,000ps,亦即20ns,也就是模-10计数器的周期。

那么怎么让它显示20ns呢?

在坐标轴区域(

),右键选择

,设置所需时间单元。

修改为ns,顺便测一下max_tick和min_tick脉冲的持续时间,显示如下:

测量完,可通过

,把不需要的Cursor去掉。

换一种视角看波形。

假设我们以max_tick作为使能信号,来翻转某个寄存器,那么这个变量就会输出方波,且其周期为模-m周期的2倍。

这就是偶数分频器的原理。

假如我们分别使用全局时钟的上升沿和下降沿触发计数器,然后根据两个计数器的值来生成时钟,再拿这两个时钟运算,得到所需分频的时钟。

下面以模-3计数器为例来说明如何3分频。

方法1

黄色区域分别为分别使用全局时钟的上升沿和下降沿触发计数器;

绿色区域为根据两个计数器的输出q生成的两个脉冲信号;

青色区域为所需分频时钟。

绿色区域是0~3>

>

1输出低电平,3>

~3-1输出高电平;

对应的绿色区域做按位或运算。

方法2

1输出高电平,3>

~3-1输出低电平;

对应的绿色区域做按位与运算。

以上就是技术分频的原理。

2偶数分频器

根据第1节的解析,下面我们写一个偶数分频的案例。

代码2.1偶数分频(缺省分频比为50,000,000)

modulef_div

#(parameterRATIO=50_000_000)

//outputclock

outputrego_clk

wiremax_tick;

mod_m_bin_counter#(.M(RATIO/2))mod_m_inst

.min_tick(),

.q()

o_clk<

=1'

elseif(max_tick)

=~o_clk;

第22~26行,我们使用模-m计数器的max_tick来作为时钟使能,驱动o_clk翻转。

注意第13行的模-m例化参数中,M的值为分频比RATIO的一半。

下面给出testbench。

代码2.2偶数分频的testbench(重新配置为6分频)

localparamRATIO=6;

f_div#(.RATIO(RATIO))f_div_inst

.o_clk(o_clk)

RTL级仿真波形如下所示。

观察3个Cursor的间距,分别为120ns、20ns,即实现了6分频动作。

3奇数分频器

讲完了偶数分频,下面再写个奇数分频。

代码3.1奇数分频(缺省为25分频)

#(parameterRATIO=25)

outputo_clk_p,o_clk_n,o_clk

localparamN=log2(RATIO);

0]q_pos,q_neg;

mod_m_bin_counter#(.M(RATIO))mod_m_inst1

.max_tick(),

.q(q_pos)

mod_m_bin_counter#(.M(RATIO))mod_m_inst2

.clk(~clk),

.q(q_neg)

assigno_clk_p=(q_pos<

=RATIO>

1)?

1;

assigno_clk_n=(q_neg<

assigno_clk=o_clk_n|o_clk_p;

第24~31行和第33~40行,我们分别例化了两个相同参数的模-m计数器,不同点在于第26行和第35行的区别,即上升沿触发和下降沿触发两种。

代码3.2奇数分频的testbench(重新配置为5分频)

localparamRATIO=5;

wireo_clk_p,o_clk_n,o_clk;

.o_clk_p(o_clk_p),

.o_clk_n(o_clk_n),

下面给出RTL级别仿真波形。

红圈内的Cursor测距显示,5分频OK。

好了,今天就啰嗦到这里,大家有什么疑问可以留言讨论。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 分频器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx