SOC复习资料Word格式文档下载.docx

SOC复习资料Word格式文档下载.docx

- 文档编号:19531013

- 上传时间:2023-01-07

- 格式:DOCX

- 页数:33

- 大小:192.18KB

SOC复习资料Word格式文档下载.docx

《SOC复习资料Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《SOC复习资料Word格式文档下载.docx(33页珍藏版)》请在冰豆网上搜索。

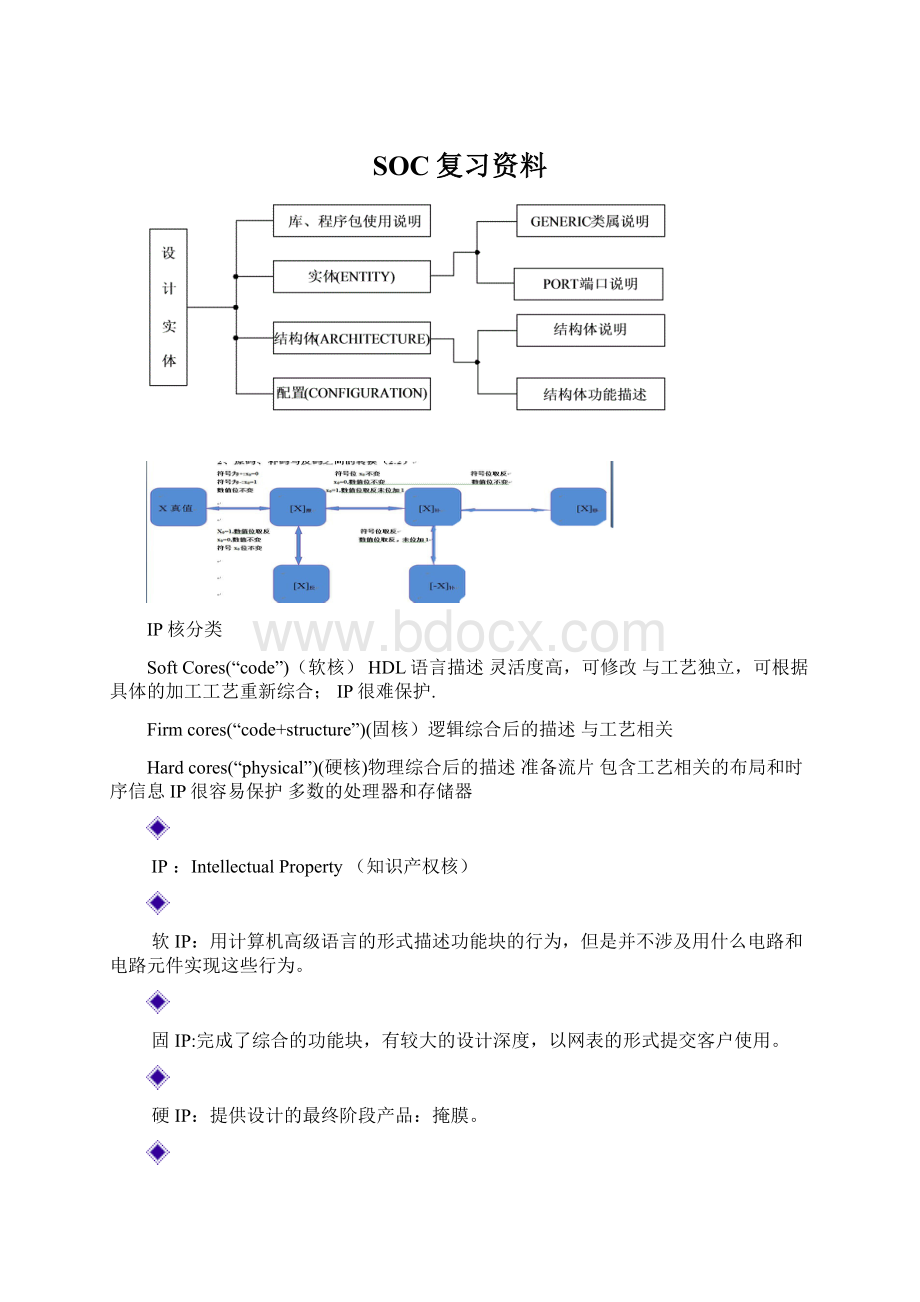

RTL(RegesistTransformLeval)描述,即寄存器传输级描述,有的文献称为数据流描述;

结构化描述是常用的层次化设计方法。

●写出下列缩写的中、英文含义

¡

ASIC专用集成电路

HDL硬件描述语言

SOPC可编程单片系统

RTL寄存器传输级

JTAG联合测试行动小组

PCB印刷电路板

FSM有限状态机

IP知识产权核(软件包)

FPGA现场可编程门阵列

CPLD复杂可编程逻辑器件

PLA可编程逻辑阵列

GAT通用阵列逻辑

HDPLD高密度可编程逻辑器件

ISP系统可编程

●比较下列数字,找出数值最小的一个(10#170#)

2#1111_1110#16#E#E1

8#276#10#170#

⏹HDL语言是一种结构化设计语言;

一个设计实体(电路模块)包括实体与结构体两部分,结构体描述(D)。

A.器件外部特性

B.器件的综合约束

C.器件外部特性与内部功能

D.器件的内部功能

⏹在一个VHDL设计中idata是一个信号,数据类型为integer,下面哪个赋值语句是不正确的(D)。

A.idata<

=16#20#

B.idata<

=32

C.idata<

=16#A#E1

D.idata<

=B#1010#

FPGA的可编程是主要基于什么结构(A)。

A.查找表(LUT)

B.ROM可编程

C.PAL可编程

D.与或阵列可编程

VHDL语言共支持四种常用库,其中哪种库是用户的VHDL设计现行工作库(D)

A.IEEE库

B.VITAL库

C.STD库

D.WORK工作库

以下对于进程PROCESS的说法,正确的是(C)

A.进程之间可以通过变量进行通信

B.进程内部由一组并行语句来描述进程功能

C.进程语句本身是并行语句

下面对利用原理图输入设计方法进行数字电路系统设计,哪一种说法是正确(A)

A.原理图输入设计方法直观便捷,很适合完成较大规模的电路系统设计

B.原理图输入设计方法一般是一种自底向上的设计方法

C.原理图输入设计方法无法对电路进行功能描述

D.原理图输入设计方法不适合进行层次化设计

在VHDL语言中,下列对时钟边沿检测描述中哪一个是错误的。

(B)

A.ifclk'

eventandclk='

1'

then

B.ifclk'

stableandnotclk='

then

C.ifrising_edge(clk)then

D.ifnotclk'

stableandclk='

进程中的变量赋值语句,其变量更新是(A)

A.立即完成

B.按顺序完成

C.在进程的最后完成

(多选)

对于信号和变量的说法,哪些是正确的。

(BCD)

A.信号用于作为进程中局部数据存储单元

B.变量的赋值是立即完成的

C.信号在整个结构体内的任何地方都能适用

D.变量和信号的赋值符号不一样

下列语句中,属于并行语句的是:

(ABC)

A.进程语句

B.WHEN…ELSE…语句

C.元件例化语句

D.CASE语句

在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,正确的是:

(ABC)

A.PROCESS为一无限循环语句

B.敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动

C.当前进程中声明的变量不可用于其他进程

D.进程由说明语句部分、并行语句部分和敏感信号参数表三部分组成

10#170#--(十进制数表示,等于170)

2#1111_1110#--(二进制数表示,等于254)

16#E#E1--(十六进制数表示,等于2#11100000#,等于224)

16#F.01#E+2--(十六进制数表示,等于3841.00)

请判断下面的标识符是否合法:

_DECODER_1,2FFT,SIG_#N,Not-Ack,RYY_RST_,data__BUS,RETURN

_Decoder_1--起始为非英文字母

2FFT--起始为数字

Sig_#N--符号“#”不能成为标识符的构成

Not-Ack--符号“-”不能成为标识符的构成

RyY_RST_--标识符的最后不能是下划线“_”

data__BUS--标识符中不能有双下划线

return--关键词

判断下面3个程序中是否有错误,若有则指出错误所在。

程序1:

程序2:

SignalA,EN:

std_logic;

Architectureoneofsampleis

Process(A,EN)variablea,b,c:

integer;

VariableB:

begin

Beginc<

=a+b;

ifEN=1thenB<

=A;

endif;

end;

endprocess;

程序3:

libraryieee;

useieee.std_logic_1164.all;

entitymux21is

port(a,b:

instd_logic;

sel:

c:

outstd_logic;

);

endsam2;

architectureoneofmux21is

begin

ifsel='

0'

thenc:

=a;

elsec:

=b;

endif;

endtwo;

答案:

程序1:

Process(A,EN)

VariableB:

Begin

ifEN='

thenB:

endprocess;

程序2:

architectureoneofsampleis

begin

process

variablea,b,c:

c:

endone;

instd_logic;

outstd_logic);

endmux21;

process(a,b,sel)

begin

ifsel='

thenc<

elsec<

endif;

●1.分别用case语句和IF语句设计四选一电路?

●用IF语句设计四选一电路

●LIBRARYIEEE;

●USEIEEE.STD_LOGIC_1164.ALL;

●ENTITYmux4IS

●PORT(a,b,d0,d1,d2,d3:

INSTD_LOGIC;

●q:

OUTSTD_LOGIC);

●ENDmux4;

●ARCHITECTUREexample_ifOFmux4IS

●BEGIN

●PROCESS(a,b,d0,d1,d2,d3)

●IF(a=‘0’ANDb=‘0’)THEN

●q<

=d0;

●ELSIF(a=‘1’ANDb=‘0’)THE

=d1;

●ELSIF(a=‘0’ANDb=‘1’)THEN

=d2;

●ELSIF(a=‘1’ANDb=‘1’)THEN

=d3;

●ENDIF;

●ENDPROCESS;

●ENDexample_if;

●用CASE语句设计四选一电路

●PORT(a,b,d0,d1,d2,d3:

INSTD_LOGIC;

q:

OUTSTD_LOGIC);

●ARCHITECTUREexample_caseOFmux4IS

●SIGNALsel:

INTEGERRANGE0TO3;

●PROCESS(a,b,d0,d1,d2,d3)

●BEGIN

●sel<

=’0’;

●IF(a=’1’)THEN

=sel+1;

●ENDIF;

●IF(b=’1’)THEN

●sel<

=sel+2;

●CASEselIS

●WHEN0=>

q<

=d0;

●WHEN1=>

=d1;

●WHEN2=>

=d2;

●WHEN3=>

=d3;

●ENDCASE;

●ENDexample_case;

●2.将下列程序改写为WHEN_ELSE语句实现的程序段

PROCESS(a,b,c,d)

BEGIN

IFa=‘0’ANDB=‘1’THENnext1<

=“1101”;

ELSIFa=‘0’THENnext1<

=d;

ELSIFB=‘1’THENnext1<

=c;

ENDIF;

ENDPROCESS;

修改:

PROCESS(a,b,c,d)

Next1<

=”1101”WHENa=‘0’ANDB=‘1’ELSE

DWHENa=‘0’ELSE

CWHENB=‘1’;

●5.比较CASE语句与WITH_SELECT语句,叙述它们的异同点。

以下程序是一个BCD码表示0~89计数器的VHDL描述,试补充完整。

libraryIEEE;

useIEEE.std_logic_unsigned.all;

entitycnt90bis

port(clk,rst,en:

cq:

outstd_logic_vector(7downto0);

--计数输出

cout:

--进位输出

endentitycnt90b;

ARCHITECTUREbhvofcnt90bis

process(clk,rst,en)

variablecqi:

std_logic_vector(7downto0);

ifrst='

cqi:

=(other=>

’0’);

--计数器清零复位

else

ifclk’eventandclk=’1’then--上升沿判断

ifen='

ifcqi(3downto0)<

"

1001"

then--比较低4位

cqi:

=cqi+1;

--计数加1

else

ifcqi(7downto4)<

1000"

then--比较高4位

cqi:

=cqi+16;

else

=(others=>

'

endif;

cqi(3downto0):

=’0000’;

--低4位清零

endif;

ifcqi=‘10001001’then--判断进位输出

cout<

='

;

cout<

cp<

=cqi;

endarchitecturebhv;

下面程序是一个16位数控分频器的VHDL描述,试补充完整。

LibraryIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYPULSE16IS

PORT(CLK:

LOAD:

D:

INSTD_LOGIC_VECTOR(15DOWNTO0);

FOUT:

OUTSTD_LOGIC);

END;

ARCHITECTUREoneOFPULSE16IS

SIGNALFULL:

STD_LOGIC;

BEGIN

P_REG:

PROCESS(CLK)

VARIABLECNT16:

STD_LOGIC_VECTOR(15DOWNTO0);

BEGIN

IFCLK'

EVENTANDCLK='

THEN

IFLOAD=’1’THEN--LOAD高电平置数

CNT16:

=D;

FULL<

ELSE

IFCNT16="

1111111111111111"

THEN

CNT16:

ELSE

=CNT16+1;

--计数加1

ENDIF;

ENDPROCESSP_REG;

P_DIV:

PROCESS(FULL’eventandFULL=’1’)--溢出信号为敏感信号

VARIABLECNT2:

IFFULL’EVENTANDFULL=’1’THEN--FULL上升沿判断

CNT2:

=NOTCNT2;

FOUT<

=CNT2;

ENDIF;

ENDPROCESSP_DIV;

下面程序是参数可定制带计数使能异步复位计数器的VHDL描述,试补充完整。

useIEEE.std_logic_1164.all;

useIEEE.Std_logic_unsigned.all;

useIEEE.std_logic_arith.all;

entitycounter_nis

generic(width:

integer:

=8);

port(data:

instd_logic_vector(width-1downto0);

load,en,clk,rst:

instd_logic;

q:

outstd_logic_vector(width-1downto0));

endcounter_n;

architecturebehaveofcounteris

signalcount:

std_logic_vector(width-1downto0);

process(clk,rst)

count<

=‘00000000’;

――清零

――边沿检测

elsifclk’eventandclk=‘1’then

ifload='

=data;

elseifen='

=count+1;

endif;

endprocess;

out<

=count;

endbehave;

⏹试写出下图2选一多路选择器的VHDL程序

图1mux21a实体图2mux21a结构体

ENTITYmux21aIS

PORT(a,b,s:

INBIT;

y:

OUTBIT);

ENDENTITYmux21a;

ARCHITECTUREoneOFmux21aIS

SIGNALd,e:

BIT;

d<

=aAND(NOTS);

e<

=bANDs;

y<

=dORe;

ENDARCHITECTUREone;

ENDENTITYmux21a;

PROCESS(a,b,s)

IFs='

THENy<

=a;

ELSEy<

=b;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREone;

⏹

设计一数据选择器MUX,其系统模块图和功能表如下图所示。

试采用下面三种方式中的两种来描述该数据选择器MUX的结构体。

⏹(a)用if语句。

(b)用case语句。

(c)用whenelse语句。

Entitymymuxis

Port(sel:

instd_logic_vector(1downto0);

--选择信号输入

Ain,Bin:

--数据输入

Cout:

outstd_logic_vector(1downto0));

Endmymux;

用if语句:

Architectureoneofmymuxis

Begin

Process(sel,ain,bin)

Begin

Ifsel=“00”thencout<

=ainorbin;

Elsifsel=“01”thencout<

=ainxorbin;

Elsifsel=“10”thencout<

=ainandbin;

Elsecout<

=ainnorbin;

Endif;

Endprocess;

Endone;

Case语句:

Architecturetwoofmymuxis

Caseselis

when“00”=>

when“01”=>

when“10”=>

whenothers=>

Endcase;

Endtwo;

Whenelse语句:

Architecturethreeofmymuxis

=ainorbinwhensel=“00”else

Ainxorbinwhensel=“01”else

Ainandbinwhensel=“10”elseainnorbin;

Endthree;

写出半加器的VHDL程序

布尔方程描述方法

LIBRARYIEEE;

--半加器描述

(1):

ENTITYh_adderIS

PORT(a,b:

co,so:

ENDENTITYh_adder;

ARCHITECT

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- SOC 复习资料

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx