运算放大器电路的误差分析+汇总Word文档下载推荐.docx

运算放大器电路的误差分析+汇总Word文档下载推荐.docx

- 文档编号:19408406

- 上传时间:2023-01-06

- 格式:DOCX

- 页数:14

- 大小:357.51KB

运算放大器电路的误差分析+汇总Word文档下载推荐.docx

《运算放大器电路的误差分析+汇总Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《运算放大器电路的误差分析+汇总Word文档下载推荐.docx(14页珍藏版)》请在冰豆网上搜索。

BJT集成运放的两个输入端是差分对管的基极,因此两个输入端总需要一定的输入电流IBN和IBP。

输入偏置电流是指集成运放输出电压为0时,两个输入端静态电流的平均值。

输入偏置电流的大小,在电路外接电阻确定之后,主要取决于运放差分输入级BJT的性能,当它的β值太小时,将引起偏置电流增加。

偏置电流越小,由于信号源内阻变化引起的输出电压变化也越小。

其值一般为10nA~1uA。

4.输入失调电流IIO

在BJT集成电路运放中,当输出电压为0时,流入放大器两输入端的静态基极电流之差,即IIO=|IBP-IBN|

由于信号源内阻的存在,IIO会引起一个输入电压,破坏放大器的平衡,使放大器输出电压不为0。

它反映了输入级差分对管的不对称度,一般约为1nA~0.1uA。

5.输入失调电压VIO、输入失调电流IIO不为0时,运算电路的输出端将产生误差电压。

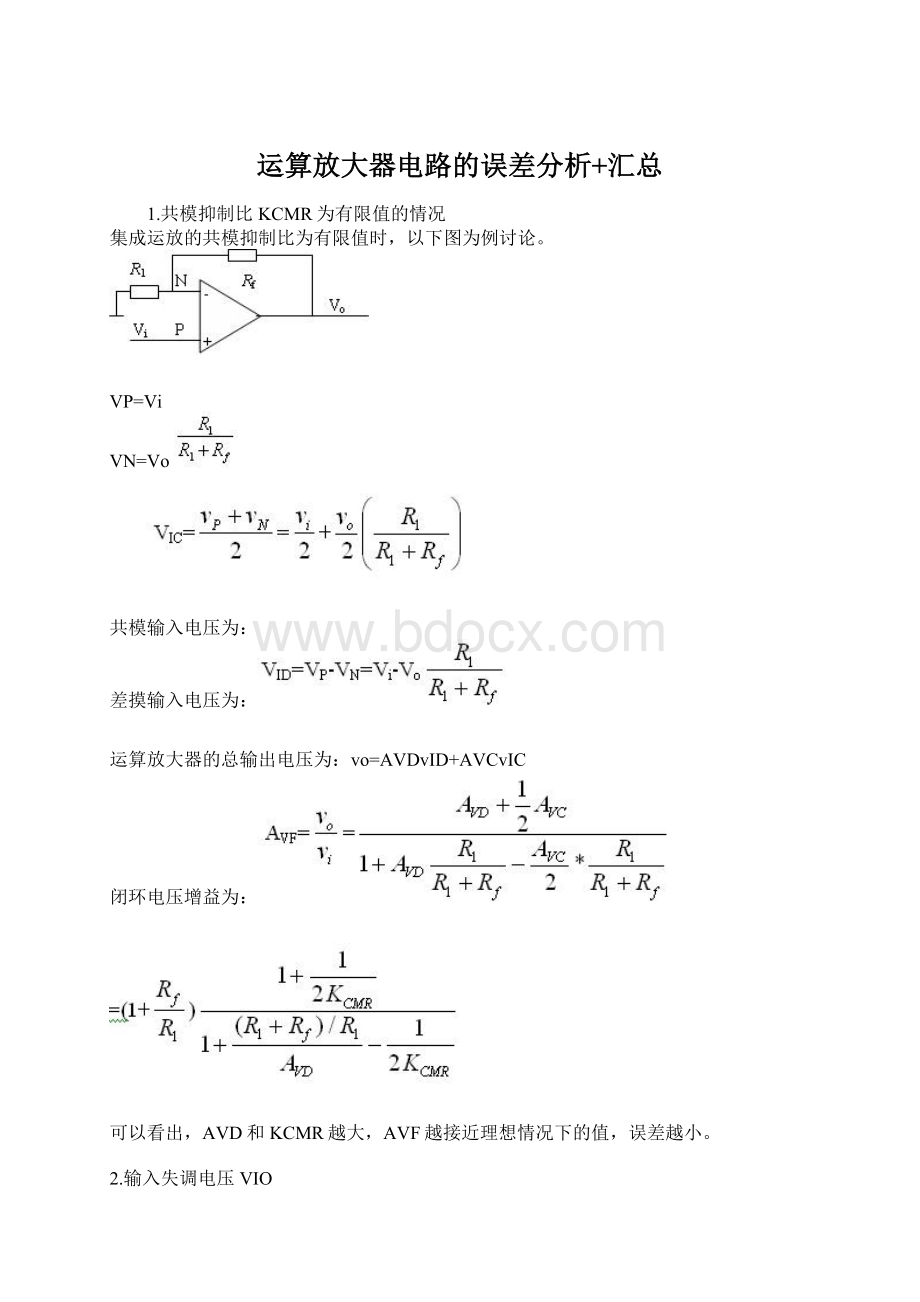

设实际的等效电路如下图大三角符号,小三角符号内为理想运放,根据VIO和IIO的定义画出。

为了分析方便,假设运放的开环增益AVO和输入电阻Ri均为无限大,外电路电阻R2=R1||Rf,利用戴维南定理和诺顿定理可得两输入端的等效电压和等效电阻,如下图所示

则可得同相输入端电压

反向输入端电压

因AVO→∞,有VP≈VN,代入得

Vo=(1+Rf/R1)[VIO+IIB(R1||Rf-R2)+IIO(R1||Rf+R2)]

当取R2=R1||Rf时,由输入偏置电流IIB引起的输入误差电压可以消除,上式可简化为

Vo=(1+Rf/R1)(VIO+IIOR2)

可见,1+Rf/R1和R2越大,VIO和IIO引起的输出误差电压越大。

当用作积分运算时,用1/(sC)代替Rf,输出误差电压为

vo(s)=[1+1/(sCR1)][VIO(s)+IIO(s)R2]

当VIO和IIO随时间变化时,即有

由此式可以看出,积分时间常数τ=R1C越小或积分时间越长,VIO和IIO引起的输出误差电压越大。

在理想情况下,VIO和IIO都为0时,输出误差电压也为0。

可以在输入级加一调零电位器,或在输入端加一补偿电压或补偿电流,以抵消VIO和IIO的影响。

问题分析:

实施电压测量时,一般要求测量仪器(电压表)的内阻要远高于被测电路检测点的阻抗,这样才能得到比较准确的测量结果。

运算放大器具有极高的输入阻抗和电压增益,其输入端信号极其微弱。

通常与输入端相连接的电阻阻值都很大(102—103KΩ),这个阻值已经和模拟式电压表的内阻在同一个数量级,电压表的接入显然会改变电路的工作状态,即使是数字式电压表(内阻MΩ级),也无法在如此高的阻抗下准确测量。

测量方法:

测量运算放大器电路的静态工作点,一般都避免直接测输入端,只测量输出端直流电压,由输出端电压可推算出输入端电压,

推算方法如下:

工作于线性模式(有反馈电阻Rf)时,输出端静态电位与两个输入端静态电位相等,即:

Vo=V+=V-;

工作于非线性模式(无反馈电阻Rf)时,输出电压只有两个离散值(高电位Vh和地电位Vl):

当V+>V-时,Vo=Vh;

当V+<V-时,Vo=Vl,其中Vh的数值接近正电源供电电压Vcc,Vl接近负电源供电电压Vdd(单电源供电时为零电位),具体数值因运算放大器型号不同略有区别。

单电源运算放大器的偏置与去耦电路设计

目前在许多手持设备、汽车以及计算机等设备只用单电源供电,但是单电源容易出现不稳定问题,因此需要在电路外围增加辅助器件以提高稳定性。

在电路图1中展示了单电源供电运算放大器的偏置方法,用电阻RA与电阻RB构成分压电路,并把正输入端的电压设置为Vs/2。

输入信号VIN是通过电容耦合到正输入端。

在该电路中有一些严重的局限性。

首先,电路的电源抑制几乎没有,电源电压的任何变化都将直接通过两个分压电阻改变偏置电压Vs/2,但电源抑制的能力是电路非常重要的特性。

例如此电路的电源电压1伏的变化,能引起偏置电路电压的输出Vs/2变化0.5伏。

该电路的电源抑制仅仅只有6dB,通过选用SGM8541运算放大器可以增强电源抑制能力。

图1:

单电源供电运算放大器的偏置方法。

其次,运算放大器驱动大电流负载时电源经常不稳定,除非电源有很好的调节能力,或有很好的旁路,否则大的电压波动将回馈到电源线路上。

运算放大器的正输入端的参考点将直接偏离Vs/2,这些信号将直接流入放大器的正输入端。

表1:

适用于图2的典型器件值。

在应用中要特别注意布局,多个电源旁路电容、星形接地、单独的印制电源层可以提供比较稳定的电路。

偏置电路的去耦问题

解答这个问题需要改变一下电路。

图2从偏置电路的中间节点接电容C2,用来旁路AC信号,这样可以提高AC的电源抑制,电阻RIN为Vs/2的基准电压提供DC的返回通路,并且为AC输入提供了交流输入阻抗。

图2:

接电容C2来旁路AC信号,提高AC的电源抑制。

这个偏置电路的-3dB带宽是通过电阻RA、RB与电容C2构成的并且等于

此偏置电路当频率在30Hz以内时,没有电源抑制的能力,因此任何在电源线上低于30Hz的信号,能够轻易地加到放大器的输入端。

一个通常解决这个问题的方法是增加电容值C2,它的值需要足够的大,以便能有效地旁路掉偏置电路通频带以内的全部噪声。

然而在这里比较合理的方法是,设置C2与偏置电路连接点的带宽是十分之一的信号输入带宽,参见图2。

表2:

电路图3和4的一些齐纳二极管与Rz电阻值的关系

在有些运算放大器中输入偏置电流比较大是需要考虑的,由于放大器偏置电流的影响,偏置分压电路的分压点将偏离Vs/2,影响了放大器的静态工作点。

为了使放大器的静态工作点尽量靠近Vs/2,需要增加平衡电阻,见电路图2。

在这个电路中运算放大器选用的是SGM8541,该放大器的输入偏置电流在常温下只有1-2个皮安,几乎为零,因此可以不考虑输入偏置电流带来的误差。

但如果工作在非常宽的温度范围(-20℃-80℃),在放大器的正负输入端加平衡电阻能很好地阻止输入带来的误差。

图3:

齐纳二级管偏置电路。

设计单电源运算放大器电路,需要考虑输入偏置电流误差、电源抑制、增益、以及输入与输出线路带宽等等。

然而普通的应用设计是可以通过查表来获得,见表1。

在单电源电压为15V或12V时偏置分压的两个电阻通常选用100kΩ,这样可以在电源消耗与输入偏置电流误差之间合理的折中。

5V单电源偏置分压电阻减小到一个比较低的值,例如42kΩ。

还有些在3.3V应用中偏置分压电阻选在27kΩ左右。

齐纳二级管偏置电路

表3:

电路参数及期间参数选择。

虽然电阻偏置电路技术成本很低,并且始终能保持运放输出控制在Vs/2,但运放的共模抑制能力完全依靠RA/RB与C2构成的RC时间常数。

通过使用C2可以提高至少10倍的RC(RC通过R1/C1与RIN/CIN的网路构成)时间常数,这将有助于提高共模抑制比。

RA与RB在使用100kΩ,并且电路带宽没有降低的时候,C2可以保持相当小的容量。

也可以采用其它的方法在单电源中提供偏置电压,并且有很好的电源抑制与共模抑制。

比如在偏置电路中可以使用一个齐纳二极管调整偏置电压,提供静态工作点。

图4:

利用相同的齐纳二极管的反相放大器电路的偏置方法。

在图3中,电流通过电阻RZ流到齐纳二极管,形成偏置工作点。

电容CN可以阻止齐纳二极管产生的噪声通过反馈进入运放。

要想实现低噪声电路需要使用一个比10uF还大的CN,并且齐纳二极管应该选择一个工作电压在Vs/2。

电阻RZ必须选择能够提供齐纳二极管工作在稳定的额定电压上和保持输出噪声电流比较低的水平上。

因为运放的输入电流只有1pA左右,几乎接近零,所以为了减小输出噪声电流,低功耗的齐纳二极管是非常理想的选择。

可以选择250mW的齐纳二极管,但为了考虑成本,选择500mW的齐纳二极管也是可以接受。

齐纳二极管的工作电流会因制造商的不同有些差别,在应用中一般IZ在5mA(250mW)与5uA(500mW)之间比较好。

表4:

电路参数及期间参数选择

在齐纳二极管的工作极限范围之内,采用下面电路(图3、图4)将有比较好的电源抑制能力。

但这个电路有一些缺陷,因为运放输出的静态工作点是齐纳二极管的电压而不是Vs/2。

如果电源电压下降,大信号输出的波形将会失真(出现不对称的削顶波形),此时电路还要消耗更多的电能。

电阻RIN与R2应该选择相同的电阻值,防止偏置电流引起更大的失调电压误差。

运算放大器容性负载驱动问题

问:

为什么我要考虑驱动容性负载问题?

答:

通常这是无法选择的。

在大多数情况下,负载电容并非人为地所加电容。

它常常是人们不希望的一种客观存在,例如一段同轴电缆所表现出的电容效应。

但是在有些情况下,要求对运算放大器的输出端的直流电压进行去耦。

例如,当运放被用作基准电压的倒相或驱动一个动态负载时。

在这种情况下,你也许在运放的输出端直接连接旁路电容。

不论哪种情况,容性负载都要对运放的性能有影响。

容性负载如何影响运放的性能?

为简单起见,可将放大器看成一个振荡器。

每个运放都有一个内部输出电阻RO,当它与容性负载相接时,在运放传递函数上产生一个附加的极点。

正如图1(b)波特图幅频特性曲线表示,附加极点的幅频特性斜率比主极点20dB/十倍频程更徒。

从相频特性曲线图1(c)中可以看出,每个附加极点的相移都增加-90°

。

我们可用图1(b)或图1(c)来判断电路的稳定性。

从图1(b)中可以看出,当开环增益和反馈衰减之和大于1时,电路会不稳定。

同样,在图1(c)中,如果某一工作频率低于闭环带宽,在这个频率下环路相移超过-180°

时,运放会出现振荡。

电压反馈型运算放大器(VFA)的闭环带宽等于运放增益带宽积(GBP,或单位增益频率)除以电路闭环增益(ACL)。

运算放大器电路的相位裕度定义为使电路不稳定所要求的闭环带宽处对应的附加相移(即环路相移十相位裕度=-180°

)。

当相位裕度为0时,环路相移为-180°

,此运放电路不稳定。

通常,当相位裕度小于45°

时,会出现问题,例如频响“尖峰”,阶跃响应中的过冲或“振铃”。

为了使相位裕度留有余地,容性负载产生的附加极点至少应比电路的闭环带宽高10倍,如果不是这样电路可能不稳定。

图1容性负载电路及其波特图

那么我应该如何处理容性负载?

首先我们应该确定运放是否能稳定地驱动自身负载。

许多运放数据手册都给出“容性负载驱动能力”这项指标。

还有一些运放提供“小信号过冲与容性负载关系曲线”,从中你可以看到过冲与附加负载电容呈指数关系增加,当达到100%时,运放不稳定。

如果有可能,应该使运放过冲远离100%。

还应注意这条曲线对应指定增益。

对于VFA,容性负载驱动能力随增益成比例增加。

所以,如果在增益为1时,VFA可稳定驱动100pF容性负载,那么在增益为10时,便能驱动1000pF容性负载。

也有少数运放的产品说明中给出开环输出电阻RO,从而可以计算出上述附加极点的频率fP=1/2πROCL。

如果附加极点fP大于上述电路带宽10倍,则电路稳定。

如果运放的产品说明没有提供容性负载驱动能力或开环输出电阻的指标,也没有给出过冲与容性负载关系曲线,那么要保证电路稳定,你必须对容性负载采取必要的补偿措施。

要使标准运放驱动容负载工作稳定有许多处理方法,下面介绍几种。

(1)提高噪声增益法

使低频电路稳定的有效方法,也是设计者常常忽略的方法,就是增加电路的闭环增益(即噪声增益),而不改变信号增益,这样可在开环增益与反馈衰减到0dB带宽之积恒定条件下降低噪声带宽。

具体电路如图2所示。

在图2(a)中,在运放的两个输入端之间接电阻RD。

此时电路的增益可由给定公式计算。

因为是噪声增益而不是信号增益支配稳定性,所以电路稳定性的提高不影响信号增益。

为保证电路稳定,最简单的方法是使噪声带宽至少应比容性负载极点频率低10倍频程。

图2提高效大器噪声增益电路

图3环路增益波特图

这种方法的缺点是输入端电压噪声和输入失调电压被放大产生附加的输出电压噪声和输出失调电压增加。

用一个电容CD与电阻RD串联可以消除附加的直流失调电压,但增加的电压噪声是器件固有的,不能消除。

当选用CD时,其电容值应尽可能大。

为保证噪声极点至少低于“噪声带宽”10倍,CD最小应取10ANOISE/2πRDGBP。

(2)环路外补偿法

这种方法是在运放的输出端和负载电容之间串入一个电阻RX,如图4所示。

虽然RX加在反馈环路的外部,但它可将负载电容产生的附加零点频率fZ作用到反馈网络的传递函数,从而可以减小高频环路相移。

为了保证电路稳定,RX的取值应该使附加零点频率至少比运放电路闭环带宽低10倍。

电路加入RX使电路性能不会像方法1那样增加输出噪声,但是从负载端看进去的输出阻抗要增加。

由于RX和RL构成分压器,从而会使信号增益降低。

如果RL已知并且适当地恒定,那么增益降低值可通提高运放电路的增益来补偿。

这种方法用于驱动传输线路非常有用。

RL和RX值必须等于电缆的特征阻抗(通常为50Ω和75Ω),以免产生驻波。

因此,先确定RX值,其余其它电阻值要使放大器的增益加倍,用来补偿由电阻分压作用降低的信号增益,从而解决问题。

图4环路外补偿法

(3)环路内补偿法

如果RL值未知,或者是动态值,那么增益级的有效输出电阻必须很低。

在这种情况下,在整个反馈环路内接一个电阻RX是很有用的,如图5所示。

在这个电路中,由于直流和低频反馈都是来自负载电阻RL,所以从输入端到负载的信号增益不受分压器RX和RL的影响。

RX=RORGRF

CF=RO+RXRF·

CL

在这个电路中外接的电容CF是用来抵消CL产生的附加极点和零点。

为了简便起见,CF产生的零点频率应该与CL产生的极点频率相一致,CF产生的极点频率应该与CL产生的零点频率相一致。

因此整个传递函数和相频响应好像似没有电容作用一样。

为了确保极点和零点作用相互抵消,图5中的方程必须求解准确。

还应注意方程成立的条件:

RF?

鞷O,RG?

鞷O,RL?

鞷O。

如果负载电阻很大,这些条件容易满足。

当RO未知时,计算则很困难。

在这种情况下,设计过程变成猜谜游戏。

应该注意“SPICE”这个词:

运算放大器的SPICE模型是一种不能精确地表示运放开环输出电阻RO的模型,所以这种模型不能完全取代传统的补偿网络设计方法。

还应当强调指出的是,为了采用这种方法,CL必须已知(且为常数)。

在许多应用中,放大器驱动一个电路外部的负载,当负载改换时,CL也应该适当变化。

只有当CL接入闭环系统时,使用上述电路才最适合。

这种在基准电压的缓冲器或倒相器中,驱动一个大的去耦电容。

这里CL是固定值,可以精确地抵消极点和零点的作用。

与前两种方法相比,这种方法非常适合用于低直流输出电阻和低噪声的情况。

而且像对基准电压源进行去耦的那么大的容性负载(一般几微法),用其它方法补偿都是不切实际的。

上述三种补偿方法都各有其优点和缺点。

为了对你的应用做出最好的选择,应该对它们有足够的认识。

这三种方法都适合用于“标准”用法,即单位增益稳定,电压反馈运算放大器(VFA)。

对于特殊应用的放大器,读者应该采用其它方法。

我的运放有一个“补偿”脚。

当驱动容性负载时,为使电路保持稳定,我能用它对运放进行补偿吗?

可以。

这是对容性负载进行补偿的最简单的方法。

现在许多运放都带有使单位增益稳定的内部补偿电路。

但是许多运放只有在很高噪声增益下才能一直保持固有的稳定性。

这类运放有一个与外部电容相连的引脚,用来减少主极点频率。

为了在低增益时工作稳定,外接电容必须靠近这个引脚,以减小增益带宽积。

当驱动容性负载时,增加外接电容过补偿)可以提高稳定性,但是带宽降低。

到现在为止,你只讨论了VFA的容性负载驱动问题,是吗?

那么对于电流反馈运算放大器(CFA)的容性负载驱动问题应如何处理?

上述讨论的那些方法,我可以使用吗?

当驱动容性负载时,对CFA的一些特性要特别注意,但容性负载对电路的影响是相同的。

与运放输出电阻相连的容性负载产生附加极点,从而增加相移并降低相位裕度,有可能产生尖峰、振铃,甚至振荡。

但是,因为CFA不存在增益带宽积这个概念(带宽依赖于增益的程度很小),所以通过简单增加噪声增益的方法,对提高电路稳定性没有显著作用。

这样便使第一种方法失效。

另外,电容绝不应接入CFA反馈环路,这样又使第三种方法失效。

对驱动容性负载的CFA进行补偿最合适的方法是方法2,在环路外串接一个电阻。

你上述介绍了一些很有用的方法,但是我还不能处理容性负载驱动问题。

另外,我的印制线路板已经制好,并且不想报废。

请问是否有驱动容性负载自身很稳定的运放?

有。

ADI公司提供一些很有用的运放,它们既能驱动“无限制”容性负载,同时又能保持优良的相位裕度,如表1所示。

表1还给出了驱动容性负载可高达规定值的另一类运放。

所谓驱动容性负载“无限制”并不是意味着驱动10μF容性负载像驱动阻性负载那样具有相同的转换速率。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 运算放大器 电路 误差 分析 汇总

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx