第九讲显示译码器及译码器的应用Word文件下载.docx

第九讲显示译码器及译码器的应用Word文件下载.docx

- 文档编号:19358760

- 上传时间:2023-01-05

- 格式:DOCX

- 页数:9

- 大小:242.32KB

第九讲显示译码器及译码器的应用Word文件下载.docx

《第九讲显示译码器及译码器的应用Word文件下载.docx》由会员分享,可在线阅读,更多相关《第九讲显示译码器及译码器的应用Word文件下载.docx(9页珍藏版)》请在冰豆网上搜索。

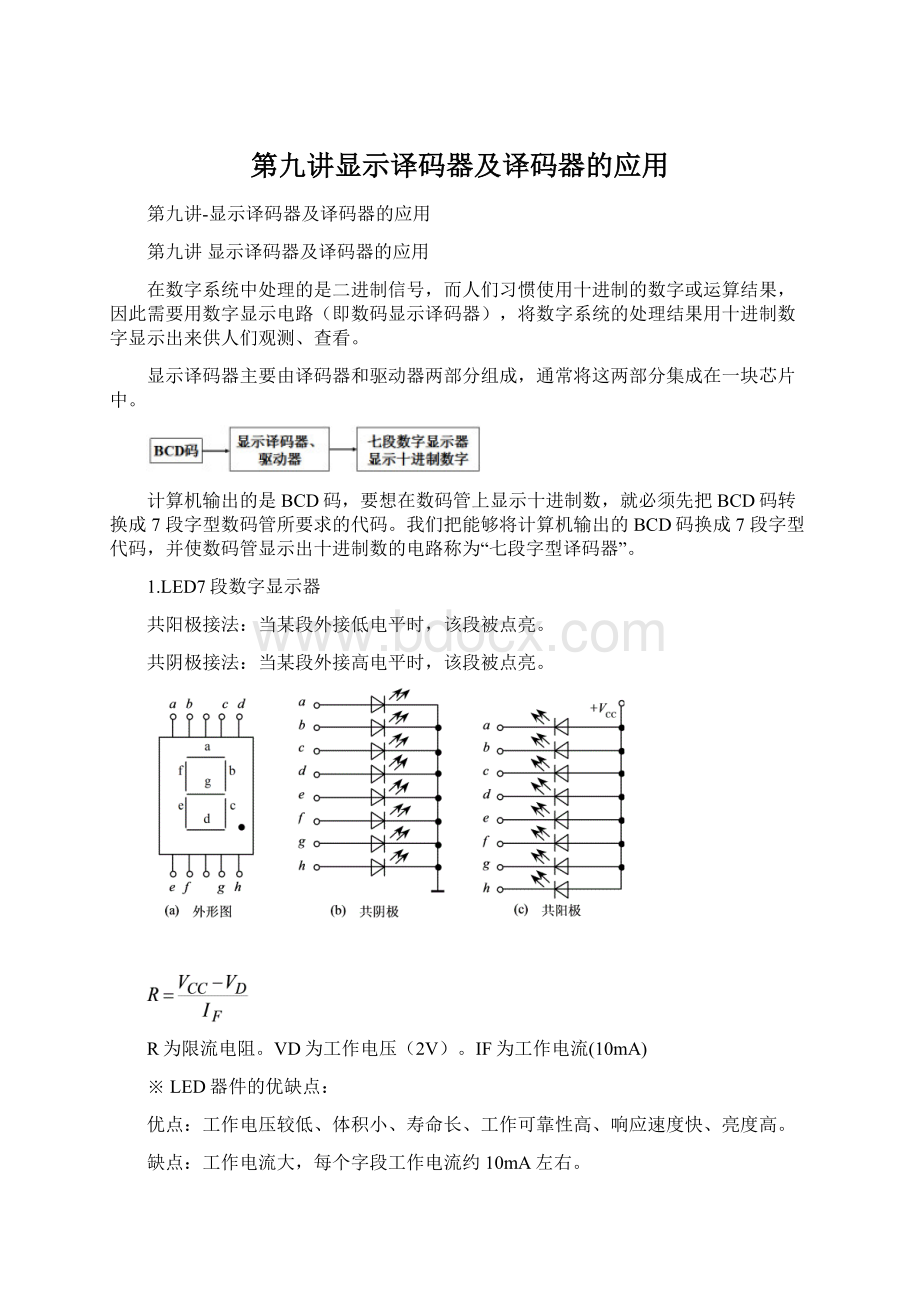

R为限流电阻。

VD为工作电压(2V)。

IF为工作电流(10mA)

※LED器件的优缺点:

优点:

工作电压较低、体积小、寿命长、工作可靠性高、响应速度快、亮度高。

缺点:

工作电流大,每个字段工作电流约10mA左右。

2.液晶显示器(LCD)

1)液晶是液态晶体的简称。

它是既具有液体的流动性,又具有某些光学特性的有机化合物。

2)其透明度和颜色受外加电场的控制。

3)控制显示原理:

①没有外加电场时,液晶分子排列整齐,入射的光线绝大部分被反射回来,液晶呈现透明状态,不显示数字。

②当在相应字段的电极加上电压时,液晶中的导电正离子作定向运动,在运动过程中不断撞击液晶分子,从而破坏了液晶分子的整齐排列,使入射光产生了散射而变得混浊,使原来透明的液晶变成了暗灰色,从而显示出相应的数字。

③当外加电压断开时,液晶分子又恢复到整齐排列的状态,显示的数字也随之消失。

4)液晶显示器的优缺点:

功耗极小,工作电压低;

显示不够清晰,响应速度慢。

※七段显示译码器相当于一个代码转换电路,四位输入BCD码→七段代码。

常用的4线—7段译码器/驱动器是CC14547。

CC14547具有较大的输出电流驱动能力,可直接驱动LED或其它显示器。

输入:

4位,8421BCD码D、C、B、A(原码)

输出:

7段,Ya~Yg,高电平有效(输出1时该段点亮)

消隐控制端:

,低电平有效。

当=0时,输出Ya~Yg都为低电平,各字段都熄灭,不显示数字。

当=1时,译码器工作。

※显示译码器分类:

•输出低电平有效,配共阳极显示器;

•输出高电平有效,配共阴极显示器。

a段卡诺图:

下列真值表仅适用于共阴极LED:

同理可得其它各段的函数式为:

逻辑图如下:

集成显示译码器74LS48

功能表:

辅助端功能:

由真值表可以看出,为了增强器件的功能,在74LS48中还设置了一些辅助端。

这些辅助端的功能如下:

(1)试灯输入端LT:

低电平有效。

当LT=0时,数码管的七段应全亮,与输入的译码信号无关。

本输入端用于测试数码管的好坏。

(3)灭灯输入/动态灭零输出端BI/RBO:

这是一个特殊的端钮,有时用作输入,有时用作输出。

当BI/RBO作为输入使用,且BI/RBO=0时,数码管七段全灭,与译码输入无关。

当BI/RBO作为输出使用时,受控于LT和RBI:

当LT=1且RBI=0时,BI/RBO=0;

其它情况下BI/RBO=1。

本端钮主要用于显示多位数字时,多个译码器之间的连接。

译码器的应用

1.用译码器实现组合逻辑函数

原理:

变量译码器输出能产生输入变量的所有最小项。

高电平输出时:

低电平输出时:

而任何一个组合逻辑函数都可以变换为最小项之和的标准形式。

因此,用译码器和门电路可实现任何单输出或多输出的组合逻辑函数。

当译码器输出低电平有效时,一般选用与非门;

当译码器输出高电平有效时,一般选用或门;

例1.用译码器实现三个输入变量函数

解:

译码器没有特指的情况下,指的都是变量译码器。

低电平输出有效的译码器能产生输入变量的所有最小项的非。

由于任何逻辑函数都可以按照最小项之和表示成标准积之和的形式,再二次求反,变成与非---与非式。

因此可以想象,利用译码器得到最

小项之非,而由外部的与非门来形成与

非,即可实现逻辑函数。

由于本题有三个输入变量,共八个

最小项。

可以采用3线-8线译码器(如

74LS138),得到逻辑电路图如右图。

例2.用译码器和门电路实现逻辑函数:

1)选择译码器。

由于Y中有3个变量A、B、C,故应选3-8译码器,如74LS138。

因74LS138输出为低电平有效,故选用与非门。

2)将Y变换为标准与或表达式。

3)令A2=A、A1=B、A0=C,可画出逻辑电路图。

例3.用译码器设计一个一位全加器。

它能将两个二进制数及来自低位的进位进行相加,并产生和数与进位数。

1)分析设计要求,列出真值表。

设被加数为Ai,加数为Bi,来自低位的进位为Ci-1。

本位和为Si,向高位的进位为Ci。

输入

输出

AiBiCi-1

SiCi

000

001

010

011

100

101

110

111

00

10

01

11

2)写出逻辑函数表达式

3)选择译码器

全加器有3个输入信号,有两个输出信号,因此可选74LS138和两个与非门来实现。

4)将Ai连A2、Bi连A1、Ci-1连A0,则Si、Ci式变为:

5)有此可画出所设计的全加器电路图。

※用二进制译码器实现码制变换:

※数码显示电路的动态灭零:

2.计算机端口地址译码

(1)地址译码电路的作用:

地址+控制信号接口芯片的选择信号

(2)地址译码电路的输出信号:

低电平有效

(3)I/O地址译码方法(高位地址、低位地址的划分):

片间选择:

高位地址+控制信号片选信号

片内端口选择:

低地址直接与接口芯片地址线连接

(4)地址范围:

n根地址线未参与译码,译出地址含2n个

例:

PC机系统板上的端口地址译码电路(为每个接口芯片分配一个含有32个地址的地址范围)

PC/XT系统板上I/O端口译码电路

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 第九 显示 译码器 应用

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx