网络MII接口与详解文档格式.docx

网络MII接口与详解文档格式.docx

- 文档编号:19320448

- 上传时间:2023-01-05

- 格式:DOCX

- 页数:18

- 大小:516.83KB

网络MII接口与详解文档格式.docx

《网络MII接口与详解文档格式.docx》由会员分享,可在线阅读,更多相关《网络MII接口与详解文档格式.docx(18页珍藏版)》请在冰豆网上搜索。

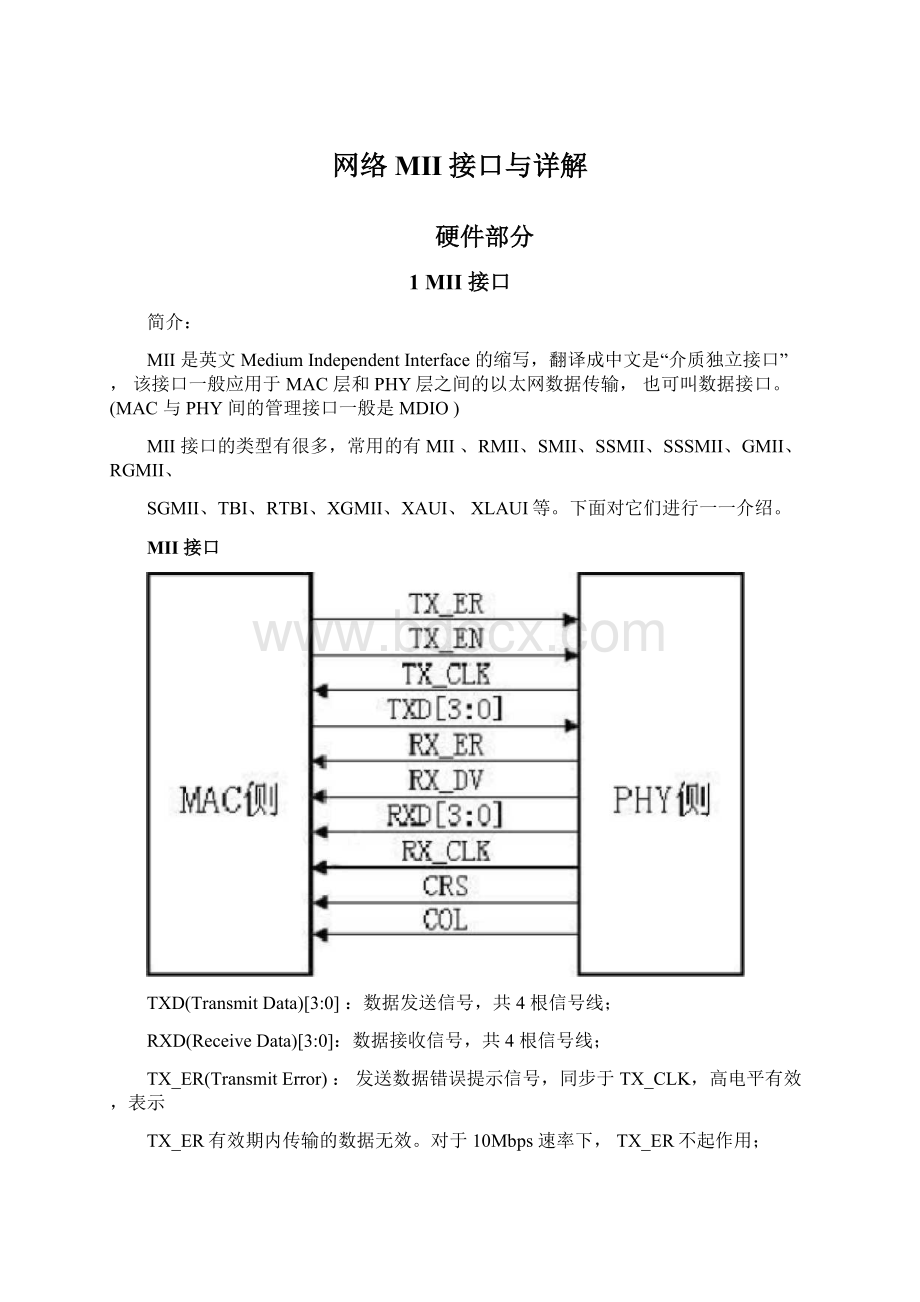

TX_CLK:

发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的。

RX_CLK:

接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。

RX_CLK也是由PHY侧提供的。

CRS:

CarrierSense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就

有效,另外,CRS只有PHY在半双工模式下有效;

COL:

CollisionDetectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模

式下有效。

MII接口一共有16根线。

RMII接口

RMII即ReducedMII,是MII的简化板,连线数量由MII的16根减少为8根。

TXD[1:

数据发送信号线,数据位宽为2,是MII接口的一半;

RXD[1:

数据接收信号线,数据位宽为2,是MII接口的一半;

TX_EN(TransmitEnable):

数据发送使能信号,与MII接口中的该信号线功能一样;

RX_ER(ReceiveError:

)数据接收错误提示信号,与MII接口中的该信号线功能一样;

CLK_REF:

是由外部时钟源提供的50MHz参考时钟,与MII接口不同,MII接口中的接收时钟和发送时钟是分开的,而且都是由PHY芯片提供给MAC芯片的。

这里需要注意的是,由于数据接收时钟是由外部晶振提供而不是由载波信号提取的,所以在PHY层芯片内的数据接收部分需要设计一个FIFO,用来协调两个不同的时钟,在发送接收的数据时提供缓冲。

PHY层芯片的发送部分则不需要FIFO,它直接将接收到的数据发送到MAC就可以了。

CRS_DV:

此信号是由MII接口中的RX_DV和CRS两个信号合并而成。

当介质不空闲时,CRS_DV和RE_CLK相异步的方式给出。

当CRS比RX_DV早结束时(即载波消失而队列中还有数据要传输时),就会出现CRS_DV在半位元组的边界以25MHz/2.5MHz的频率在0、1之间的来回切换。

因此,MAC能够从CRS_DV中精确的恢复出RX_DV和CRS。

在100Mbps速率时,TX/RX每个时钟周期采样一个数据;

在10Mbps速率时,TX/RX每

隔10个周期采样一个数据,因而TX/RX数据需要在数据线上保留10个周期,相当于一个数据发送10次。

当PHY层芯片收到有效的载波信号后,CRS_DV信号变为有效,此时如果FIFO中还没有数据,则它会发送出全0的数据给MAC,然后当FIFO中填入有效的数据帧,数据帧的开头是“101010---”交叉的前导码,当数据中出现“01”的比特时,代表正式数据传输开始,

MAC芯片检测到这一变化,从而开始接收数据。

当外部载波信号消失后,CRS_DV会变为无效,但如果FIFO中还有数据要发送时,CRS_DV在下一周期又会变为有效,然后再无效再有效,直到FIFO中数据发送完为止。

在接收过程

中如果出现无效的载波信号或者无效的数据编码,则RX_ER会变为有效,表示物理层芯片

接收出错。

SMII接口

SMII即SerialMII,串行MII的意思,跟RMII相比,连线进一步减少到4根;

TXD:

发送数据信号,位宽为1;

RXD:

接收数据信号,位宽为1;

SYNC:

收发数据同步信号,每10个时钟周期置1次高电平,指示同步。

所有端口共用的一个参考时钟,频率为125MHz,为什么100Mbps速率要用

125MHz时钟?

因为在每8位数据中会插入2位控制信号,请看下面介绍。

TXD/RXD以10比特为一组,以SYNC为高电平来指示一组数据的开始,在SYNC变高后的10个时钟周期内,TXD上依次输出的数据是:

TXD[7:

0]、TX_EN、TX_ER,控制信号的含义与MII接口中的相同;

RXD上依次输出的数据是:

RXD[7:

0]、RX_DV、CRS,RXD[7:

0]的含义与RX_DV有关,当RX_DV为有效时(高电平),RXD[7:

0]上传输的是物理层接收的数据。

当RX_DV为无效时(低电平),RXD[7:

0]上传输的是物理层的状态信息数据。

见下表:

当速率为10Mbps时,每一组数据要重复

10次,MAC/PHY芯片每10个周期采样一次。

MAC/PHY芯片在接收到数据后会进行串

/并转换。

SSMII接口

SSMII即SerialSyncMII,叫串行同步接口,跟SMII接口很类似,

只是收发使用独立的参

考时钟和同步时钟,不再像SMII那样收发共用参考时钟和同步时钟,

传输距离比SMII更远。

SSSMII接口

SSSMII即SourceSyncSerialMII,叫源同步串行MII接口,SSSMII与SSMII的区别在于参考时钟和同步时钟的方向,SSMII的TX/RX参考时钟和同步时钟都是由PHY芯片提供的,而SSSMII的TX参考时钟和同步时钟是由MAC芯片提供的,RX参考时钟和同步时钟是由PHY芯片提供的,所以顾名思义叫源同步串行。

接收参考时钟RX_CLK的频率均为125MHz(1000Mbps/8=125MHz)。

在这里有一点需要特别说明下,那就是发送参考时钟

GTX_CLK,它和MII接口中的TX_CLK

是不同的,MII接口中的TX_CLK是由PHY芯片提供给MAC芯片的,而GMII接口中的GTX_CLK

是由MAC芯片提供给PHY芯片的。

两者方向不一样。

在实际应用中,绝大多数GMII接口都是兼容MII接口的,所以,一般的GMII接口都有

两个发送参考时钟:

TX_CLK和GTX_CLK两(者的方向是不一样的,前面已经说过了),在用作

MII模式时,使用TX_CLK和8根数据线中的4根。

RGMII接口

RGMII即ReducedGMII,是GMII的简化版本,将接口信号线数量从24根减少到14根

(COL/CRS端口状态指示信号,这里没有画出),时钟频率仍旧为125MHz,TX/RX数据宽度从8为变为4位,为了保持1000Mbps的传输速率不变,RGMII接口在时钟的上升沿和下降沿都采样数据。

在参考时钟的上升沿发送GMII接口中的TXD[3:

0]/RXD[3:

0],在参考时钟的下降沿发送GMII接口中的TXD[7:

4]/RXD[7:

4]。

RGMI同时也兼容100Mbps和10Mbps两种速率,此时参考时钟速率分别为25MHz和2.5MHz。

TX_EN信号线上传送TX_EN和TX_ER两种信息,在TX_CLK的上升沿发送TX_EN,下降沿发送TX_ER;

同样的,RX_DV信号线上也传送RX_DV和RX_ER两种信息,在RX_CLK的上升沿发送RX_DV,下降沿发送RX_ER。

SGMII接口

SGMII即SerialGMII,串行GMII,收发各一对差分信号线,时钟频率625MHz,在时钟

信号的上升沿和下降沿均采样,参考时钟RX_CLK由PHY提供,是可选的,主要用于MAC

侧没有时钟的情况,一般情况下,RXCLK不使用。

收发都可以从数据中恢复出时钟。

在TXD发送的串行数据中,每8比特数据会插入TXEN/TXER两比特控制信息,同样,

在RXD接收数据中,每8比特数据会插入RXDV/RXER两比特控制信息,所以总的数据速

率为1.25Gbps=625Mbps*2.

其实,大多数MAC芯片的SGMII接口都可以配置成SerDes接口(在物理上完全兼容,只需配置寄存器即可),直接外接光模块,而不需要PHY层芯片,此时时钟速率仍旧是625MHz,不过此时跟SGMII接口不同,SGMII接口速率被提高到1.25Gbps是因为插入了控制信息,而SerDes端口速率被提高是因为进行了8B/10B变换,本来8B/10B变换是PHY芯片的工作,在SerDes接口中,因为外面不接PHY芯片,此时8B/10B变换在MAC芯片中完成了。

8B/10B

变换的主要作用是扰码,让信号中不出现过长的连“

0”和连“1”情况,影响时钟信息的提

取,关于8B/10B变换知识,我后续会单独介绍。

TBI接口

TBI即TenBitInterface的意思,接口数据位宽由GMII接口的8位增加到10位,其实,TBI接口跟GMII接口的差别不是很大,多出来的2位数据主要是因为在TBI接口下,MAC芯片在将数据发给PHY芯片之前进行了8B/10B变换(8B/10B变换本是在PHY芯片中完成的,前面已经说过了),另外,RX_CLK+-/是从接收数据中恢复出来的半频时钟,频率为62.5MHz,RX_CLK+-/不是差分信号,而是两个独立的信号,两者之间有180度的相位差,在这两个时

钟的上升沿都采样数据。

RXCLK+-/也叫伪差分信号。

除掉上面说到的之外,剩下的信号都跟GMII接口中的相同。

大多数芯片的TBI接口和GMII接口兼容。

在用作TBI接口时,CRS和COL一般不用。

RTBI接口

RTBI即ReducedTBI,简化版TBI,接口数据位宽为5bit,时钟频率为125MHz,在时钟的上升沿和下降沿都采样数据,同RGMII接口一样,TX_EN线上会传送TX_EN和TX_ER两种信息,在时钟的上升沿传TX_EN,下降沿传TX_ER;

RX_DV线上传送RX_DV和RX_ER两种信息,在RX_CLK上升沿传RX_DV,下降沿传RX_ER。

万兆以太网接口的端口速率为10Gbps,主要有XGMII和XAUI两种,另外还有HIGIG,不过HIGIG是Broadcom公司的私有标准,这里暂不介绍。

XGMII接口

TXD[31:

数据发送通道,

32位并行数据。

RXD[31:

数据接收通道,

TXC[3:

发送通道控制信号,TXC=0时,表示TXD上传输的是数据;

TXC=1时,表示

TXD上传输的是控制字符。

0]分别对应TXD[31:

24],TXD[23:

16],TXD[15:

8],TXD[7:

0]。

RXC[3:

接收通道控制信号,RXC=0时,表示RXD上传输的是数据;

RXC=1时,表示

RXD上传输的是控制字符。

0]分别对应RXD[31:

24],RXD[23:

16],RXD[15:

8],RXD[7:

TXD和TXC的参考时钟,时钟频率156.25MHz,在时钟信号的上升沿和下降沿都采样数据。

156.25MHz*2*32=10Gbps。

RXD和RXC的参考时钟,时钟频率156.25MHz,在时钟信号的上升沿和下降沿都采样数据。

XGMII接口共74根连线,单端信号,采用HSTL/SSTL_2逻辑,端口电压1.5V/2.5V,由于SSTL_2的端口电压高,功耗大,现在已很少使用。

HSTL即HighSpeedTransceiverLogic,

高速发送逻辑的意思。

SSTL,即StubSeriesTerminatedLogic,短路终止逻辑,主要用于高速内存接口,SSTL目前存在两种标准,SSTL_3是3.3V标准;

SSTL_2是2.5V标准。

XAUI接口

由于受电气特性的影响,XGMII接口的PCB走线最大传输距离仅有7cm,并且XGMII接口的连线数量太多,给实际应用带来不便,因此,在实际应用中,XGMII接口通常被XAUI接口代替,XAUI即10Gigabitattachmentunitinterface,10G附属单元接口,XAUI在XGMII的基础上实现了XGMII接口的物理距离扩展,将PCB走线的传输距离增加到50cm,使背板走线成为可能。

源端XGMII把收发32位宽度数据流分为4个独立的lane通道,每个lane通道对应一个字节,经XGXS(XGMIIExtenderSublayer完)成8B/10B编码后,将4个lane分别对应XAUI的4个独立通道,XAUI端口速率为:

2.5Gbps*1.25*4=12.5Gbps。

在发送端的XGXS模块中,将TXD[31:

0]/RXD[31:

0],TXC[3:

0]/RXC[3:

0],TX_CLK/RX_CLK转换成串行数据从TXLane[3:

0]/RXLane[3:

0]中发出去,在接收端的XGXS模块中,串行数据被转换成并行,并且进行时钟恢复和补偿,完成时钟去抖,经过5B/4B解码后,重新聚合成XGMII。

XAUI接口采用差分线,收发各四对,CML逻辑,AC耦合方式,耦合电容在10nF~100nF之间。

XAUI接口可以直接接光模块,如XENPAK/X2等。

也可以转换成一路10G信号XFI,接XFP/SFP+等。

有些芯片不支持XAUI接口,只支持XGMII接口,这时可以用专门的芯片进行XGMII/XAUI接口转换,如BCM8011等。

请叫我华丽的分割线

对于10/100M的MII

rx_clk都是PHY提供,为2.5MHz/25MHz

txclk都是PHY提供,为2.5MHz/25MHz

数据位4bit,即使用MDI的4根线,即

2对差分线

对于10/100/1000M的(G)MII

rx_clk由PHY提供,为2.5MHz/25MHz/125MHz

10/100M时,使用tx_clk,由PHY提供,为2.5MHz/25MHz

1000M时,使用gtx_clk,由MAC提供,为125MHz

对于10/100/1000M的RGMII

rx_clk由PHY提供,为125MHz

gtx_clk由MAC提供,为125MHz

对于MAC和PHY连接,我们称为Forward(G)MII

对于MAC和MAC相连,叫Reverse(G)MII

2MII接口详解

词条简介

MII(MediaIndependentInterface(介质无关接口);

或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。

它包括一个数据接口,以及一个MAC和PHY之间的管理接口。

数

据接口包括分别用于发送器和接收器的两条独立信道。

每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需要16个信号。

管理接口是个双信号接口:

一个是时钟信号,另一个是数据信号。

通过管理接口,上层能监视和控制PHY。

MII(Managementinterface)

只有两条信号线。

MII标准接口用于连快FastEthernetMAC-block与PHY。

"

介质无关"

表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。

在其他速率下工作的与MII等效的接口有:

AUI(10M以太网)、GMII(Gigabit以太网)和XAUI(10-Gigabit以太网)。

MII总线

在IEEE802.3中规定的MII总线是一种用于将不同类型的PHY与相同网络控制器(MAC)相连接的通用总线。

网络控制器可以用同样的硬件接口与任何PHY进行连接。

MII相关接口介绍

以太网媒体接口有:

MIIRMIISMIIGMII

所有的这些接口都从MII而来,MII是(MediumIndependentInterface)的意思,是指不用考虑媒体是铜轴、光纤、电缆等,因为这些媒体处理的相关工作都有PHY或者叫做MAC

的芯片完成。

MII支持10兆和100兆的操作,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多,如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到32端口的话就要用到448根线,一般按照这个接口做交换机,是不太现实的,所以现代的交换机的制作都会用到其它的一些从MII简化出来的标准,比如RMII、SMII、GMII等。

RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线,所以它一般要求是50兆的总线时钟。

RMII一般用在多端口的交换机,它不是每个端口安排收、发两个时钟,而是所有的数据端口公用一个时钟用于所有端口的收发,这里就节省了不少的端口数目。

RMII的一个端口要求7个数据线,比MII少了一倍,所以交换机能够接入多一倍数据的端口。

和MII一样,RMII支持10兆和100兆的总线接口速度。

SMII是由思科提出的一种媒体接口,它有比RMII更少的信号线数目,S表示串行的意思。

因为它只用一根信号线传送发送数据,一根信号线传输接受数据,所以在时钟上为了满足100的需求,它的时钟频率很高,达到了125兆,为什么用125兆,是因为数据线里面会传送一些控制信息。

SMII一个端口仅用4根信号线完成100信号的传输,比起RMII差不多又少了一倍的信号线。

SMII在工业界的支持力度是很高的。

同理,所有端口的数据收发都公用同一个外部的125M时钟。

GMII是千兆网的MII接口,这个也有相应的RGMII接口,表示简化了的GMII接口。

MII工作原理

“媒体独立”表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备

都可以正常工作。

包括分别用于发送器和接收器的两条独立信道。

每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需要16个信号,包括TX_ER,TXD,TX_EN,TX_CLK,COL,RXD,RX_EX,RX_CLK,CRS,RX_DV等。

MII以4位半字节方式传送数据双向传输,时钟速率25MHz。

其工作速率可达100Mb/s。

MII管理接口是个双信号接口,一个是时钟信号,另一个是数据信号。

通过管理接口,上层能监视和控制PHY,其管理是使用SM(ISerialManagementInterface)总线通过读写PHY的寄存器来完成的。

PHY里面的部分寄存器是IEEE定义的,这样PHY把自己的目前的状态反映到寄存器里面,MAC通过SMI总线不断的读取PHY的状态寄存器以得知目前PHY的状态,例如连接速度,双工的能力等。

当然也可以通过SMI设置PHY的寄存器达到控制的目的,例如流控的打开关闭,自协商模式还是强制模式等。

不论是物理连接的MII总线和SMI总线还是PHY的状态寄存器和控制寄存器都是有IEEE的规范的,因此不同公司的MAC和PHY一样可以协调工作。

当然为了配合不同公司的PHY的自己特有的一些功能,驱动需要做相应的修改。

PHY是物理接口收发器,它实现物理层。

包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。

100BaseTX采用4B/5B编码。

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是CRC),每4bit就增加1bit的检错码,然后把并行

数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去。

收数据时的流程反之。

PHY还有个重要的功能就是实现CSMA/CD的部分功能。

它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。

如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。

这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突。

通信速率通过双方协商,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式,这个技术被称为AutoNegotiation或者NWAY。

隔离变压器把PHY送出来的差分信号用差模耦合的线圈耦合滤波以增强信号,并且通过电磁场的转换耦合到连接网线的另外

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 网络 MII 接口 详解

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx