计算机系统结构课后答案unit4Word格式.docx

计算机系统结构课后答案unit4Word格式.docx

- 文档编号:19265060

- 上传时间:2023-01-04

- 格式:DOCX

- 页数:7

- 大小:21.21KB

计算机系统结构课后答案unit4Word格式.docx

《计算机系统结构课后答案unit4Word格式.docx》由会员分享,可在线阅读,更多相关《计算机系统结构课后答案unit4Word格式.docx(7页珍藏版)》请在冰豆网上搜索。

由题意已知存取周期Tm=2*10^(-6)s,宽度W=4B,B实=0.6Bm=4*2^20B/S,

Bm=W*m/Tm=6.99*10^6B/S

m=Bm*Tm/W=6.99*10^6*2*10^-6/4=3.495

所以m取4能满足要求

P.S.

①微秒(百万分之一秒) 1μs=10^-6s

②计量单位中的M(兆)是10的6次方,见到M自然想起要在该数值的后边续上六个0,即扩大一百万倍。

在二进制中,MB也表示到了百万级的数量级,但1MB不正好等于1000000字节,而是1048576字节,即1MB=2E+20Bytes=1048576Bytes。

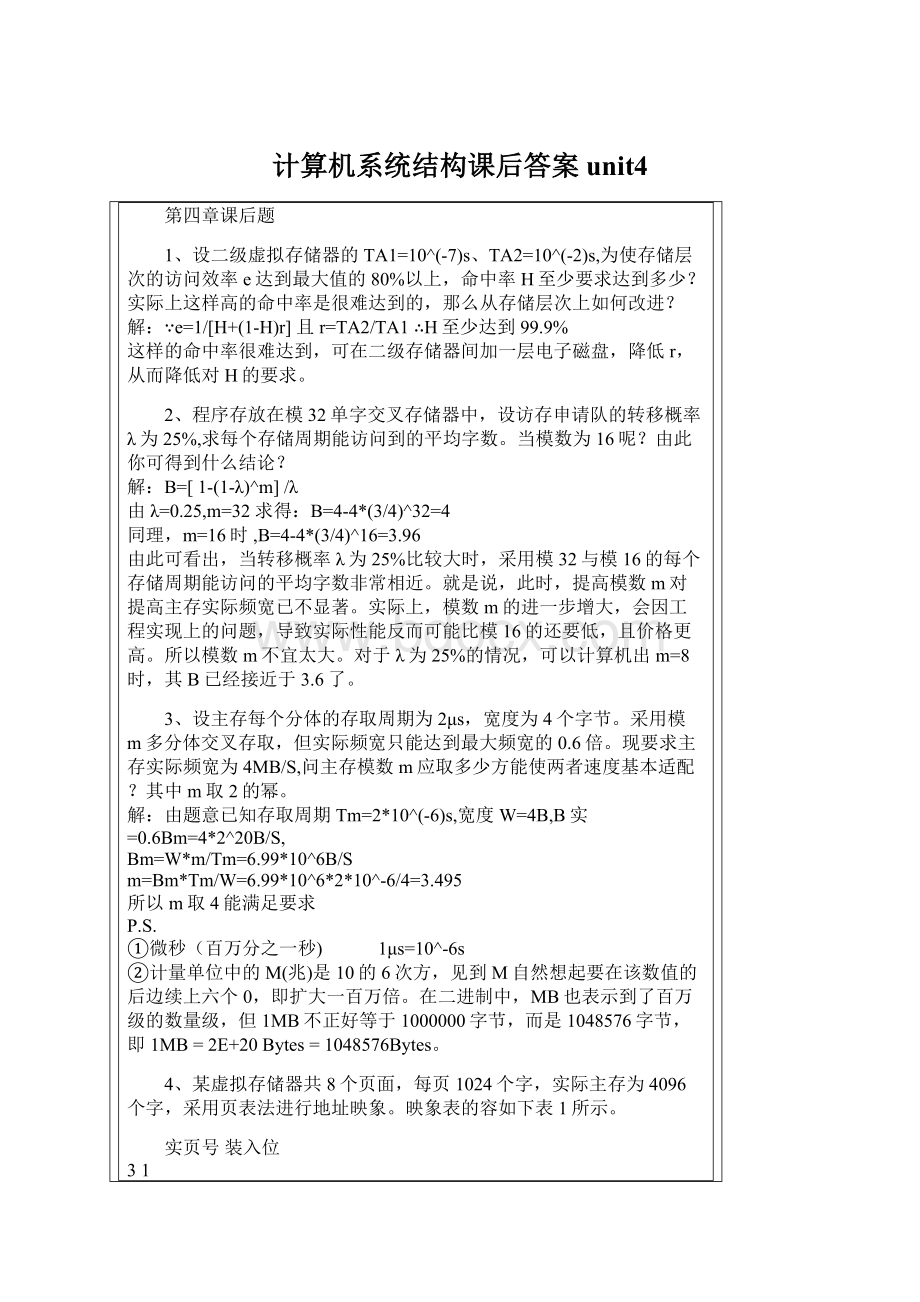

4、某虚拟存储器共8个页面,每页1024个字,实际主存为4096个字,采用页表法进行地址映象。

映象表的容如下表1所示。

实页号装入位

31

11

20

30

21

10

01

00

表1

虚页号实页号装入位

031

111

220

330

421

510

601

700

表2

(1)列出会发生页面失效的全部虚页号;

根据页表法列出表2,当装入位为0时,即为页面失效,再找出相对应的虚页号即可。

会发生页面失效的全部虚页号为:

2,3,5,7

(2)按以下虚地址计算主存实地址:

0,3728,1023,1024,2055,7800,4096,6800。

虚页号=│_虚地址/页面大小_│

实地址=(实页号*页面大小)+(虚地址-虚页号*页面大小)

虚地址03728102310242055780040966800

虚页号03012746

实页号33312020

装入位10110011

实地址307237284095102420556322048656

5、一个段页式虚拟存储器。

虚地址有2位段号、2位页号、11位页位移(按字编址),主存容量为32K字。

每段可有访问方式保护,其页表和保护位如下表所示。

(1)此地址空间中共有多少个虚页?

2Nv页,而Nv=用户虚页号=段号S+页号P

此地址空间中共有2^Nv=2^(2+2)=16个虚页

6、设某程序包含5个虚页,其页地址为4,5,3,2,5,1,3,2,2,5,1,3。

当使用LRU算法替

换时,为获得最高命中率,至少应分配给该程序几个实页?

其可能的最高命中率为多少?

7.采用页式管理的虚拟存储器,分时运行两道程序。

其中,程序X为

DO50I=1,3

B(I)=A(I)-C(I)

IF(B(I)·

LE·

0)GOTO40

D(I)=2*C(I)-A(I)

IF(D(I)·

EQ·

0)GOTO50

40 E(I)=0

50 CONTINUE

Data:

A=(-4,+2,0)

C=(-3,0,+1)

每个数组分别放在不同的页面中;

而程序Y在运行过程中,其数组将依次用到程序空间的第3,5,4,2,5,3,1,3,2,5,1,3,1,5,2页。

如果采用LRU算法,实存却只有8页位置可供存放数组之用。

试问为这两首程序的数组分别分配多少个实页最为合适?

为什么?

解答:

分别分配给程序X和Y的数组4个实页最为合适。

根据题意,程序X依次调用数组A,C,B,B,E,A,C,B,B,C,A,D,D,E,A,C,B,B,E中的数据。

设程序X中的数组A,B,C,D,E分别存放于程序空间的第1,2,3,4,5页,则程序的页地址流为:

1,3,2,2,5,1,3,2,2,3,1,4,4,5,1,3,2,2,5。

分析使用LRU算法对程序X的页地址流进行堆栈处理的过程可知,分配给程序X的数组5个实页最为合适;

分析使用LRU算法对程序Y的页地址流进行堆栈处理的过程可知,分配给程序Y的数组4个实页最为合适。

但实存只有8页位置可供存放数组之用,所以,分别分配给程序X和Y的数组4个实页。

note:

分时运行在微观上是串行的,就是说,分时运行时把时间划分为若干时间片,每个程序轮流占用时间片;

在宏观上是并行的,就是说,每个程序在一个时间片并不能运行完。

总的来看,是同时运行的,所以两个程序分配的实页和不能大于8。

参考:

上面的FORTRAN源代码转成C后

main()

{

intA[]={-4,2,0};

intC[]={-3,0,1};

for(i=0,i<

3,i++)

{B[i]=A[i]-C[i];

if(B[i]<

0)

E[i]=0;

else

{D[i]=2*C[i]-A[i];

if(D[i]<

>

};

}

8.设一个按位编址的虚拟存储器,它应可对应1K个任务,但在一段较长时间,一般只有4个任务在使用,故用容量为4行的相联寄存器组硬件来缩短被变换的虚地址中的用户位位数;

每个任务的程序空间最大可达4096页,每页为512个字节,实主存容量为2^20位;

设快表用按地址访问存储器构成,行数为32,快表的地址是经散列形成;

为减少散列冲突,配有两套独立相等比较电路。

请设计该地址变换机构,容包括:

(1)画出其虚、实地址经快表变换之逻辑结构示意图;

(2)相联寄存器组中每个寄存器的相联比较位数;

(3)相联寄存器组中每个寄存器的总位数;

(4)散列变换硬件的输入位数和输出位数;

(5)每个相等比较器的位数;

(6)快表的总容量(以位为单位)。

解:

(1)依题意得知:

虚地址为34位,其中用户号为10位(对应1K的任务)、虚页号12位(每个任务4096页)、页位移12位(每页512字节,512字节=512*8=1024*4=2^12)

实地址为20位,其中实页号8位,页位移12位(与虚页页位移对应)

相联寄存器的作用:

把10位的用户号转换为2位的ID(因为一般只有4个任务在使用),并把ID与虚地址的虚页号合并到快表中查实页号。

快表的作用:

相当于页表,即虚页号对实页号的对应关系。

但又有所简化(原因是如果用用户号和虚页号与实页号对应,前者就有22位,现改进后虚页号只有14位了)

(2)相联寄存器组中每个寄存器的相联比较位数为10(与虚地址中的用户号宽度对应)

(3)相联寄存器组中每个寄存器的总数为12(用户号宽度+ID宽度)

(4)散列变换硬件的输入位数为14位(虚页号宽度+相联寄存器中ID的宽度),输出位数为8位(与主存中的实页号宽度对应)

(5)每个相等比较器的位数=ID+用户虚页号nv'

=2+12=14(位)。

(6)快表的总容量:

32行*(14(输入位数)+8(输出位数))*2=32*22*2

9.考虑一个920个字的程序,其访问虚存的地址流为20,22,208,214,146,618,370,490,492,868,916,728。

(1)若页面大小为200字,主存容量为400字,采用FIFO替换算法,请按访存的各个时刻,写出其虚页地址流,计算主存的命中率;

(2)若页面大小为100字,再做一遍;

(3)若页面大小为400字,再做一遍;

(4)由

(1)、

(2)、(3)的结果可得出什么结论?

(5)若把主存容量增加到800字,按第

(1)小题再做一遍,又可得出什么结论?

(1)主存容量400字,页面大小200字,所以主存实页数为2;

把地址流转换为页地址流,以第一个虚地址流转换为页地址流为例说明:

求模公式为:

INT(地址/页面大小),就是把地址整除于页面大小,得INT(20/200)=0,下同,所以页地址流为:

0,0,1,1,0,3,1,2,2,4,4,3

按FIFO算法得出替换过程为:

0(调入),0(命中),1(调入),1(命中),0(命中),3(替换0,0比1先入队,所以被替换,下同),1(命中),2(替换1),2(命中),4(替换3),4(命中),3(替换2),所以总共命中6次。

故命中率H=6/12=50%

(2)方法同

(1)H=25%

(3)H=50%

(4)由以上结论可得,FIFO算法的条件下,当页面大小发生变化时,其命中率变化是:

一开始随页面大小增大命中率(第一步与第二步比较),但当页面大小增到一定时,命中率不再增加(第一步与第三步比较)。

(5)命中率为58%,结论是如果分配给主存容量增加时可以搞高命中率。

10.在一个页式二级虚拟存储器中,采用FIFO算法进行页面替换,发现命中率H太低,因此有下列建议:

(1)增大辅存容量;

(2)增大主存容量(页数);

(3)FIFO改为LRU;

(4)FIFO改为LRU,并增大主存容量(页数);

(5)FIFO改为LRU,并增大页面大小。

试分析上述各建议对命中率的影响情况。

(1)增大辅存容量,对命中率H无影响。

(2)增大主存容量(页数),可普遍提高命中率。

(3)FIFO改为LRU,一般可提高命中率。

(4)FIFO改为LRU,并增大主存容量(页数),一般可使命中率有较大提高。

(5)FIFO改为LRU,并增大页面大小,如果原来页面很小,则会使命中率显著上升,如果原来页面很大,则会使命中率下降。

11.采用组相联映象的Cache存储器,Cache为1KB,要求Cache的每一块在一个主存周期能从主存取得。

主存模4交叉,每个分体宽为32位,总容量为256KB。

用按地址访问存储器构成相联目录表实现主存地址到Cache地址的变换,并约定用4个外相等比较电路。

请设计此相联目录表,求出该表之行数、总位数及每个比较电路的位数。

设Cache地址中的组块号为s,相联目录表的行数是2^(13-s),总位数是(8+2s)*2^(15-s),每个比较电路的位数为8+s。

剖析:

在一个主存周期主存能访问到的字节数为mW=4*32/8=16(Byte)。

要求Cache的每一块在一个主存周期能从主存取得,所以,Cache中每块的块字数不能大于16Bytes。

为了加速调块,一般让每块的大小等于在一个主存周期主存能访问到的字数,即16Bytes。

设Cache地址中的组块号为s,相联目录表的行数=Cache地址的组数Q=Cache容量/(每组块数*每块大小)=1KB/(S*4*32)=2^13/(2^s*2^7)=2^(6-s)。

主存块数/Cache块数=256=2*8,所以,主存地址中的区号nd=8。

每个比较电路的位数=nd+s'

=nd+s=8+s。

相联目录表的总位数=表中子目录表的个数*每个子目录表的位数*相联目录表的行数=4*(nd+s'

+s)*Q=4*(8+2s)*2^(6-s)=(8+2s)*2^(8-s)。

note:

若认为相等比较电路的个数=组块数,则相联目录表的行数=2^4,每个比较电路的位数=10,相联目录表的总位数=12*2^6。

12.有一个Cache存储器。

主存共分8个块(0~7),Cache为4个块(0~3),采用组相联映象,组块数为2块,替换算法为近期最少使用算法(LRU)。

(1)画出主存、Cache地址的各字段对应关系(标出位数)图;

(2)画出主存、Cache空间块的映象对应关系示意图;

(3)对于如下主存块地址流:

1,2,4,1,3,7,0,1,2,5,4,6,4,7,2,如主存中容一开始未装入Cache中,请列出Cache中各块随时间的使用状况;

(4)对于(3),指出块失效又发生块争用的时刻;

(5)对于(3),求出此期间Cache的命中率。

(1)主存地址、Cache地址的各字段的位数及其对应关系如下图所示

(2)主存块、Cache块的映象对应关系如下图所示

(3)Cache中各块随时间的使用状况如下图所示。

图中标*号的是候选替换块的块号,H:

命中;

R:

替换;

L:

失效。

(4)发生块失效又发生块争用的时刻有6、7、9、10、11、12、14、15。

(5)Cache的块命中率Hc=3/15=0.2。

由于主存块、Cache块之间存在上述的映象对应关系,主存的第0、1、4、5块只能映象装入或替换物理Cache的第0、1块;

主存的第2、3、6、7块只能映象装入或替换物理Cache的第2、3块。

13.采用组相联映象,LRU替换算法的Cache存储器,发现等效访问速度不高,为此建议:

(1)增大主存容量;

(2)增大Cache的块数(块的大小不变);

(3)增大组相联组的大小(块的大小不变);

(4)增大块的大小(组的大小和Cache总容量不变);

(5)提高Cache本身器件的访问速度。

(1)增大主存容量对Cache的访问时间ta基本不影响,从而对Cache的等效访问速度基本不影响。

(2)增大Cache的块数(块的大小不变)一般将使Cache的命中率Hc上升,从而使ta下降,从而提高Cache的等效访问速度。

(3)增大组相联组的大小(块的大小不变)一般将使Cache的命中率Hc上升,从而使ta下降,从而提高Cache的等效访问速度。

(4)增大块的大小(组的大小和Cache总容量不变)一般将使ta下降,从而提高Cache的等效访问速度。

(5)提高Cache本身器件的访问速度一般将缩短ta,从而提高Cache的等效访问速度。

14.你对Cache存储器的速度不满,于是申请到一批有限的经费,为能发挥其最大经济效益,有人建议你再买一些同样速度的Cache片子以扩充其容量;

而另有人建议你干脆去买更高速的Cache片子将现有的低速Cache片子全部换掉。

你认为哪种建议可取?

你如何做决定?

Cache本身的速度与容量都会影响Cache存储器的等效访问速度。

如果对Cache存储器的等效访问速度不满,需要改进的话,就要作具体分析,看看现在Cache存储器的等效访问速度是否已接近于Cache本身的速度。

如果差得较远,说明Cache的命中率低,应从提高Cache命中率着手,包括调整组的大小、块的大小、替换算法以及增大Cache容量等。

如果Cache存储器的等效访问速度已经非常接近于Cache本身的速度还不能满足需要,就应该更换更高速的Cache片子。

下面

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 计算机系统 结构 课后 答案 unit4

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx