六人抢答器设计Word下载.docx

六人抢答器设计Word下载.docx

- 文档编号:19107655

- 上传时间:2023-01-03

- 格式:DOCX

- 页数:23

- 大小:547.52KB

六人抢答器设计Word下载.docx

《六人抢答器设计Word下载.docx》由会员分享,可在线阅读,更多相关《六人抢答器设计Word下载.docx(23页珍藏版)》请在冰豆网上搜索。

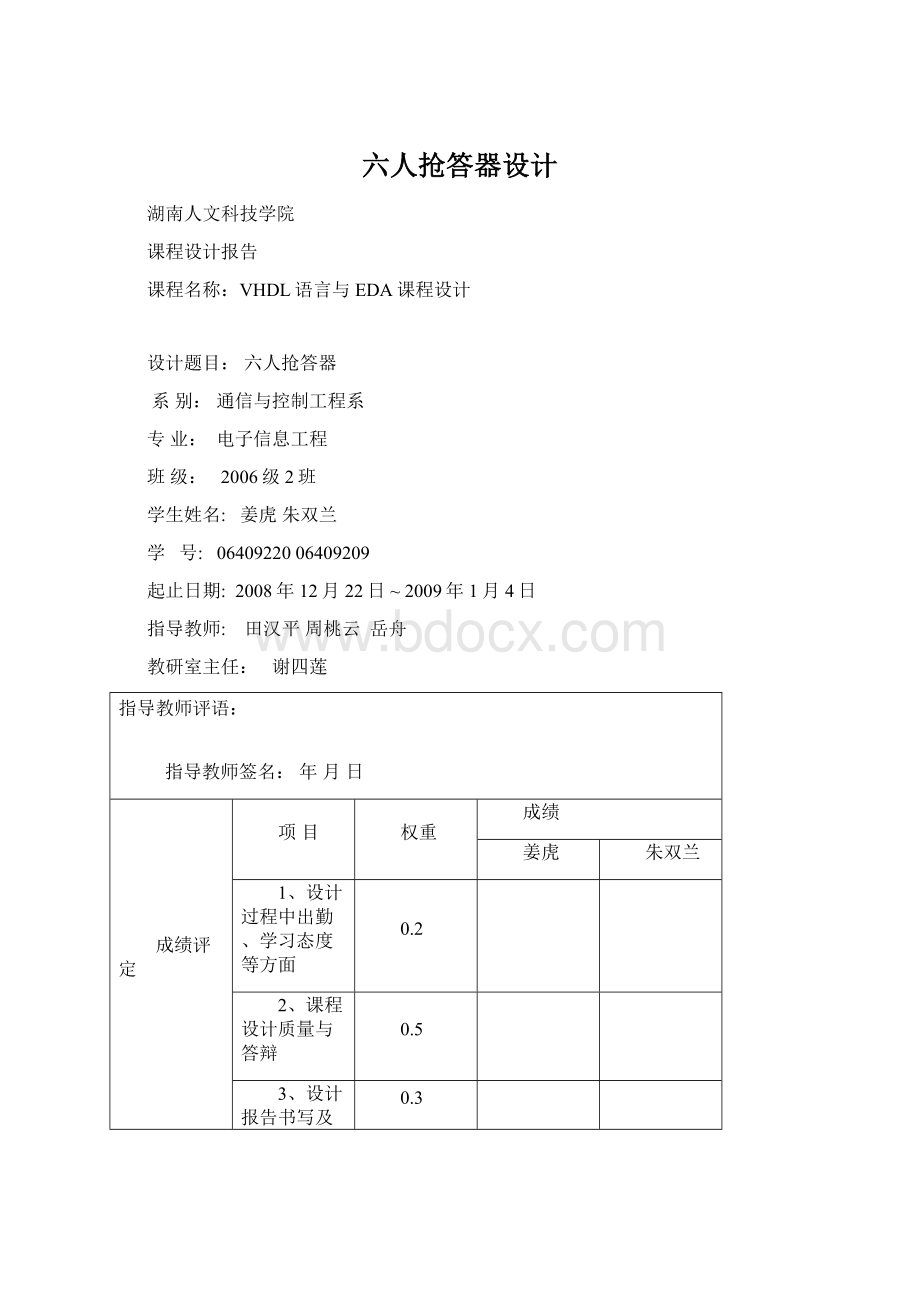

0.5

3、设计报告书写及图纸规范程度

0.3

总成绩

教研室审核意见:

教研室主任签字:

教学系审核意见:

主任签字:

年月日

摘要

本次设计在EDA开发平台QUARTUSⅡ6.0上利用VHDL语言设计六人抢答器电路。

电路中设有六个抢答键,可供六人同时抢答;

我们利用一个二十进制计数器,将其输入频率设定为一赫兹,成功实现了二十秒倒计时的功能;

我们利用VHDL语言中的IF和CASE语句结合空操作语句NULL实现开始抢答与超前抢答的区别;

各个模块配以一时钟频率由蜂鸣器输出可实现抢答成功、超前抢答犯规、超时抢答等各种情况的报警效果;

本设计采用的是杭州康芯电子有限公司生产的GW48系列/SOPC/EDA实验开发系统,FPGA目标芯片型号为Altera公司的Cyclone系列中的EPIC6Q240C8。

芯片配置成功后锁定引脚下载即可进行硬件测试:

选择实验电路结构图NO.5,使CLK1与CLKOCK5相接(接受1024Hz时钟频率),CLK与CLOCK0相接(接受1Hz时钟频率),报警输出接SPEAK,六位选手分别对应实验箱上的1~6键,键7为抢答开始键,当其未按下就进行抢答则为超前犯规,按下后二十秒倒计时开始,选手进行抢答,按实验箱上的复位键则可重新开始下一轮的抢答。

关键词:

六人抢答器;

数码显示;

信号封锁;

犯规报警。

六人抢答器

设计要求

抢答台数为6;

具有抢答开始后20秒倒计时,20秒倒计时后六人抢答显示超时,并报警;

能显示超前抢答台号并显示犯规报警;

系统复位后进入抢答状态,当有一路抢答按键按下,该路抢答信号将其余各路抢答信号封锁,同时铃声响起,直至该路按键松开,显示牌显示该路抢答台号。

1总体设计方案论论证与对比

1.1方案一

该方案方框图如图1:

在该方案中,由二十秒倒计时模块、抢答鉴别模块、锁存器模块等模块组成[3]。

蜂鸣器和数码管分别起报警和显示台号的作用。

但该方案中的数码管显示是由七段显示器的形式来显示台号的,由于实验箱电路结构与按键数目的限定,使得我们没有采用该方案。

1.2方案二

该方案方框图如图2:

此方案中整个电路主要由超前抢答判别模块、二十秒倒计时模块、抢答成功按键模块、抢答报警模块四个模块组成[4]。

其台号的显示都是将信号送入译码器译码之后再由数码管显示出来,结合前面六位选手的按键及开始键可得实验箱上模式5的电路结构满足硬件测试的要求。

所以我们选定该方案来进行我们这次的课程设计。

2顶层电路VHDL程序设计

顶层电路VHDL程序如下

USEieee.std_logic_1164.all;

LIBRARYwork;

ENTITYjinaghuIS

port(rst:

INSTD_LOGIC;

--抢答开始键

clk:

--计数器时钟输入

clk1:

--蜂鸣器时钟输入

AIN:

INSTD_LOGIC_VECTOR(6downto1);

--选手按键

speak:

OUTSTD_LOGIC;

--蜂鸣器

cout:

--超时抢答报警

shuma:

OUTSTD_LOGIC_VECTOR(3downto0);

--抢答成功显示台号数码管

shuma1:

shuma2:

OUTSTD_LOGIC_VECTOR(3downto0);

shuma3:

shuma4:

shuma5:

shuma6:

OUTSTD_LOGIC_VECTOR(3downto0));

ENDjinaghu;

ARCHITECTUREbdf_typeOFjinaghuIS

componentanjian--元件U1例化

PORT(rst:

AIN6:

shuma:

endcomponent;

componentchaoqian--元件U2例化

PORT(clk1:

rst:

shuma1:

shuma3:

OUTSTD_LOGIC_VECTOR(3downto0));

componentdaojishi--元件U3例化

PORT(clk:

INSTD_LOGIC_VECTOR(3downto0);

OUTSTD_LOGIC);

componentqiangdabao--元件U3例化

signalSYNTHESIZED_WIRE_17:

STD_LOGIC_VECTOR(3downto0);

signalSYNTHESIZED_WIRE_1:

STD_LOGIC;

signalSYNTHESIZED_WIRE_2:

signalSYNTHESIZED_WIRE_3:

signalSYNTHESIZED_WIRE_4:

signalSYNTHESIZED_WIRE_18:

signalSYNTHESIZED_WIRE_19:

signalSYNTHESIZED_WIRE_20:

BEGIN

shuma3<

=SYNTHESIZED_WIRE_17(3);

shuma2<

=SYNTHESIZED_WIRE_17

(2);

shuma1<

=SYNTHESIZED_WIRE_17

(1);

shuma0<

=SYNTHESIZED_WIRE_17(0);

shuma13<

=SYNTHESIZED_WIRE_18(3);

shuma12<

=SYNTHESIZED_WIRE_18

(2);

shuma11<

=SYNTHESIZED_WIRE_18

(1);

shuma10<

=SYNTHESIZED_WIRE_18(0);

shuma23<

=SYNTHESIZED_WIRE_19(3);

shuma22<

=SYNTHESIZED_WIRE_19

(2);

shuma21<

=SYNTHESIZED_WIRE_19

(1);

shuma20<

=SYNTHESIZED_WIRE_19(0);

shuma33<

=SYNTHESIZED_WIRE_20(3);

shuma32<

=SYNTHESIZED_WIRE_20

(2);

shuma31<

=SYNTHESIZED_WIRE_20

(1);

shuma30<

=SYNTHESIZED_WIRE_20(0);

b2v_inst:

anjianPORTMAP(rst=>

rst,AIN6=>

AIN,shuma=>

SYNTHESIZED_WIRE_17);

--参数传递映射语句

b2v_inst1:

chaoqianPORTMAP(clk1=>

clk1,rst=>

rst,AIN6=>

AIN,

speak=>

SYNTHESIZED_WIRE_1,

shuma1=>

SYNTHESIZED_WIRE_18,

shuma2=>

SYNTHESIZED_WIRE_19,

shuma3=>

SYNTHESIZED_WIRE_20,

shuma4=>

shuma4,

shuma5=>

shuma5,

shuma6=>

shuma6);

b2v_inst2:

daojishiPORTMAP(clk=>

clk,clk1=>

rst,

shuma=>

SYNTHESIZED_WIRE_17,speak=>

SYNTHESIZED_WIRE_3,cout=>

cout);

b2v_inst3:

qiangdabaoPORTMAP(rst=>

rst,clk1=>

clk1,AIN6=>

SYNTHESIZED_WIRE_2);

SYNTHESIZED_WIRE_4<

=SYNTHESIZED_WIRE_1ORSYNTHESIZED_WIRE_2ORSYNTHESIZED_WIRE_3;

speak<

=NOT(SYNTHESIZED_WIRE_4);

END;

3单元模块程序设计

根据顶层原理图,共分为anjian模块、chaoqian模块、daojishi模块、qiangdabao模块这四个模块。

其中anjian模块的功能是锁定抢答成功的选手的台号并显示,chaoqian模块可将超前抢答了的选手台号显示出来并伴随报警,daojishi模块进行二十秒倒计时并显示超时报警,qiangdabao模块主要是为抢答成功之后提供报警功能[2]。

3.1二十秒倒计时模块

3.1.1二十秒倒计时模块原理图

3.1.2二十秒倒计时模块VHDL程序设计[1]

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitydaojishiis

port(clk,clk1,rst:

instd_logic;

shuma:

inoutstd_logic_vector(3downto0);

--主数码管

speak:

outstd_logic;

cout:

inoutstd_logic);

--进位,可用于超时显示

enddaojishi;

architectureoneofdaojishiis

begin

process(clk,rst)

variablecqi:

std_logic_vector(7downto0);

if(rst='

1'

)and(clk'

eventandclk='

)then

ifcqi<

30thencqi:

=cqi+1;

elsecqi:

=(others=>

'

0'

);

endif;

if(cqi>

20)and(cqi<

23)thencout<

='

;

elsecout<

if(cout='

)and(shuma="

0000"

)and(rst='

)thenspeak<

=clk1;

--无人抢答,超时报警

elsespeak<

endif;

endprocess;

endone;

3.2抢答成功选手按键模块

3.2.1抢答成功选手按键模块原理图

3.2.2抢答成功选手按键模块VHDL程序设计

entityanjianis

port(rst:

AIN6:

instd_logic_vector(6downto1);

--六位选手抢答输入

outstd_logic_vector(3downto0));

endanjian;

architectureoneofanjianis

process(AIN6,rst)

variabletemp:

std_logic_vector(3downto0);

begin

ifrst='

then

ifAIN6="

000000"

thentemp:

="

elsifAIN6="

000001"

thentemp:

0001"

;

--1

elsifAIN6="

000010"

0010"

--2

elsifAIN6="

000100"

0011"

--3

001000"

0100"

--4

010000"

0101"

--5

100000"

0110"

--6

elsenull;

shuma<

=temp;

3.3超前抢答犯规模块

3.3.1超前抢答犯规模块原理图

3.3.2超前抢答犯规模块VHDL程序设计

entitychaoqianis

port(clk1,rst:

instd_logic_vector(6downto1);

shuma1,shuma2,shuma3:

outstd_logic_vector(3downto0);

shuma4,shuma5,shuma6:

endchaoqian;

architectureoneofchaoqianis

signalabc:

std_logic_vector(6downto0);

abc<

=rst&

AIN6;

--rst为0,抢答未开始

process(abc)

variabletepm:

caseabcis

when"

0000001"

=>

shuma1<

shuma2<

shuma3<

shuma4<

shuma5<

shuma6<

speak<

0000010"

0000100"

0001000"

0010000"

0100000"

0000011"

0000101"

0001001"

0010001"

0100001"

0000110"

0001010"

0010010"

0100010"

0001100"

0010100"

0100100"

0011000"

0101000"

0110000"

0000111"

0001011"

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 六人 抢答 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx