电脑主机板的系统结构Word下载.docx

电脑主机板的系统结构Word下载.docx

- 文档编号:18999891

- 上传时间:2023-01-02

- 格式:DOCX

- 页数:23

- 大小:864.29KB

电脑主机板的系统结构Word下载.docx

《电脑主机板的系统结构Word下载.docx》由会员分享,可在线阅读,更多相关《电脑主机板的系统结构Word下载.docx(23页珍藏版)》请在冰豆网上搜索。

这份教材目的是让大家学习后能达到主机板功能分析的境界,所以大家必须对主机板要有很全面的认识,以上一些主机系统的片面知识有没有引起你的兴趣呢?

如果有的话,请准备接受大容量的知识灌输和长时间的烦闷吧!

这是掌握计算机运作内幕的唯一途径,希望你成功(记得九十步与一百步之差)。

祝你成功!

能感受到计算机和你是多幺接近甚至感觉到它处理每一个事件时的脉搏的跳动。

关于计算机系统分析介绍

一.计算机的发展:

相信大家一定听过不少关于这方面的东西,但是这里还是要老调重弹一下,让我们用比较技术一点的眼光从另一个角度去看看。

计算机的诞生是为了战争获胜的需要,并经历了慢慢向民用的过渡。

我们更关心的是它的发展过程,有什幺进展?

具体功能扩展在那里。

那些地方没有变化。

计算机经历了从8位机到现在的32位机,速度达到主频1GMHz,,基频可以达到133MHz甚至200MHz,这些数据意味着速度不断提升,但是有没有仍然保持不变的呢?

有:

SIO,PIO,ISA插槽等标准接口还在使用,也就是说它的控制信号和数据型号和地址信号在这个功能框图里都没有变化。

我们需要关注的另一个方面是:

计算机的发展并不是简单的工作频率的提升,CPU内在的计算指令集也在不断的改变和扩展,控制型号数量也在扩展,同时为了支持更大容量的内存和硬盘,更有效率的管理他们,相应的硬件电路应运而生。

最后总结一下,计算机发展到现在,既有不变的地方,但更多是改变:

寻址能力,资源管理能力,计算新领域支持等等。

从而引发了地址线和数据线的扩充以及工作频率的提升,为了支持这些,控制信号相应做出扩展。

二.如何去学习计算机系统(硬件)

针对以上对计算机发展的了解,在学习中就可以因应做出方案:

首先将计算机结构按功能若干方框,然后标示出比较稳定的规格,并区分出新增的功能框图。

对各种功能框图作认真学习,即使做到了这一步你还未能自如的对功能问题做到出色的分析,因为还有更难和更具挑战的目标:

1.各功能块是如何联系起来的.2.不同的指令执行时,三总线是如何动作的.3.主机系统加电Boot时,主机系统由那些动作,各功能块是如何响应加电自检的。

这些多做到了,那幺,祝贺你---你已经达到主机系统分析专业工程人员的水平了。

第一部分组成主机系统的硬体成员

2.北桥芯片

3.内存条

4.显示卡

5.南桥芯片

6.超级输入/输出控制芯片

7.硬盘

8.CD-ROM

9.软盘驱动器

10.电源供应器

第二部分主机系统可以划分为多个功能方框图

1.RESET电路

2.时钟电路

3.电源处理电路

4.HostBus接口(CPU信号线)

5.AGP显示卡接口

6.内存管理接口

7.PCI接口

8.PCI声卡电路原理

9.USB接口原理

10.CMOS路原理

11.ISA接口

12.中断申请及允许过程

13.串行接口电路

14.并行接口电路

15.PS/2键盘接口电路

16.PS/2鼠标接口电路

第三部分主机系统Boot机的动作内容及顺序

1.Boot机成功的前提条件

2.Boot机过程检查的项目

3.Boot机过程中一些特殊的可作参考的数据

第四部分DEBUGcard使用简介

第五部分一些控制信号线的描述及说明(用VIA694X;

VIA686A举例说明)

Hostbussignal

AGPbussignal

PCIbussignal

ISAbussignal

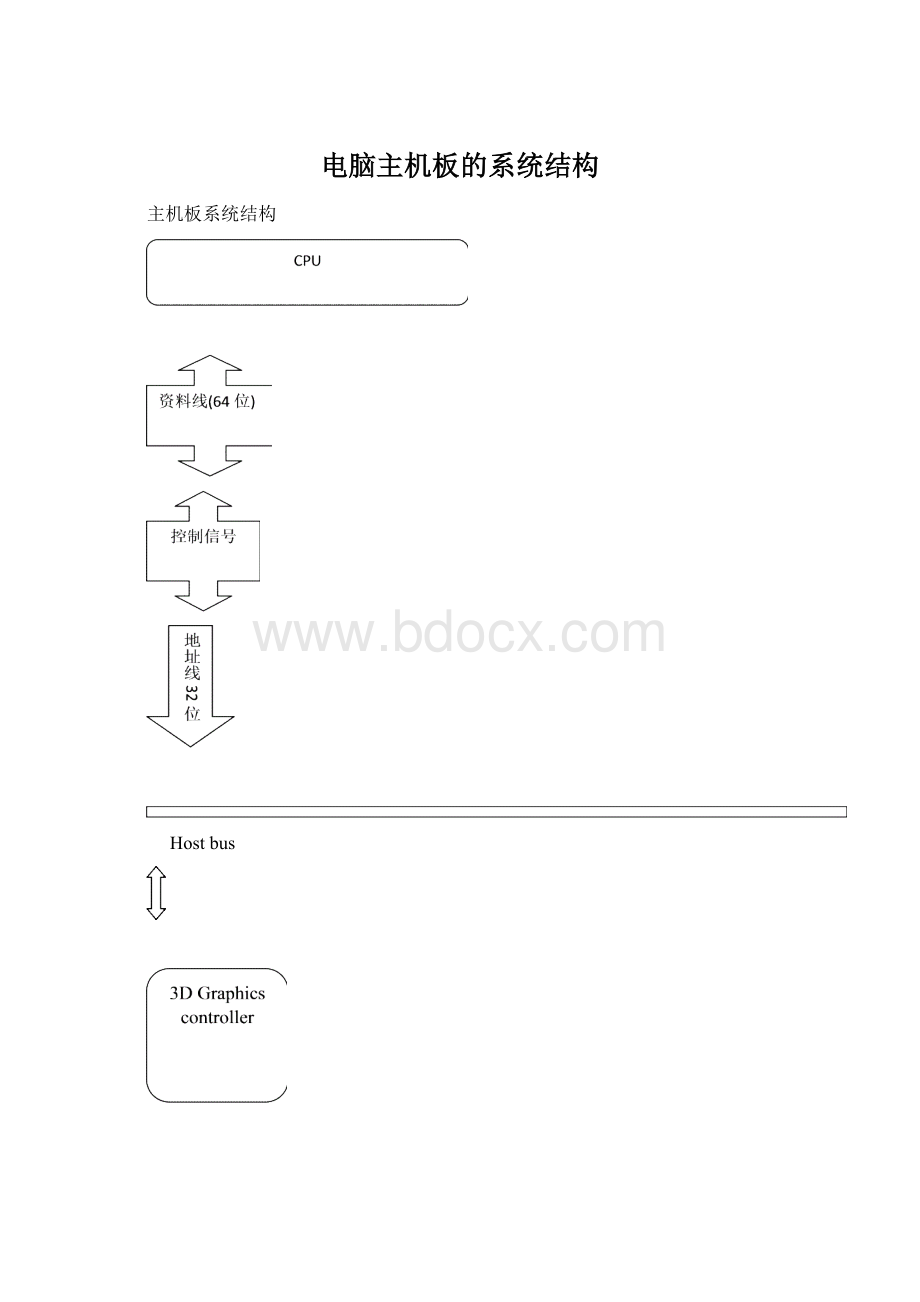

CPU的详细描述是centralprocessingunit,中央处理器。

它包括四种信号线:

(一)电源

(二)其它线(三)数据线,地址线(四)控制线

(一)电源:

1.VID[4:

0]电压判定。

有五个脚用于指定CPUcore所需电压voltageidentification.

Processor

VID4

VID3

VID2

VID1

VID0

VCC

01111

1

1.80

1.85

1.90

1.95

2.00

2.05

No

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.9

3.0

3.1

3.2

3.3

3.4

3.5

Note:

1.0=processorpinconnectedtoVss

2.1=Openonmicroprocessor,maybepulleduptoTTLVihonbaseboard.

3.toensureasystemisreadyforPentiumIIIprocessor.

PIIICPU有27个Vcc和30个Vss(接地)输入。

Vcc(core)heVccl2共有19个输入脚。

CPU所希望的工作电压和L2Cache所希望的工作电压是不同的,

3个V_cc_L2inputvoltage:

3.3V用于提供给L2Cache的TagRAM和BSRAM

4个V_TTinputvoltage:

1.5V(用于提供一个AGTL+终止电压到处理器

GTL–gunningtransceiverlogic

AGTL—assistedgunningtransceiverlogic

VRM–Voltageregulationmodule

Have27Vcc(power)and30Vss(ground)input.

2.有关稳定的方面

由于大量使用晶体管而且很高的内部频率,处理器将会在轻载和满载之间产生大的涌动的有效(平均)电流。

如果涌动减弱不力,就会引起供应电压值在标称值下浮动。

设计主机板时要注意提供给处理器的电压要满足规定要求

3.钟控制和低能量状态

PIIICPU允许使用AUTOHALT(自动暂停),停止响应,睡眠,深度睡眠状态从而停止处理器内部局部时钟来减少能量的损耗(达到节能的目的)

1标准状态----状态1NORMALSTATE----STATE1

这是处理器的标准操作状态。

2自动暂停省电状态----状态2

当处理器执行HALT指令时,AUTOHALT作为低能量状态开始。

在SMI#,BINIT#,INIT#,LINE[1:

0](NMI,INTR)变化的时候处理器会转换为标准模式。

RESET信号将导致处理器马上进行自身的初始化。

在AUTOHALT状态下FLUSH#信号会被有效输入,而且处理器会返回到AUTOHALT状态。

在AUTOHALTPOWERDOWN状态,处理器能够产生一个STPCLK#信号。

当系统不能确定STPCLK#中断,处理器将返回到HALT状态。

3STOP-GRANTSTATE----状态3

当STPCLK#信号被确认为真,处理器会进入STOP-GRANTSTATE状态。

在STOP-GRANTSTATE状态下,BINIT#和FLUSH#信号无效。

RESET信号将使处理器立即自身初始化,但处理器仍然处于STOP-GRANTSTATE状态。

在SLP#信号有效时,将转入睡眠状态—SLEEPSTATE.

在STOP-GRANTSTATE状态下,处理器会锁住SMI#,INIT#和LINT[1:

0],而且只有当处理器返回到标准状态时才能起作用。

4HALT/Grant-Snoopstate---状态4

5睡眠状态SLEEPSTATE------------状态5

睡眠状态是非常低功耗的状态,在此状态下,处理器维持其内容,维持Phase-lockedloop,并且停止所有内部时钟。

睡眠状态只能从STOP-GRANTSTATE进入。

一旦在STOP-GRANT状态下,SLP#信号线被确认有效将令处理器进入睡眠状态。

SLP#信号在标准状态和AUTOHALT状态下不起作用(不被识别)。

在睡眠状态下,处理器不能够响应监测处理事件或锁住中断信号,当处理器在睡眠状态下,没有转变或者确认(SLP#,RESET#信号除外)会系统总线被允许(接受)。

当处理器在睡眠状态下RESET#信号被驱动为有效,而且保持RESET#脚所规定之规格,这样处理器会复位自己,同时忽略通过STOP-GRANT状态的转变。

当RESET#在处理器睡眠状态下被驱动为有效,并在RESET#信号确实被响应,处理器已正确执行了RESET#序列后SLP#和STPCLK#信号将市区作用。

当处理器在睡眠状态时,它可以进入最低功耗状态,就是深度睡眠状态,,通过停止BCLK#输入来实现。

一旦进入睡眠状态或深度睡眠状态,如果其它异步一同总现有事件发生SLP#信号脚将被定义为无效

6深度睡眠状态

深度睡眠状态是处理器能进入的功耗最低的状态,同时会存储前后记录。

通过停止BCLK输入来进入深度睡眠状态(在SLP#信号有效斌进入睡眠状态之后)。

当BCLK停止后处理器马上进入深度睡眠状态,建议在深度睡眠状态时保持BCLK输入为低电平。

要在进入睡眠状态,必须重新提供BCLK信号。

7时钟控制器

处理器向L2(二级)Cache(缓冲器)提供时钟信号,在AUTOHALTPowerDown和Stop-Grant状态,处理器会执行系统总线检测。

在AUTOHALTPowerDown和Stop-Grant状态下,处理器不会停止对L2Cache提供时钟。

进入HALT/GRANTJ检测状态后,将允许检测L2Cache,就像标准状态一样。

当处理器在睡眠状态或深度睡眠状态下,它将不响应中断或者检测处理。

在睡眠状态下,供应L2Cache的时钟不会停止。

在深度睡眠状态下,供应L2Cache的时钟奖杯停止,供应给L2Cache的时钟在送给处理器的内部时钟机制稳定之后会重新启动(也就是说处理器已经重新进入睡眠状态)。

在AUTOHALTPowerDown和STOP-GRANT状态下,PICCLK信号不应该被停止。

但PICCLK信号可以在睡眠状态或者深度睡眠状态下被停止,当从深度睡眠状态向睡眠状态转变时,PICCLK和BCLK信号必须重新启动(或理解为重新提供)。

Symbol

Parameter

CoreFreq

Min

Typ

Max

Unit

VCCCORE

VCCforprocessorcore

2.00V

V

2,3,4,5

VCCL2

VCCforsecondlevelcache

3.135

3.465

3.3V±

5%9

VTT

AGTL+busterminationvoltage

1.365

1.50

1.635

1.5±

9%6

BaseboardToleranceStatic

ProcessorcorevoltagestatictolerancelevelatSC242pins

–0.070

0.070

BaseboardToleranceTransient

ProcessorcorevoltagetransienttolerancelevelatSC242pins

–0.140

0.140

VCCCORETolerance,Static

Processorcorevoltagestatictolerancelevelatedgefingers

–0.085

085

2,8

VCCCORETolerance,Transient

Processorcorevoltagetransienttolerancelevelatedgefingers

–0.170

0.170

ICCCORE

ICCforprocessorcore

450MHZ500MHZ

14.516.1

AA

2,3,10,112,3,10,11

ICCL2

ICCforsecondLevelCache

1.1.12

2,9,102,9,10

IVTT

Terminationvoltagesupplycurrent

A

12

Ignt

ICCSTOP-GRANTforprocessorcore

1.21.4

2,10,13

IGNntL2

ICCSTOP-GRANTforsecondCache

0.1

2,9,10

ISLP

ICCsleepforprocessorcore

0.800.90

2,102,10

ISLPL2

ICCsleepforsecondlevelCache

IDSLP

ICCdeepsleepforprocessorcore

0.5

IDSLPPL2

ICCdeepsleepforsecondlevelCache

DICCcore/dt

Powersupplycurrentslewrate

20

A/us

2,14,15,16

DICCL2/dt

L2CachePowersupplycurrentslewrate

14,15,16

DICCVTT/dt

Terminationcurrentslewrate

VCC5

5voltagepowersupply

4.75

5

5.25

5V+_5%16,17

ICC5

ICCfor5Vsupplyvoltage

1.0

17

(二)其它线

1.RESERVEDpins:

所有保留线必须保持断开,如果连接到Vcccore,Vccl2,Vss或者其它信号线将会导致组件坏掉或者与以后的处理器不兼容

2.TESTHIpins:

所有TESTHI脚必须通过100欧姆电阻连接到2.5V

3.PICCLKpins:

PICCLK必须用有效的输入时钟驱动,即使APIC未被使用时PICD[1:

0]线也必须被上拉到2.5V,并且每条APIC数据线必须使用各自独立的上拉电阻。

未使用的AGTL+信号应该保持断开,为使用的低电平有效的CMOS输入应该通过一个电阻连接到2.5V.为使用的高电平有效输入应该通过电阻连到地线(Vss),为使用的输出信号应该保持断开。

上拉电阻推荐使用:

~10K(PICD例外)。

下拉电阻推荐使用~1K.

4.EMIpins:

通过0欧姆电阻接到基板地或底板地。

0欧姆电阻接到底板地应考虑就近原理和为使阻抗最低。

同步和异步系统总线信号:

所有的AGTL+信号都是与BCLK同步的,所有的CMOS,APIC,CLOCK,TAP信号都是与BCLK异步的。

所有的APIC都是与PICCLK同步的,所有的TAP信号都是与TCK同步的。

系统总线频率选择信号BSEL0(通常认为100MHz/66MHz):

当BSEL0为低电平时,系统总线频率选择66MHz,为高时系统选择100Mhz的频率。

Phase-lockedloop-----PLL

ThePICCLK(APICClock)signalisaninputclocktotheprocessorandcorelogicorI/OAPICwhichisrequiredforoperationofallprocessors,corelogic,andI/OAPICcompinentsontheAPICbus.---------------PICCLK

BurstpipelinedsynchronousstaticRAM-----------BSRAM

TAGRAM

ThePIIIprocessorsystembususeavariantofGTL+signalingtechnologycalledassistedGunningTransceiverLogic(AGTL+)signalingTechnology.ThePIIIprocessorhasadedicatedL2Cachebus,thusmaintainingthedualindependentbusarchitecturetodeliverhighbusbandwidthandhighperformance.

PIII能支持4GB内存。

备注:

(三)数据线,地址线

数据线(Datasignals)

D0~D63双向传输,低电平有效

地址线(Addresssignals)

A0~A35单向传输,由CPU送出,低电平有效。

(四)控制线

AGTLInput

BPRI#,BR1#,DEFER#,RESET#,RS[2:

0]#,RSP#,TRDY#

AGTLOutput

PRDY#

AGTLI/O

A[35:

3]#,ADS#,AERR#,AP[1:

0],BERR#,BINIT#,BNR#,BP[3:

2]#,BPM[1:

0]#,BR0#,D[63:

0]#,DBSY#,DEP#[7:

0],DRDY#,HIT#,HITM#,LOCK#,REQ[4:

0]#,RP#

CMOSInput

A20M#,FLUSH#,IGNNE#,INIT#,LINT0/INTR,LINT1/NMI,PREQ#,PWRGOOD,SMI#,SLP#,STPCLK#

CMOSOutput

FERR#,IERR#,THERMTRIP#

SystemBusClock

BCLK

APICClock

PICCLK

APICI/O

PICD[1:

0]

TAPInput

TCK,TDI,TMS,TRST#

TAPOutput

TDO

Power/Other

VCCcore,VCCL2,VCC5,VID[4:

0],VTT,VSS,SLOTOCC#,THERMDP,THERMDN,BSEL[1:

0],EMI,TESTHI,Reserved

备注:

1.这些信号工作规格是在2.5V电压

信号说明:

名称

类型

描述

3]

I/O

地址线A[35:

0]定义了2的36次方物理内存地址空间,当ADS#信号有效时,这些脚传送处理的地址。

当ADS#信号无效时,这些脚传送处理类型的信息。

A[24:

35]#信号线通过AP1#奇偶信号作用得到奇偶保护,而A[23:

0]#信号线通过AP0#奇偶信号作用得到奇偶保护.

在RESET#信号转变时,处理器尝试(或者应理解为:

取样)A[35:

0]#测定POWER-ON(加电)的配置。

A20M#

I

如果A20M#信号生效,在内部Cache寻找某线之前,和在总线读/写处理之前处理器将屏蔽物理地址线第20位(A20#),A20M#有效时,地址将被限制在1M的范围,起到仿真8086处理器的作用,A20M#只在实模式下才生效.A20M#是异步信号。

无论如何,在I/O写指令后要重视这个信号,在相关写入总线的处理后,A20#必须随TRDY#的出现而生效。

ADS#

此信号出现就指出有效的处理地址在A[35:

3]#地址脚。

所有的总线服务会观测此信号的状态(有效时)而开始奇偶校验,协议检查,地址译码,内部监测,和延缓标识的回复来匹配联合新的事件处理的操作。

AERR#

地址奇偶错误。

此信号受到所有处理器总线代理的观测与驱动。

如果使用此信号,必须连接到处理器系统总线代理相应的脚。

在加电初始化的时候,AERR#是可选择是否侦测的,如果选择AERR#有效就会是当前事件处理异常中断。

AP[1:

地址奇偶信号。

这些AP[1:

0]信号随同ADS#,A

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 电脑 主机板 系统 结构

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx