50占空比三分频器的设计方法文档格式.docx

50占空比三分频器的设计方法文档格式.docx

- 文档编号:18962885

- 上传时间:2023-01-02

- 格式:DOCX

- 页数:9

- 大小:198.43KB

50占空比三分频器的设计方法文档格式.docx

《50占空比三分频器的设计方法文档格式.docx》由会员分享,可在线阅读,更多相关《50占空比三分频器的设计方法文档格式.docx(9页珍藏版)》请在冰豆网上搜索。

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

useieee.std_logic_arith.all;

entityfen3is

port

(clkin

:

in

std_logic;

--时钟输入

qout1

bufferstd_logic;

qout2

qout3

clkout:

out

std_logic

--占空比为1/2的三分频输出

);

endfen3;

architecturebehaveoffen3is

begin

qout3<

=qout1norqout2;

process(clkin)

begin

ifclkin'

eventandclkin='

1'

then

--在上升沿触发

qout1<

=qout3;

endif;

endprocess;

0'

--在下降沿触发

qout2<

process(qout3)

variabletem:

std_logic;

ifqout3'

eventandqout3='

--二分频

tem:

=nottem;

endif;

clkout<

=tem;

endprocess;

endbehave;

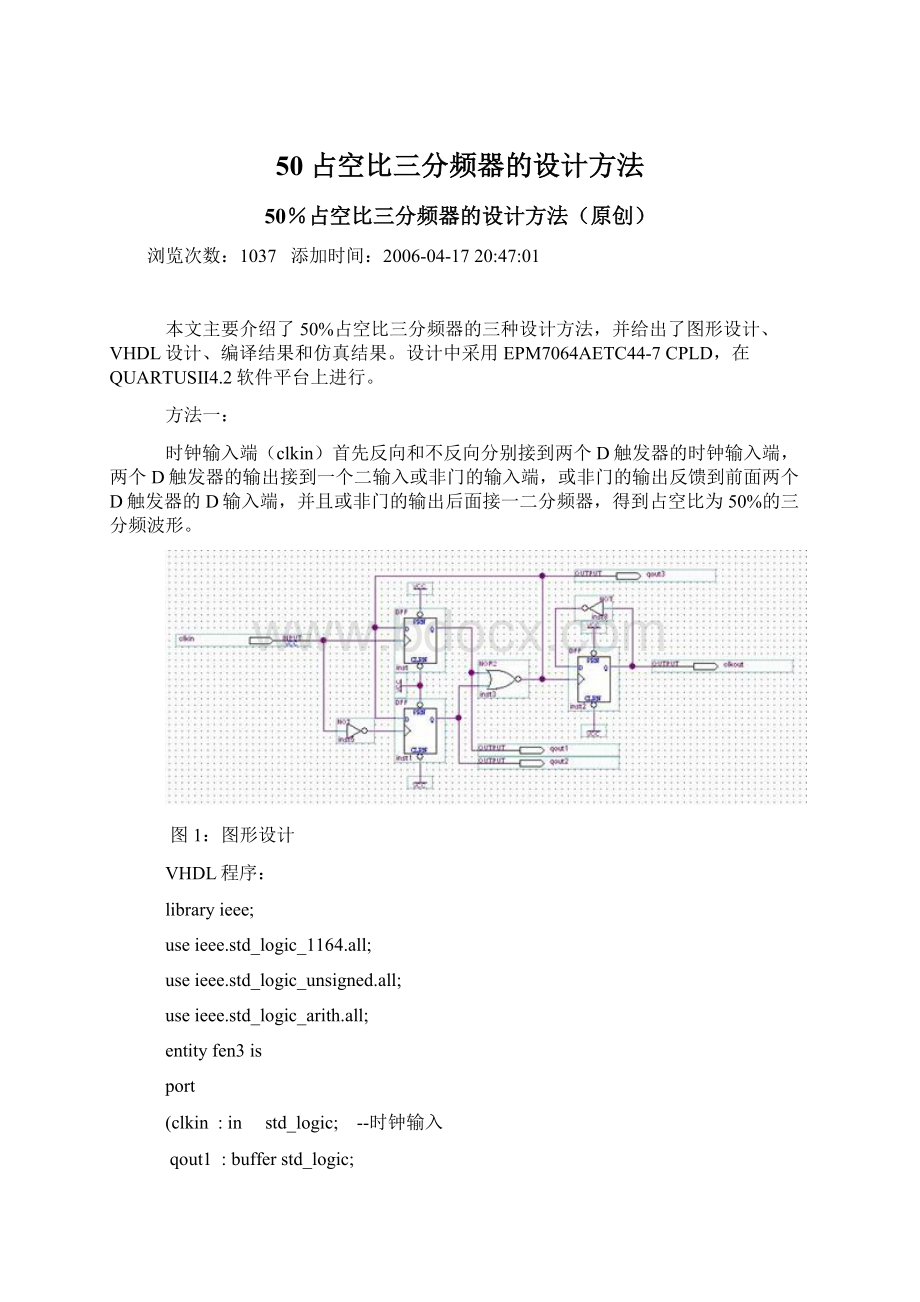

图2:

编译结果

图3:

仿真结果

方法二:

设计两个占空比为1/3的三分频器,分别在时钟输入端的上升沿和下降沿触发,然后两个分频器的输出接一个或门,得到占空比为50%的三分频波形。

图4:

entityfen3is

=qout1orqout2;

--占空比为1/3的三分频

variablecnt:

integerrange0to2;

--在上升沿触发

ifcnt=2then

cnt:

=0;

qout1<

='

;

else

cnt:

=cnt+1;

variablecnt:

begin

图5:

图6:

方法三:

设计一个占空比为50%的四分频器,四分频器的时钟输入端是由四分频器的输出端和时钟输入相异或后驱动的,四分频器的时钟输出端就是占空比为50%的三分频波形输出。

图7:

constantcounter_len:

integer:

=3;

--设置计数器的模

signalclk_tem:

=clkinxorclk_tem;

--反馈

process(qout1)

--四分频

integerrange0tocounter_len;

ifqout1'

eventandqout1='

ifcnt=counter_lenthen

ifcnt<

=1then

clk_tem<

endbehave;

图8:

图9:

以上介绍了三种设计50%占空比三分频器的方法,由以上看出,第三种设计方法,程序最简洁,占用宏单元最少,而且可以举一反三,很容易设计出其他奇数分频占空比为50%的分频器。

(作者:

徐刚)

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYOdd_Frenis

port(Clk:

instd_logic;

O

outstd_logic);

endOdd_Fren;

architecturebevofOdd_Frenis

signalO_r,O_d

std_logic_vector(1downto0):

="

00"

signalO_ro,O_do,O_x:

std_logic:

='

signalO_t

begin

P1:

PROCESS(Clk,O_r)

if(Clk'

eventandClk='

)then

caseO_ris

when"

01"

=>

O_ro<

O_r<

=O_r+1;

10"

whenothers=>

endcase;

endPROCESS;

P2:

PROCESS(Clk,O_d)

caseO_dis

O_do<

O_d<

=O_d+1;

O_x<

=O_roxorO_do;

P3:

PROCESS(O_x)

if(O_x'

eventandO_x='

O_t<

=notO_t;

O<

=O_t;

endbev;

-----------------------------------------------------------------------------------------------

ENTITYtst_Odd_Frenisend;

architecturetestoftst_Odd_Frenis

COMPONENTOdd_Frenis

port(Clk:

endCOMPONENT;

signalClk:

signalO

U0:

Odd_Frenportmap(Clk,O);

PROCESS

Clk<

waitfor50ns;

endtest;

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 50 分频器 设计 方法

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx