夏宇闻第五章文档格式.docx

夏宇闻第五章文档格式.docx

- 文档编号:18930758

- 上传时间:2023-01-02

- 格式:DOCX

- 页数:18

- 大小:202.43KB

夏宇闻第五章文档格式.docx

《夏宇闻第五章文档格式.docx》由会员分享,可在线阅读,更多相关《夏宇闻第五章文档格式.docx(18页珍藏版)》请在冰豆网上搜索。

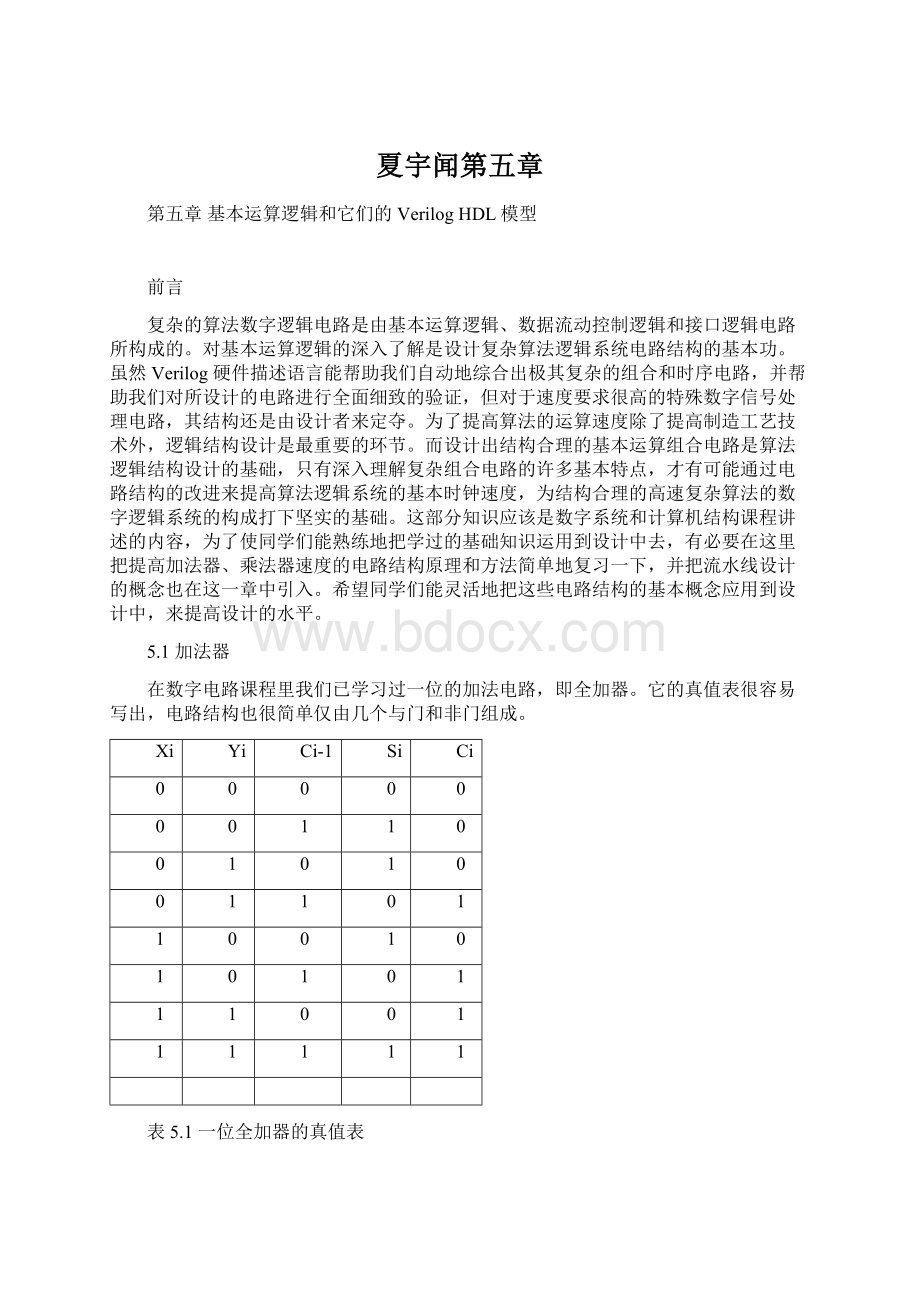

参考清华大学出版社出版的刘宝琴老师编写的《数字电路与系统》,可以很容易地写出超前进位形成电路的逻辑,在这里不再详细介绍。

在数字信号处理的快速运算电路中常常用到多位数字量的加法运算,这时需要用到并行加法器。

并行加法器比串行加法器快得多,电路结构也不太复杂。

它的原理很容易理解。

现在普遍采用的是Carry-Look-Ahead-Adder加法电路(也称超前进位加法器),只是在几个全加器的基础上增加了一个超前进位形成逻辑,以减少由于逐位进位信号的传递所造成的延迟。

下面的逻辑图表示了一个四位二进制超前进位加法电路。

同样道理,十六位的二进制超前进位加法电路可用四个四位二进制超前进位加法电路再加上超前进位形成逻辑来构成。

同理,依次类推可以设计出32位和64位的加法电路。

在实现算法时(如卷积运算和快速富里叶变换),常常用到加法运算,由于多位并行加法器是由多层组合逻辑构成,加上超前进位形成逻辑虽然减少了延迟,但还是有多级门和布线的延迟,而且随着位数的增加延迟还会积累。

由于加法器的延迟,使加法器的使用频率受到限制,这是指计算的节拍(即时钟)必须要大于运算电路的延迟,只有在输出稳定后才能输入新的数进行下一次运算。

如果设计的是32位或64位的加法器,延迟就会更大。

为了加快计算的节拍,可以在运算电路的组合逻辑层中加入多个寄存器组来暂存中间结果。

也就是采用数字逻辑设计中常用的流水线(pipeline)办法,来提高运算速度,以便更有效地利用该运算电路,我们在本章的后面还要较详细地介绍流水线结构的概念和设计方法。

我们也可以根据情况增加运算器的个数,以提高计算的并行度。

用VerilogHDL来描述加法器是相当容易的,只需要把运算表达式写出就可以了,见下例。

moduleadd_4(X,Y,sum,C);

input[3:

0]X,Y;

output[3:

0]sum;

outputC;

assign{C,Sum}=X+Y;

endmodule

而16位加法器只需要扩大位数即可,见下例:

moduleadd_16(X,Y,sum,C);

input[15:

output[15:

这样设计的加法器在行为仿真时是没有延时的。

借助综合器,可以根据以上VerilogHDL源代码自动将其综合成典型的加法器电路结构。

综合器有许多选项可供设计者选择,以便用来控制自动生成电路的性能。

设计者可以考虑提高电路的速度,也可以考虑节省电路元件以减少电路占用硅片的面积。

综合器会自动根据选项为你挑选一种基本加法器的结构。

有的高性能综合器还可以根据用户对运算速度的要求插入流水线结构,来提高运算器的性能。

可见在综合工具的资源库中存有许多种基本的电路结构,通过编译系统的分析,自动为设计者选择一种电路结构,随着综合器的日益成熟它的功能将越来越强。

然后设计者还需通过布局布线工具生成具有布线延迟的电路,再进行后仿真,便可知道该加法器的实际延时。

根据实际的延迟便可以确定使用该运算逻辑的最高频率。

若需要重复使用该运算器,则需要在控制数据流动的状态机中为其安排必要的时序。

5.2乘法器

乘法电路:

在数字信号处理中经常需要进行乘法运算,乘法器的设计对运算的速度有很大的影响。

本节讨论两个二进制正数的乘法电路和运算时间延迟问题以及怎样用VerilogHDL模型来表示乘法运算。

还将讨论当用综合工具生成乘法运算电路时,怎样来控制运算的时间延迟。

设两个n位二进制正数X和Y:

X:

Xn-1·

·

X1X0

Y:

Yn-1·

Y1Y0

则X和Y的乘积Z有2n位:

并且

式中YiX称为部分积,记为Pi,有

显然,两个一位二进制数相乘遵循如下规则:

0×

0=0;

1=0;

1×

1=1

因此YiXj可用一个与门实现,记Pi.j=YiXj

例:

两个四位二进制数X和Y相乘。

被乘数:

X3X2X1X0

×

)乘数:

Y3Y2Y1Y0

______________________________________________________________

Y0X3Y0X2Y0X1Y0X0

Y1X3Y1X2Y1X1Y1X0

Y2X3Y2X2Y2X1Y2X0

Y3X3Y3X2Y3X1Y3X0

__________________________________________________________

乘积:

Z7Z6Z5Z4Z3Z2Z1Z0

快速乘法器常采用网格形式的迭带阵列结构,图5.3示出两个四位二进制数相乘的结构图,图中每一个乘法单元MU的逻辑图如图5.4所示,即每一个MU由一个与门和一个全加器构成。

事实上,图5.3中第一行的每个MU可用一个与门实现,每一行最右边一个MU中的全加器可用半加器实现。

图5.3实现乘法的最长延时为1个与门的传输延时加上八个全加器的传输延时。

假设每个全加器产生和与产生进位的传输延时相同,并且均相当4个与门的传输延时,则图5.3逐位进位并行乘法器的最长延时为1+8×

4=33个门的传输延时。

为了提高乘法运算速度可以改为图5.5所示的进位节省乘法器(Carry-SaveMultiplier)。

图中用了一个三位的超前进位加法器,九个图5.4所示的乘法单元,七个与门。

显然,图5.5中第二行的乘法单元中全加器可改为半加器。

图5.5执行一次乘法运算的最长延时为1个与门的传输延时加上3个全加器的传输延时,再加上三位超前进位加法器的传输延时。

设三位超前进位加法器的传输延时为5个门的传输延时,则最长延时为1+3×

4+1×

5=18的传输延时。

节省乘法运算时间的关键在于每个乘法单元的进位输出向下斜送到下一行,故有进位节省乘法器之称。

根据加法器类似的道理,八位的二进制超前进位乘法电路可用两个四位二进制超前进位乘法电路再加上超前进位形成逻辑来构成。

同理,依次类推可以设计出16位、32位和64位的乘法电路。

用VerilogHDL来描述乘法器是相当容易的,只需要把运算表达式写出就可以了,见下例。

modulemult_4(X,Y,Product);

output[7:

0]Product;

assignProduct=X*Y;

而8位乘法器只需要扩大位数即可,见下例:

modulemult_8(X,Y,Product);

input[7:

这样设计的乘法器在行为仿真时是没有延时的。

借助综合器,可以根据以上VerilogHDL源代码自动将其综合成典型的乘法器电路结构。

设计者可以考虑提高速度,也可以考虑节省电路元件以减少电路占用硅片的面积。

综合器会自动根据选项和约束文件为你挑选一种基本乘法器的结构。

随着综合工具的发展,其资源库中将存有越来越多种类的基本电路结构,通过编译系统的分析,自动为设计者选择一种更符合设计者要求的电路结构。

然后设计者通过布局布线工具生成具有布线延迟的电路,再进行后仿真,便可精确地知道该乘法器的实际延时。

若需要重复使用该运算器,便可以根据此数据在控制数据流动的状态机中为其安排必要的时序。

所以借助于硬件描述语言和综合工具大大加快了计算逻辑电路设计的过程。

5.3比较器

数值大小比较逻辑在计算逻辑中是常用的一种逻辑电路,一位二进制数的比较是它的基础。

下面列出了一位二进制数比较电路的真值表:

X

Y

(X>

Y)

=Y)

(X=Y)

(X<

(X<

(X!

从真值表很容易写出一位二进制数比较电路的布尔表达式如下:

Y)=X·

(~Y)

Y)=(~X)·

(X=Y)=(~X)·

(~Y)+X·

也很容易画出逻辑图。

位数较多的二进制数比较电路比较复杂,以前我们常用7485型四位数字比较器来构成位数较多的二进制数比较电路,如8位、16位、24位、32位的比较器。

同学们可以参考清华大学出版社刘宝琴老师编写的“数字电路与系统”中,有关多位并行比较器的设计的章节,在这里不再详细介绍。

用VerilogHDL来设计比较电路是很容易的。

下面就是一个位数可以由用户定义的比较电路模块:

modulecompare_n(X,Y,XGY,XSY,XEY);

input[width-1:

0]X,Y;

outputXGY,XSY,XEY;

regXGY,XSY,XEY;

parameterwidth=8;

always@(XorY)//每当X或Y变化时

begin

if(X==Y)

XEY=1;

//设置X等于Y的信号为1

elseXEY=0;

if(X>

XGY=1;

//设置X大于Y的信号为1

elseXGY=0;

if(X<

XSY=1;

//设置X小于Y的信号为1

elseXSY=0;

end

综合工具能自动把以上原代码综合成一个八位比较器。

如果在实例引用时分别改变参数width值为16和32综合工具就能自动把以上原代码分别综合成16位和32位的比较器。

5.4多路器

多路选择器(Multiplexer)简称多路器,它是一个多输入、单输出的组合逻辑电路,在数字系统中有着广泛的应用。

它可以根据地址码的不同,从多个输入数据中选取一个,让其输出到公共的输出端。

在算法电路的实现中多路器常用来根据地址码来调度数据。

我们可以很容易地写出一个有两位地址码,可以从四组输入信号线中选出一组通过公共输出端输出的功能表。

地址1

地址0

输入1

输入2

输入3

输入4

输出

可以很容易地写出它的布尔表达式,也很容易画出逻辑图,但是当地址码比较长,比如有12位长,而且每组输入信号位数较宽(如位宽为8)信号组的数目又较多时,再加上又需多路选择使能控制信号时,其逻辑电路的基本单元需要量是较大的,如画出逻辑图来就显得很复杂,电路具体化后不易于理解,(同学们可以参考阎石老师主编的“数字电子技术基础”教材,复习多路选择器的概念)。

用VerilogHDL来设计多路选择器电路是很容易的。

下面就是带使能控制信号的数据位宽可以由用户定义的八路数据选择器模块:

moduleMux_8(addr,in1,in2,in3,in4,in5,in6,in7,in8,Mout,nCS);

input[2:

0]addr;

input[width-1]in1,in2,in3,in4,in5,in6,in7,in8;

output[width-1]Mout;

always@(addrorin1orin2orin3orin4orin5orin6orin7orin8)

if(!

ncs)

case(addr)

3’b000:

Mout=in1;

3’b001:

Mout=in2;

3’b010:

Mout=in3;

3’b011:

Mout=in4;

3’b100:

Mout=in5;

3’b101:

Mout=in6;

3’b110:

Mout=in7;

3’b111:

Mout=in8;

endcase

else

Mout=0;

end

综合工具能自动把以上原代码综合成一个数据位宽为8的八路选一数据多路器。

如果在实例引用时分别改变参数width值为16和32,综合工具就能自动把以上原代码分别综合成数据宽度为16位和32位的八选一数据多路器。

5.5总线和总线操作

总线是运算部件之间数据流通的公共通道。

在硬线逻辑构成的运算电路中只要电路的规模允许,我们可以比较自由地来确定总线的位宽,因此可以大大提高数据流通的速度。

适当的总线的位宽,配合适当并行度的运算逻辑和步骤能显著地提高专用信号处理逻辑电路的运算能力。

各运算部件和数据寄存器组可以通过带控制端的三态门与总线的连接。

通过对控制端电平的控制来确定在某一时间片段内,总线归哪两个或哪几个部件使用(任何时间片段只能有一个部件发送,但可以有几个接收)。

用Verilog来描述总线和总线操作是非常简单的。

下面就是一个简单的与总线有接口的模块是如何对总线进行操作的例子:

moduleSampleOfBus(DataBus,link_bus,write);

inout[11:

0]DataBus;

//总线双向端口

inputlink_bus;

//向总线输出数据的控制电平

reg[11:

0]outsigs;

assignDataBus=(link_bus)?

outsigs:

12‘hzzz;

//当link_bus为高电平时通过总线把存在outsigs的计算结果输出

always@(posedgewrite)//每当write信号上跳沿时

begin//接收总线上数据并乘以五

outsigs<

=DataBus*5;

//把计算结果存入outsigs

通过以上例子我们可以理解使这个总线连接模块能正常工作的最重要的因素是与其他模块的配合,如:

何时提供write信号?

此时DataBus上数据是否已正确提供?

何时提供link_bus电平?

输出的数据是否能被有效地利用?

控制信号的相互配合由同步状态机控制的开关阵列控制。

在第七章里我们将详细介绍如何用VerilogHDL来设计复杂的同步状态机并产生精确同步的开关控制信号来控制数据的正确流动。

5.6流水线(pipeline)

流水线(pipe-line)设计技术:

流水线的设计方法已经在高性能的、需要经常进行大规模运算的系统中得到广泛的应用,如CPU(中央处理器)等。

目前流行的CPU,如intel的奔腾处理器在指令的读取和执行周期中充分地运用了流水线技术以提高它们的性能。

高性能的DSP(数字信号处理)系统也在它的构件(building-blockfunctions)中使用了流水线设计技术。

通过加法器和乘法器等一些基本模块,本节讨论了有关流水线的一些基本概念,并对采用两种不同的设计方法:

纯组合逻辑设计和流水线设计方法时,在性能和逻辑资源的利用等方面的不同进行了比较和权衡。

流水线设计的概念:

所谓流水线设计实际上就是把规模较大、层次较多的组合逻辑电路分为几个级,在每一级插入寄存器组暂存中间数据。

K级的流水线就是从组合逻辑的输入到输出恰好有K个寄存器组(分为K级,每一级都有一个寄存器组)上一级的输出是下一级的输入而又无反馈的电路。

图5.6表示了如何将把组合逻辑设计转换为相同组合逻辑功能的流水线设计。

这个组合逻辑包括两级。

第一级的延迟是T1和T3两个延迟中的最大值;

第二级的延迟等于T2的延迟。

为了通过这个组合逻辑得到稳定的计算结果输出,需要等待的传播延迟为[max(T1,T3)+T2]个时间单位。

在从输入到输出的每一级插入寄存器后,流水线设计的第一级寄存器所具有的总的延迟为T1与T3时延中的最大值加上寄存器的Tco(触发时间)。

同样,第二级寄存器延迟为T2的时延加上Tco。

采用流水线设计为取得稳定的输出总体计算周期为:

max(max(T1,T3)+Tco,(T2+Tco))

流水线设计需要两个时钟周期来获取第一个计算结果,而只需要一个时钟周期来获取随后的计算结果。

开始时用来获取第一个计算结果的两个时钟周期被称为采用流水线设计的首次延迟(latency)。

对于CPLD来说,器件的延迟如T1、T2和T3相对于触发器的Tco要长得多,并且寄存器的建立时间Tsu也要比器件的延迟快得多。

只有在上述关于硬件时延的假设为真的情况下,流水线设计才能获得比同功能的组合逻辑设计更高的性能。

采用流水线设计的优势在于它能提高吞吐量(throughput)。

假设T1、T2和T3具有同样的传递延迟Tpd。

对于组合逻辑设计而言,总的延迟为2*Tpd。

对于流水线设计来说,计算周期为(Tpd+Tco)。

前面提及的首次延迟(latency)的概念实际上就是将(从输入到输出)最长的路径进行初始化所需要的时间总量;

吞吐延迟则是执行一次重复性操作所需要的时间总量。

在组合逻辑设计中,首次延迟和吞吐延迟同为2*Tpd。

与之相比,在流水线设计中,首次延迟是2*(Tpd+Tco),而吞吐延迟是Tpd+Tco。

如果CPLD硬件能提供快速的Tco,则流水线设计相对于同样功能的组合逻辑设计能提供更大的吞吐量。

典型的富含寄存器资源的CPLD器件(如Lattice的ispLSI8840)的Tpd为8.5ns,Tco为6ns。

流水线设计在性能上的提高是以消耗较多的寄存器资源为代价的。

对于非常简单的用于数据传输的组合逻辑设计,例如上述例子,将它们转换成流水线设计可能只需增加很少的寄存器单元。

随着组合逻辑变得复杂,为了保证中间的计算结果都在同一时钟周期内得到,必须在各级之间加入更多的寄存器。

如果需要在CPLD中实现复杂的流水线设计,以获取更优良的性能,具有丰富寄存器资源的CPLD结构并且具有可预测的延迟这两大特点的FPGA是一个很有吸引力的选择。

流水线加法器与组合逻辑加法器的比较

采用流水线技术可以在相同的半导体工艺的前提下通过电路结构的改进来大幅度地提高重复多次使用的复杂组合逻辑计算电路的吞吐量。

下面是一个n位全加器的例子,如图5.7所示为实现该加法功能需要三级电路:

(1)加法器输入的数据产生器和传送器;

(2)数据产生器和传送器的超前进位部分;

(3)数据产生、传送功能和超前进位三者求和部分。

在n位组合逻辑全加器中插入三层寄存器或寄存器组,将它转变为n位流水线全加器,如图5.8(b)所示。

由于进位C-1既是第一级逻辑的输入,又是第二级逻辑输入,因此将C-1进位改为流水线结构时需要使用两级寄存器。

同样地,发生器输出在作为求和单元的输入之前,也要多次插入寄存器。

作为求和单元的输出,进位Cout要达到同一流水线的级别也需要插入两层寄存器。

若用拥有840个宏单元和312个有寄存能力I/O单元的LatticeispLSI8840分别来实现16位组合逻辑全加器和16位流水线全加器并比较它们的运行速度,对于16位组合逻辑全加器,共用了34个宏单元。

执行一次计算需经过3个GLB层,每次计算总延迟为45.6ns。

而16位流水线全加器共用了81个宏单元。

执行一次计算只需经过1个GLB层,每次计算总延迟为15.10ns(但第一次计算需要多用三个时钟周期),吞吐量约增加了三倍。

流水线乘法器与组合逻辑乘法器的比较:

首先,我们使用一个4*4乘法器的例子来说明部分积乘法器的基本概念。

然后,通过一个复杂得多的6*10乘法器来比较流水线乘法器和组合逻辑乘法器这两个不同设计方法的实现在性能上有何差异。

如图5.9所示,4*4乘法器可以被分解为部分积的向量和(或称加权和),比如说是16个1*1乘法器输出的向量和。

这里并没有直接在4*4乘法器的每一级都插入寄存器以达到改为流水线结构的目的,而是将其分割为1*4乘法器来产生所有的部分积向量。

这样分割的结果是形成了两级的流水线设计,相对1*1乘法器的组合具有更短的首次延迟,而吞吐延迟相同。

每一级的流水线求和用图5.8(b)所示的流水线加法器来实现。

我们用一个类似图5.9中的4*4、但更为复杂的6*10流水线乘法器来比较流水线乘法器与非流水线乘法器之间性能上的差异。

如图5.10所示,该6*10流水线乘法器采用6个10位乘法器来实现1*10乘法--a0*b[9:

0],a1*b[9:

0],a2*b[9:

0],a3*b[9:

0],a4*b[9:

0],a5*b[9:

0]。

由于ai非0即1,那么1*10乘法器的结果是b[9:

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 夏宇闻 第五

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx