模拟集成电路设计实习讲义SCUT自由下载Word下载.docx

模拟集成电路设计实习讲义SCUT自由下载Word下载.docx

- 文档编号:18717397

- 上传时间:2022-12-31

- 格式:DOCX

- 页数:28

- 大小:1.51MB

模拟集成电路设计实习讲义SCUT自由下载Word下载.docx

《模拟集成电路设计实习讲义SCUT自由下载Word下载.docx》由会员分享,可在线阅读,更多相关《模拟集成电路设计实习讲义SCUT自由下载Word下载.docx(28页珍藏版)》请在冰豆网上搜索。

图1-14加入激励源后的图

二、Spectre仿真(opam)

(1)直流分析(DCAnalyses)

我们在共模输入管脚接一个可以调节的电压源VCM,使得这个电压源的电压从0升到高到3.3v然后我们测量output端的电压。

从图1-14中的Tools菜单->

AnalogEnvironment调出spectre

图2-1spectre仿真界面

。

2-1setup菜单->

modellibrarys调出模型库设置窗口。

点击Browse找到使用的仿真文件“sm083006-1k.scs”,

Section那栏填入:

typical,然后点击ADD。

依次在Section栏中加入bjt,capacitor,diode,resistor并点击加入,结果如图:

图2-2setupresult

点击ok,回到spectre的主窗口。

提示:

我们在创建库lab_practice的时候已经指定了工艺库为chrt35rf,因此这里的模型库是自动设置好的。

现在我们要进行dc分析的设置了,从analyses菜单->

choose调出分析设置窗口。

选择DC分析,变化类型选择ComponentParameter,Componentname填入VCM参数为dc,变化范围是0到3.3(见图2-3).

图2-3dc分析设置

点击ok.回到了spectre主界面。

到此,已经把仿真环境设置好了。

现在我们要观察output端的波形,如何才能做到呢?

从spectre的outputs菜单->

tobeplot->

selectfromschematic,这个时候,会切换到schematic窗口,用鼠标点击一下output那条连线,看看发生了什么?

图2-4selectontheschematic

output端的颜色变了,标识出它的波形将会被显示,spectre的窗口已经变成了下面的

图2-5设置后的spectre

图2-6Output波形(结果显示共模输入电平在2.0V以下输出直流工作点基本不变)

DC分析,除了包含器件参数的仿真外,还可以进行温度仿真,设计变量仿真和器件模型参数仿真。

有兴趣的话可以自己摸索一下。

(2)AC分析

我们必须先明确一下ac分析的目的,所谓的ac分析,就是在一定的静态工作点上,施加一个小信号,然后分析输出的的交流信号,可以看出放大系数,频率响应等的特性。

先进行AC分析激励设置,将输入交流信号V1(正端)和V0(负端)的交流幅值设置为500mV,相位都为0。

由于两端反向连接,故反向,差分交流输入的幅值为1V。

图2-7交流分析激励设置

现在进行分析设置,重新调出图2-3的窗口,。

图2-8ac分析设置

设置频率从1变到1G,点击ok,然后netlist&

run:

图2-9输出波形查看设置

图2-10输出运算放大器的波特图

现在测量一下图2-10中的运算放大器的低频增益(Av0)、3dB带宽(f0)、相位裕度(PM)等参数。

有两种测量方法:

Trace工具条测量法及calculator精确计算测量法

图2-11用Trace工具条进行仿真参数的测量,此图读出低频增益为51.27dB

-3dB带宽和相位裕度也可测出。

图2-12用Trace工具条测量-3dB带宽(51.27dB-3dB=48.27dB),测出为484.83kHz

图2-13用Trace工具条测量相位裕度,定义为增益为1(0dB)时对应的相位与-180oC的距离。

先从幅频特性中找出增益为0dB(此处为99.45dB,近似0dB)对应的频率(121.91MHz),再在相频特性中找出此频率对应的相位,与-180oC相减即为相位裕度(-125.82oC-(-180oC)=54.18oC)

开子窗口按钮

图2-14以实际幅值而非dB值显示的幅频特性(因为输入为1.0V,所以实测低频输出电压值即为放大器的低频增益值,365.98)

a)如果想精确计算仿真结果的参数,则需用Calculator工具。

先Edit/Delete删除第二个子窗口,只留下原来的幅频特性和相频特性在一起的图。

Tools/Calculator弹出Calculator窗口

图2-15Calculator窗口

先将options菜单中的setRPN那个勾去掉。

选择ac分析,再点击vf选项,去到电路原理图中点击输出点(out),然后在右下白色窗口中选择测量bandwidth,再点击一下Append字样右边的plot按钮就可以计算出仿真波形的-3dB带宽(491500Hz,约480kHz)。

相位裕度也可用同样的方法计算(选phasemargin,测出PM=54.15oC)

图2-16用Calculator计算运放的-3dB带宽

三、建立opam的symbol:

整个系统包括上面设计好的运算放大器(opam)模块和后面的带隙基准源(bandgap)模块。

系统的设计采用层次化设计方法:

顶层为系统电路,调用opam模块和bandgap模块。

而要模块调用的话必须先为设计好的模块建立symbol。

方法为:

图3-1将opam另存为opam_simu

重新进入opam文件修改

先将电压源、电流源等删除,加pin(快捷键按p),加pin时可以单击鼠标右键对pin旋转。

依次加上vdd,GND,Iin,vin+,vin-共五个输入pin,加上之前加的out输出pin,共六个pin。

修改后的电路图如图3-2所示。

图3-2去电压源、电流源,以及gnd,再加相应地pin

接着我们要对设计要的原理图绘制symbol,生成symbol后,这个opamp就可以在其它电路中被调用。

从原理图生成symbol的方法如下,在VirtuosoSchematicEditing窗口中,选择菜单Design->

CreateCellview->

FromCellview.

图3-3从菜单创建symbol

图3-4在Tool/DataType一栏中选Composer-Symbol

图3-5安排pin的位置

图3-5只是pin摆放的一个例子。

图3-6创建好的opam模块的Symbol

图3-7创建的Symbol在LibraryManager中体现

四、bandgap模块

(1)温度系数仿真

图4-2温度从0到100oC变化时bandgap电压输出的变化系数仿真设置

图4-3bandgap温度系数仿真结果

按“D”按键使用两点差测量工具,出来一个红色三角形和一个绿色三角形。

将红色条拉到输出电压最大位置,绿色条拉到输出最小位置,可以读出波形的最大电压(Ymax)、最小电压(Ymin)及最大最小电压差(Y),从而计算出bandgap的温度系数TC。

TC=(Ymax-Ymin)/[(1/2)(Ymax+Ymin)]/100

=2*0.003027/(2.000711+1.997684)/100

=15.14ppm

(2)PSRR仿真

在直流VDD的上面加一交流信号(图4-4),设置交流仿真的频率范围(图4-5),看out1信号(图4-6)。

图4-4PSRR激励仿真设置图

在直流电源VDD的基础上加一交流信号vdd,模拟电源电压波动对电路输出的影响(电源抑制比,PSRR(dB)=20log(Vout/VDD))

图4-5电源抑制比仿真设置

图4-6电源抑制比仿真结果

从仿真结果图4-6可知,在频率<

1kHz时,PSRR<

-35dB

五、总电路(调用bandgap和opam模块):

将lab_practice库中的bandgap_simu单元copy成bandgap单元,打开bandgap单元电路,删除直流电压源和交流电压源,创建bandgap单元的Symbol。

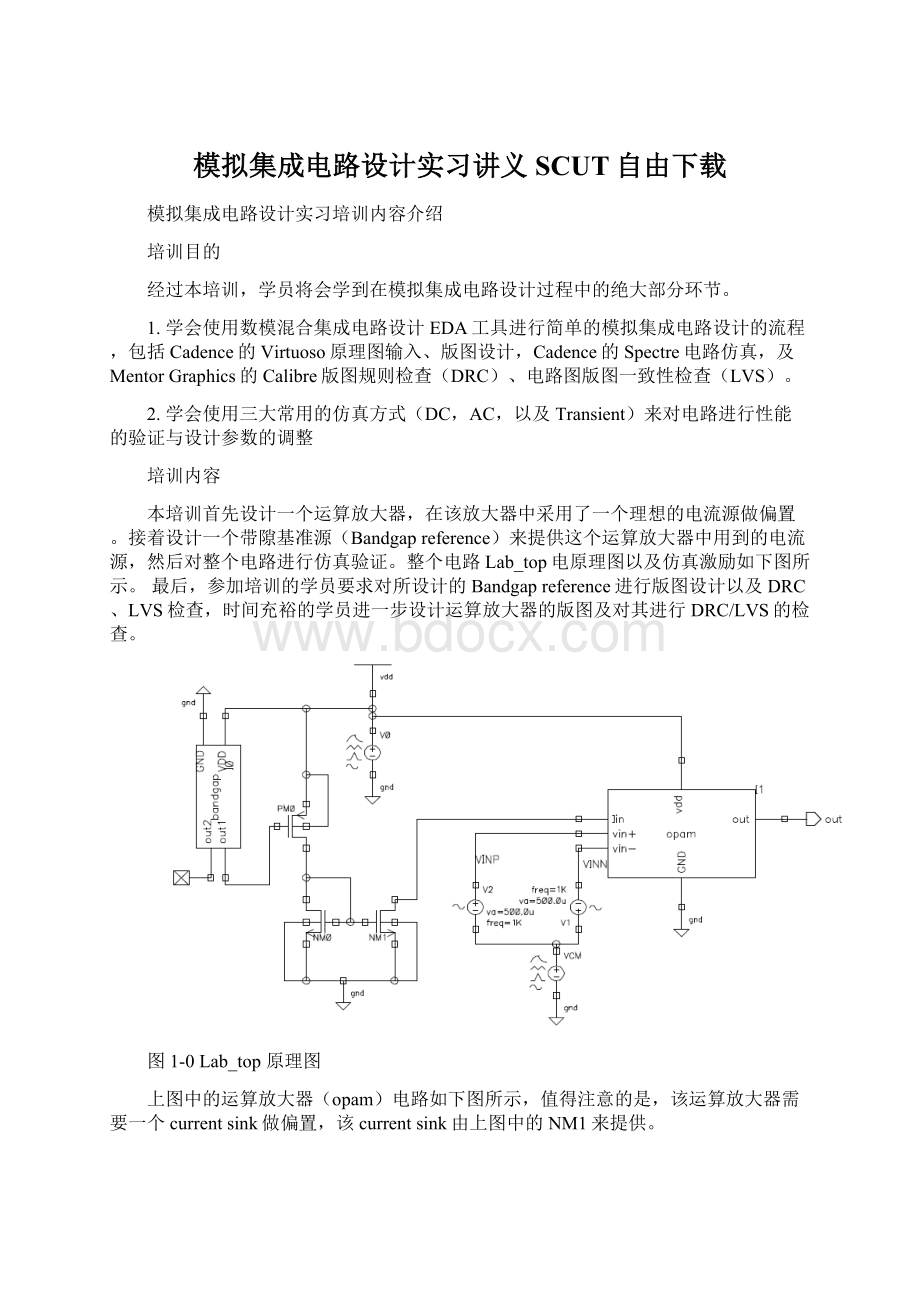

在lab_practice库中创建顶层系统电路lab_top单元,然后调用bandgap和opam子电路,加上几个PMOS和NMOS管做镜像电流源缓冲,再加上直流电源(V0)、运放的差分共模电压(VCM)及差分输入交流信号激励(VINP、VINN),如图5-1所示。

注,lab_practice_demo中的lab_top中的两个差分输入信号有点错误,需要修改,将VINN的方向翻转180度,与VINP反向,并将ACphase由180度改为0度。

图5-1使用bandgap模块和opam模块构成的电路总图

(1)先做瞬态仿真调静态偏置工作点

图5-2做瞬态仿真设置

图5-3瞬态仿真输出波形选择NM1的漏端(可看NM1的漏极电流)及输出电压(out端)

图5-4瞬态仿真波形

从图5-4可以看出,0.25us后NM1输出给opam的偏置电流基本保持在54.2uA。

输出电压V(out)则在不断变化,这是由于输入加了1mV的差分正弦信号引起的。

如果要看清楚V(out)的整个变化,只要将仿真截止时间拉长至10mS以上就可以了,此时,输入激励以及输出响应如图5-5。

请注意,输出响应out的相位跟VINP是一致,跟VINN的相位是相反的。

图5-5仿真时间为10mS的瞬态响应波形

(2)再做AC分析

图5-6AC分析时VINP和VINN设置

由于在lab_top的连接图中,两个输入激励的连接是相反的,这样VINP和VINN就是幅度都为0.5V但相位相反的正弦信号,从而差分信号(VINP-VINN)为幅值为1.0V的正弦信号。

图5-7AC仿真结果

图5-7中左边子窗口可以看出低频增益为365.93。

用calculator工具对子窗口2中的特性进行测量,测得其带宽为493.166kHz,相位裕度PM=54.11o

六、画版图

1.先画bandgap模块,打开librarymanager,新建版图文件

图6-1新建bandgap的版图文件

图6-2进入版图编辑器界面

在版图界面选择Tools/LayoutXL打开相应模块的schematic

图6-3使用LayoutXL进行原理图和版图的交互编辑

在VirtuosoXLLayout中,选择菜单Create/PickFromSchematic,然后鼠标点击schematic中的元件,在layout编辑器中放入。

布图设计分为两步:

元件布局与布线

在布局阶段需要根据原理图的设计考虑元件之间的匹配,此处建议的匹配方式:

(1)两个三极管,本电路大小比为1:

8,所以小的管放中间,大管分成8个相同的方块以小管为中心均匀分布;

(2)电阻R16、R19、R20,RA=RB=10RC电阻匹配采用一维对称A1B1A2B2…..A5B5CB6A6B7A7…B10A10

原理图中R20(L/W=21.25um/2.5um)、R16(L/W=192.85um/2.5um)、R19(L/W=192.85um/2.5um)这三个电阻需匹配。

故将R16和R19拆分成8段21.25um/2.5um再加上两段11.425um/2.5um,以R20为中心交叉对称放置于R20两边;

(3)MA=MB=MC=2MD的MOS管匹配也采用一维对称0.5MA0.5MB0.5MCMD0.5MC0.5MB0.5MA;

原理图中的PM66、PM65、PM68、PM69这四个晶体管为镜像电流源,故需要较好匹配。

各管的宽长比为PM66(5um/2um)、PM65(10um/2um)、PM68(10um/2um)、PM69(10um/2um),将这些管拉到版图界面后发现PM66的宽度和其他三个管的宽度不一样,这样很难匹配。

故修改原理图,将PM65、PM68、PM69三个管的宽长比改为和PM66一样(5um/2um),同时将这三个管的multiplier设置为2,这样这三个管的实际宽长比相当于两个PM66的并联,即为10um/2um。

这样布版图时就可以匹配了。

同样在原理图中有两个dummyMOS管,需要加到两边。

(4)参数相同的MOS管元件匹配:

差分对,电流镜等。

需要在原理图中将匹配的每个MOS管的宽度改为原来的一半,同时将multiplier设置为2,即拆成两个一半大小的MOS管的并联,且加上两个dummy管。

当调到版图中按上面的方式对称布局。

(5)参数相同的电阻元件匹配:

R15、R17。

在版图中拆成两段长度为一半的电阻,记得在原理图中加入dummy元件。

将多个匹配的元件对齐:

首先将匹配的七个MOS版图水平对齐,方法是Edit/Others/Align然后弹出对齐设置窗口,按图6-7所示设置,然后点击SetNewReference,在Layout中先选中中间MOS版图作为对齐中心,然后依次点击其他六个MOS,这样这七个MOS管就水平对齐了(元件之间空隙为1.0um)。

图6-7元件对齐设置

接着垂直方向对齐电阻,这回将图6-7的Alignmentdirection选项中的Horizontal改为Vertical,Spacings改为3.0um,点击SetNewReference,在Layout中先选择中间那个电阻作为参考位置,然后依次点击上面和下面的电阻,将它们全部对齐。

最后对齐九个三极管,先将中间三极管位置放好,然后用上面的方法水平和垂直对齐其他三极管,这里Spacings设置为3.0um

所有的元件都放进来并对齐位置后,布局就完成了,接下来是布线。

为了将元件的衬底接到VDD或GND,以及对匹配的所有元件进行防干扰,所以对需要的管子加guardring:

PMOS管加well-guardring,NMOS管加p-guardring。

加方法(以pmos为例):

调出LayoutXL,放置nwell层框将要加well-guardring的所有pmos框起来,选中nwell框,shift-G,双击nwell框之外的地方将guardring放好,按“s”(拉伸线条)将nwell框拉到围住guardring的内框,如图6-10所示。

nmos管加完p-guardring后,则将之前放置的nwell层框删除。

图6-10给PM65、PM66、PM68、PM69四个PMOS加保护环(guardring)

2.再画OPAM的版图,方法如画Bandgap。

为画版图方便,可以考虑将OPAM原理图中的M10a和M10b的长、宽都降低10倍,即改为:

W10a=58um,L10=2um,Multiplier=2

原理图中所有需要匹配的元件都要拆成两个,并加上dummy元件。

Calibre的quickstart

注:

如运行DRC和LVS时出现类似“errorwhilecomplingrules”错误,则先修改下面两个文件:

1.修改DRC规则文件,将/home/eda/wzh_lab/verify/drc/drcfile/yi046dr002_1k00/drc_header_1k_00文件中包含在INCLUDE/home/eda/ICPRJ/verify/drc…..等语句中的ICPRJ改成wzh_lab保存

2.修改LVS规则文件,将/home/eda/wzh_lab/verify/lvs/lvsfile/chrt035rf.sg.lvs.cal文件中ICPRJ改成wzh_lab保存

一、DRC

1.先做bandgap的drc。

Virtuoso界面菜单最右边Calibre/RunDRC,出现如图1所示界面

图1DRC运行界面

在wzh_lab/verify/drc目录中创建目录bandgap,然后将drc的工作目录设为bandgap目录,如图2所示。

然后按图2中的RunDRC按钮,稍等片刻,出现图3所示的DRC检查结果。

图2设定工作目录和DRC文件

错误01的四个角的坐标,双击其中任意一个坐标,可在layout中显示错误位置

在Virtuosolayout界面菜单中,CalibreRunLVS进入界面设置

Rules,Calibre-LvsRulesFile:

/home/eda/wzh_lab/verify/lvs/lvsfile/chrt035rf.sg.lvs.cal

Calibre-LvsRunDirectory:

/home/eda/wzh_lab/verify/lvs/

Inputs,Layout:

选择Exportfromlayoutviewer

其他基本不用设置,然后RunLVS,结果如图8所示,

Layout输出netlist

Schematic输出的netlist

图8LVS结果,出现82个不一样的地方

LVS错误的修改相对较复杂,没有简单的规律可循,需要有相当的经验。

下面就本实验项目给出需要修改的地方,大家按照以下方式修改即可:

1.修改导出的netlist文件(bandgap.cdl)该文件是原理图输出的netlist,在上述例子中,该文件位于/home/eda/wzh_lab/verify/lvs/netlist

加文件等效语句(解决在chrt35rf工艺中schematic输出的netlist和layout提取的netlist中使用模型名字不同的问题),将下列语句加到网表文件bandgap.cdl中语句.PARAM的下面,每行一句:

*.EQUIVnmos_3p3=NM

*.EQUIVpmos_3p3=PM

*.EQUIVnpolyf_u_1k=YAK

*.EQUIVPIP=CP

*.EQUIVVPNP_5x5=BV

对电容的修改:

把电容的调用语句添加上以下画线的部分,尺寸值用原理图上的尺寸。

CC10net86net72875.00fc_length=20uc_width=35u$[CP]M=1

对电阻的修改:

把电阻调用语句的第三端去掉,即以下画线部分去掉。

RR20net64net68.71831K$SUB=net42$[YAK]

然后,加上电阻相应的宽和长,尺寸值用原理图上的尺寸,如下面画线部分:

RR20net64net68.71831Kw=2.5ul=21.25u$[YAK]

以上仅仅是修改了电阻RR20,其他的电阻请参照电阻RR20修改的方式进行修改,其中各个电阻的宽度w=和长度l=中的值需要用原理图中的数字来加。

图9通过LVS检查的提示界面

华南理工大学国家集成电路人才培养基地

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 模拟 集成电路设计 实习 讲义 SCUT 自由 下载

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx