AXI总线学习Word文件下载.docx

AXI总线学习Word文件下载.docx

- 文档编号:18683201

- 上传时间:2022-12-31

- 格式:DOCX

- 页数:17

- 大小:1.11MB

AXI总线学习Word文件下载.docx

《AXI总线学习Word文件下载.docx》由会员分享,可在线阅读,更多相关《AXI总线学习Word文件下载.docx(17页珍藏版)》请在冰豆网上搜索。

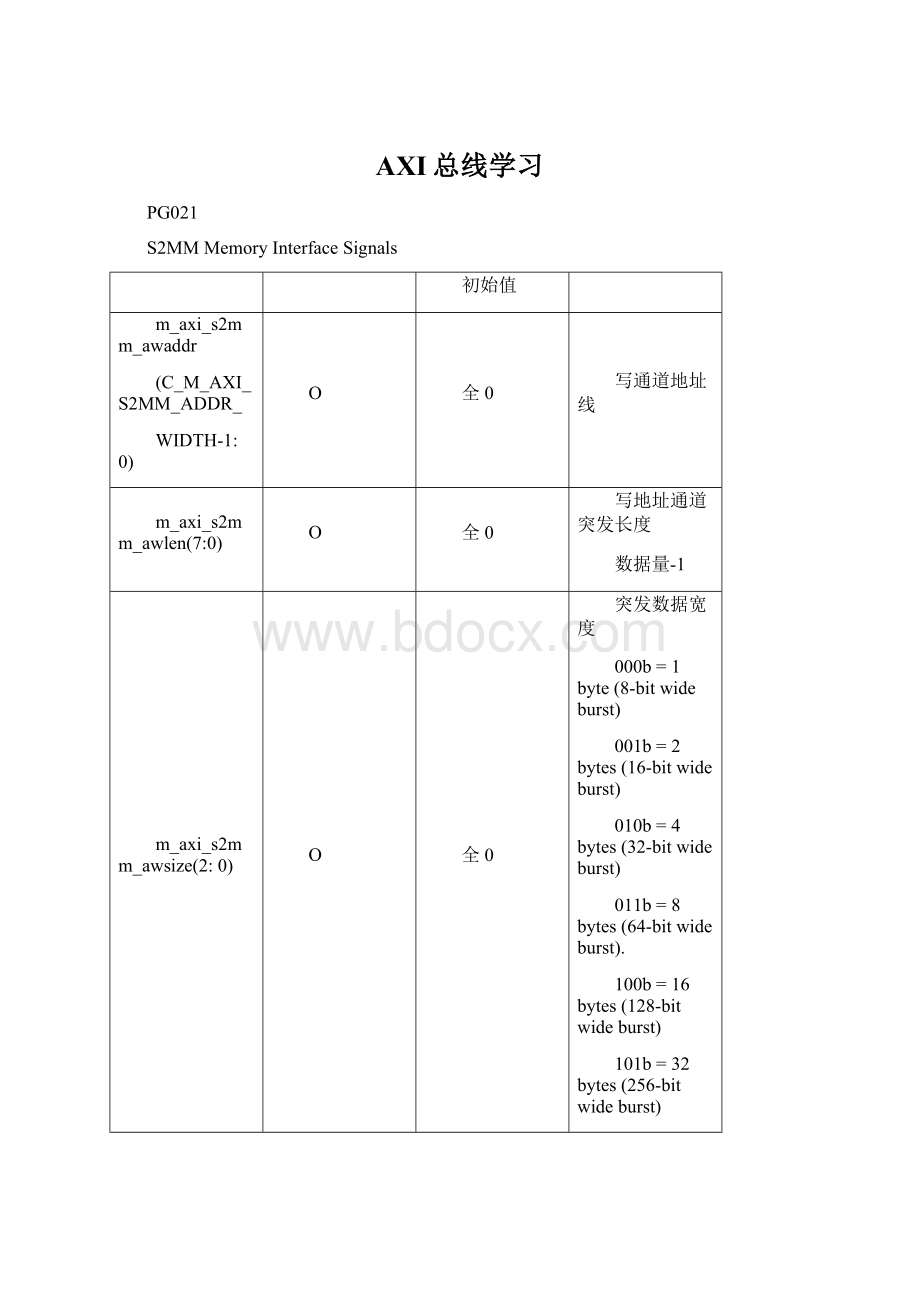

数据量-1

m_axi_s2mm_awsize(2:

突发数据宽度

000b=1byte(8-bitwideburst)

001b=2bytes(16-bitwideburst)

010b=4bytes(32-bitwideburst)

011b=8bytes(64-bitwideburst).

100b=16bytes(128-bitwideburst)

101b=32bytes(256-bitwideburst)

m_axi_s2mm_awburst(1:

01b=INCR-Incrementingaddress

写地址通道写地址有效

I

从设备准备好接受写地址

写数据通道数据线

字节使能信号

写数据通道最后一个数据标志

写数据通道数据有效标志

从设备准备接收数据就绪

写应答通道响应

00=OK

10=从设备返回错误

11=地址译码错误

写应答通道应答有效标志

准备好接收应答信息

寄存器空间

支持Scatter/Gather

MM2SDMA控制寄存器

4

MM2SDMA状态寄存器

8

MM2S当前描述符寄存器

10h

MM2S尾描述符寄存器

30h

S2MMDMA控制寄存器

34

S2MMDMA状态寄存器

38

S2MM当前描述符寄存器

40

S2MM尾描述符寄存器

不支持Scatter/Gather

18h

MM2S源地址寄存器

28

MM2S突发长度寄存器

48

S2MM目的地址寄存器

58

S2MM缓冲区长度

全部是小端地址模式:

DMA控制寄存器:

Bit0:

0当前DMA操作完成后停止DMA传输或者S/G方式下未完成的命令或传输都被清掉。

AXI4-Streamoutsarepotentiallyterminatedearly.Descriptorsintheupdatequeueareallowedtofinishupdatingtoremotememorybeforeenginehalt.

1启动DMA传输。

Bit2:

软件复位整个DMA引擎。

Bit12:

中段完成使能。

Bit13:

中段完成延时使能。

简单模式下无效。

Bit14:

错误中断时能。

Bit23:

16中断阈值。

最小值为1.每发生一次中断,中断阈值计数器减一,当中断阈值寄存器为0时,DMA引擎向外产生一个中断。

Bit31:

24中断延时寄存器。

用来设置中断超时时间。

InterruptDelayTimeOut.Thisvalueisusedforsettingtheinterrupttimeoutvalue.TheinterrupttimeoutisamechanismforcausingtheDMAenginetogenerateaninterruptafterthedelaytimeperiodhasexpired.当中断延时寄存器失效后为了保证仍然可以差生中断。

Thisisusedforcaseswhentheinterruptthresholdisnotmetafteraperiod

oftime,andtheCPUdesiresaninterrupttobegenerated.Timerbegins

countingattheendofapacketandresetswithreceiptofanewpacketor

atimeouteventoccurs.Settingthisvaluetozerodisablesthedelaytimerinterrupt.

如果在一定的时间内,中断阈值寄存器仍然不到0,而且CPU希望产生一个中断。

那么在一个数据包完成后,计数器开始计数直到接收到一个新包后或者超时事件发生后复位计数器。

DMA状态寄存器:

停止状态位。

0=DMA运行

1=DMA通道停止。

从DMA控制寄存器的停止位到状态位反映出来有一段时间。

Bit1:

DMA通道空闲。

Bit3:

支持S/G方式否。

Bit4:

DMA内部错误。

Bit5:

DMASlave错误。

Bit6:

DMA译码错误。

Bit8:

SG方式内部错误。

Bit9:

SG方式从设备错误。

DMA传输完成中断位。

如果中断完成了并且中断阈值达到了,就会产生一个AXIDMA中断。

SG方式下才有CTRL、StatusSTREAM,所以才有APP0~APP5。

尾描述符里存着状态数据。

如果使用了应用层状态数据,低23位必须存储RxLength必须载入尾描述符的APP4里。

如果没有使用,尾描述符的APP4存储接受到的状态数据。

数据结构式链表,头指针指向下一个指针,尾指针指向头指针。

从获得带有TXSOF的包开始,一直获取到TXEOF的包为止。

每个描述符的状态域存储了实际传输的字节数。

把所有描述符的字节数累加起来就是总接收数。

描述符管理

DMA启动位置1;

尾描述符指针指向BD12;

将描述符入队直到队满;

更新当前指针指向下一个描述符;

只要尾指针不等于当前指针,并且队不满,描述符入队;

队列更新;

完成位为1的描述符被释放掉用于再分配。

描述符的值域被更新(包括完成位,其他控制位,缓冲区指针,缓冲区长度等)。

描述符再分配后,尾指针指向最后一个再利用的指针。

如果DMA暂停(遇到了初始TAILDESC_PTR指针指向的地方),当写了新的TAILDESC_PTR值后,重新启动。

AXIDMA向目标器件插入了一个标志表示数据类型。

对于以太网,控制标签的最高字节为A。

状态FIFO填满了,AXIDMA在数据流中会插入等待周期。

AXIInterconnect可以插入读/写FIFO缓冲来避免死锁。

AXIDMA*_ISSUING乘以*_BURST_SIZE<

*_FIFO_DEPTH

使用EDK的时候,为MM2s和S2MM都实例化了FIFO。

中断控制器

一旦接受到EOF标志的包开始计数。

接收到SOF标志的包后复位。

当一个延时中断发生后,延时计数器清零,直到中断服务程序中DMASR.Dly_Irq位清零后才继续计数。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- AXI 总线 学习

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

铝散热器项目年度预算报告.docx

铝散热器项目年度预算报告.docx