EDA智能函数发生器kWord格式.docx

EDA智能函数发生器kWord格式.docx

- 文档编号:18587993

- 上传时间:2022-12-28

- 格式:DOCX

- 页数:19

- 大小:391.38KB

EDA智能函数发生器kWord格式.docx

《EDA智能函数发生器kWord格式.docx》由会员分享,可在线阅读,更多相关《EDA智能函数发生器kWord格式.docx(19页珍藏版)》请在冰豆网上搜索。

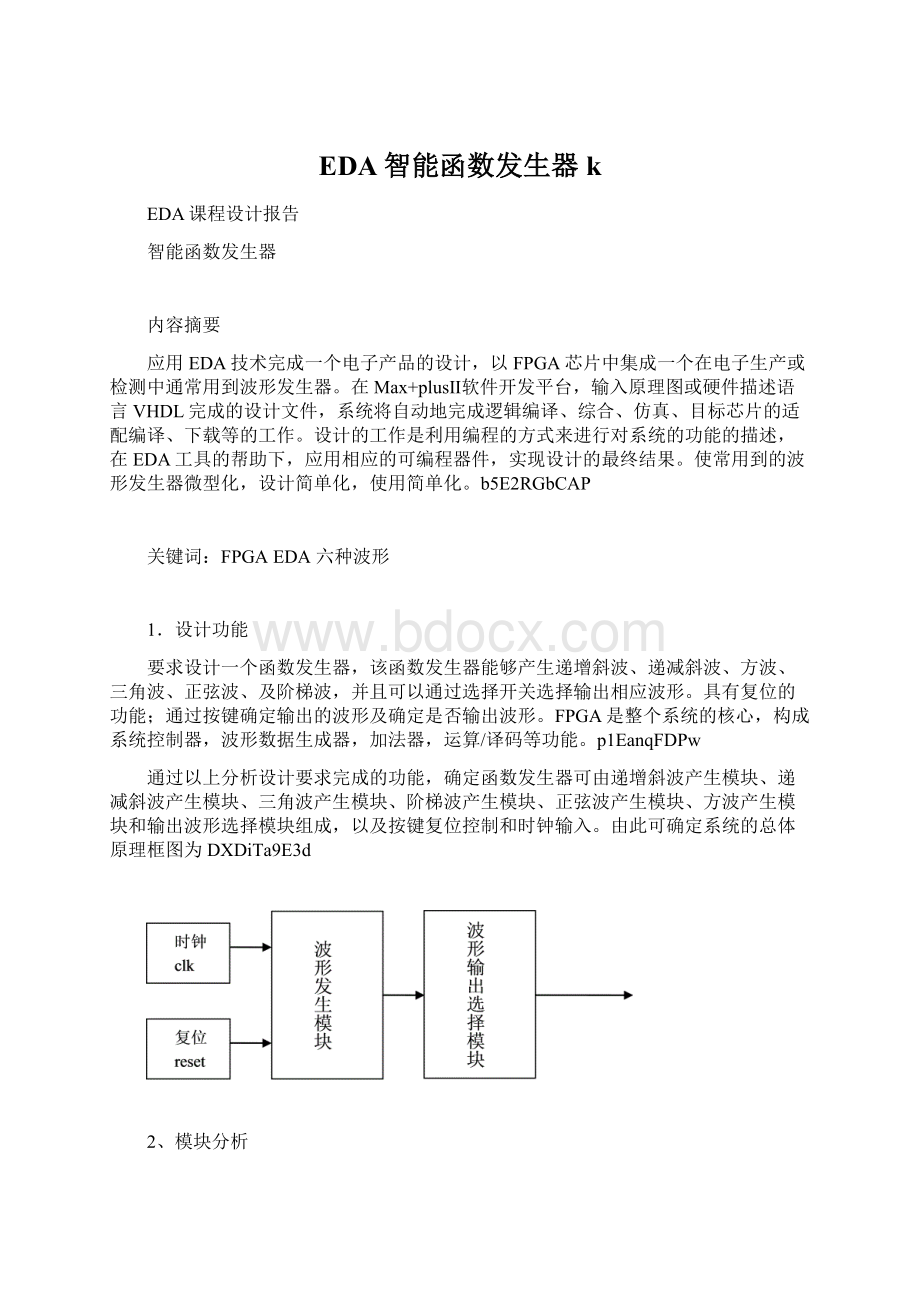

Q【7..0】为输出信号,根据输出函数选择信号SEL【2..0】的取值输出相应的波形。

5PCzVD7HxA

一、路要产生六种不同的波形,因此要对每种波形函数设计对应的电路模块,每个模块的输入输出设置相同,但不同函数发生模块对输入信号的处理方式是不同的,仅以递增斜波函数为例,模块框图如图(2>

。

其中CLK为时钟输入信号,CLR为复位清零信号,Q【7..0】为输出波形函数。

jLBHrnAILg

二、选择电路本质是一个简单的译码器模块。

其框图如图2所示。

其中SEL【2..0】为输出选择信号,根据该信号的取值,电路将选择输入信号D0【7..0】~D5【7..0】中的某一组数据,作为输出信号在输出端Q【7..0】输出。

xHAQX74J0X

完整电路原理图:

<

1)、Increase斜波函数发生模块框图

Increase斜波函数发生模块VHDL语言描述:

LIBRARYIEEE。

USEIEEE.STD_LOGIC_1164.ALL。

USEIEEE.STD_LOGIC_UNSIGNED.ALL。

ENTITYincreaseIS

PORT(

CLK,CLR:

INSTD_LOGIC。

Q:

OUTSTD_LOGIC_VECTOR(7DOWNTO0>

>

ENDincrease。

ARCHITECTURErtlOFincreaseIS

BEGIN

PROCESS(CLK,CLR>

VARIABLETMP:

STD_LOGIC_VECTOR(7DOWNTO0>

BEGIN

IFCLR='

1'

THEN

TMP:

="

00000000"

ELSIFCLK'

EVENTANDCLK='

IFTMP="

11111111"

TMP:

="

ELSE

=TMP+1。

ENDIF。

ENDIF。

Q<

=TMP。

ENDPROCESS。

ENDrtl。

Increase斜波函数发生模块仿真图

2)、decrease斜波函数发生模块框图:

decrease斜波函数发生模块VHDL语言描述:

ENTITYdecreaseIS

ENDdecrease。

ARCHITECTURErtlOFdecreaseIS

=TMP-1。

decrease斜波函数发生模块仿真图

3)Delta三角波函数发生模块框图:

Delta三角波函数发生模块仿VHDL语言描述:

ENTITYdeltaIS

ENDdelta。

ARCHITECTURErtlOFdeltaIS

VARIABLETAG:

STD_LOGIC。

IFTAG='

0'

IFTMP="

11111110"

TMP:

TAG:

='

ELSE

ENDIF。

ELSE

00000001"

Delta三角波函数发生模块仿真图

4)、ladder梯形波函数发生模块框图:

ladder梯形波函数发生模块VHDL语言描述:

ENTITYladderIS

ENDladder。

ARCHITECTURErtlOFladderIS

=TMP+16。

TAG:

ladder梯形波函数发生模块仿真图

5)、sin正弦波函数发生模块框图:

sin正弦波函数发生模块VHDL语言描述:

USEIEEE.STD_LOGIC_ARITH.ALL。

ENTITYsinIS

ENDsin。

ARCHITECTURErtlOFsinIS

INTEGERRANGE0TO63。

Q<

IFTMP=63THEN

=0。

CASETMPIS

WHEN0=>

Q<

=conv_std_logic_vector(255,8>

WHEN1=>

=conv_std_logic_vector(254,8>

WHEN2=>

=conv_std_logic_vector(252,8>

WHEN3=>

=conv_std_logic_vector(249,8>

WHEN4=>

=conv_std_logic_vector(245,8>

WHEN5=>

=conv_std_logic_vector(239,8>

WHEN6=>

=conv_std_logic_vector(233,8>

WHEN7=>

=conv_std_logic_vector(225,8>

WHEN8=>

=conv_std_logic_vector(217,8>

WHEN9=>

=conv_std_logic_vector(207,8>

WHEN10=>

=conv_std_logic_vector(197,8>

WHEN11=>

=conv_std_logic_vector(186,8>

WHEN12=>

=conv_std_logic_vector(174,8>

WHEN13=>

=conv_std_logic_vector(162,8>

WHEN14=>

=conv_std_logic_vector(150,8>

WHEN15=>

=conv_std_logic_vector(137,8>

WHEN16=>

=conv_std_logic_vector(124,8>

WHEN17=>

=conv_std_logic_vector(112,8>

WHEN18=>

=conv_std_logic_vector(99,8>

WHEN19=>

=conv_std_logic_vector(87,8>

WHEN20=>

=conv_std_logic_vector(75,8>

WHEN21=>

=conv_std_logic_vector(64,8>

WHEN22=>

=conv_std_logic_vector(53,8>

WHEN23=>

=conv_std_logic_vector(43,8>

WHEN24=>

=conv_std_logic_vector(34,8>

WHEN25=>

=conv_std_logic_vector(26,8>

WHEN26=>

=conv_std_logic_vector(19,8>

WHEN27=>

=conv_std_logic_vector(13,8>

WHEN28=>

=conv_std_logic_vector(8,8>

WHEN29=>

=conv_std_logic_vector(4,8>

WHEN30=>

=conv_std_logic_vector(1,8>

WHEN31=>

=conv_std_logic_vector(0,8>

WHEN32=>

WHEN33=>

WHEN34=>

WHEN35=>

WHEN36=>

WHEN37=>

WHEN38=>

WHEN39=>

WHEN40=>

WHEN41=>

WHEN42=>

WHEN43=>

WHEN44=>

WHEN45=>

WHEN46=>

WHEN47=>

WHEN48=>

WHEN49=>

WHEN50=>

WHEN51=>

WHEN52=>

WHEN53=>

WHEN54=>

WHEN55=>

WHEN56=>

WHEN57=>

WHEN58=>

WHEN59=>

WHEN60=>

WHEN61=>

WHEN62=>

WHEN63=>

WHENOTHERS=>

NULL。

ENDCASE。

sin正弦波函数发生模块仿真图

6)square方波函数发生模块框图:

square方波函数发生模块VHDL语言描述:

ENTITYsquareIS

ENDsquare。

ARCHITECTURErtlOFsquareIS

SIGNALTAG:

VARIABLECNT:

TAG<

IFCNT<

63THEN

CNT:

=CNT+1。

=NOTTAG。

PROCESS(CLK,TAG>

IFCLK'

Q<

square方波函数发生模块仿真图

整图仿真

课程设计心得

设计语言主要是采用VHDL语言的自顶向下的设计方法。

EDA中,自顶向下的设计方法,就是在整个设计流程中各设计环节逐步求精的过程,应用VHDL运行自顶向下的设计,就是使用VHDL模型在所有综合级别上对硬件进行说明、建模和仿真测试。

顶层文件采用了原理图的方法设计,使各模块之间的层次关系清晰。

LDAYtRyKfE

应用EDA技术用FPGA完成波形发生器,通过选择波形的按钮,实现6种波形的互相转换。

利用示波器可以验证波形发生器与原定的设计的理论是相一致。

Zzz6ZB2Ltk

用FPGA完成波形发生器的方法与传统的方法相比较,硬件结构是相当简单的。

大大减小了它的体积和重量。

可以节去传统的烦琐的硬件设计和硬件组合。

易于使用,按下选择波形的选择按钮,即可选出你所需的波形。

dvzfvkwMI1

PFGA里面有的是有待连接的逻辑门、D触发器等器件,它的外围还要有EEPROM、SDRAM、FLASH与之相配合才可以正常工作,这一点可能会广泛应用FPGA来比较麻烦。

随着技术的发展,如果把EEPROM、SDRAM、FLASH都集成要在FPGA中去,组成它的最小系统,这样的话将会,节去芯片外的线路设计,会得到更加广泛地的应用。

rqyn14ZNXI

应用EDA技术完成波形发生器的设计,设计简单。

可以看到利用EDA技术完成一个电子设计,可以节省我们开发时间,从而提高大大地了我们的效率。

采用新技术就是为了提高效率,快速完成设计任务。

我们做一个工程时,所在追求的也是快且高效率。

不断地去快速掌握并能快速地应用新技术是我们做技术的人的基本素质。

我们要注重自己在这方面的能力。

当然我们不能废弃我们基本的东西—学科基础,全面发展自己,这需要我不断去追求。

EmxvxOtOco

通过这次课设,也给我带来以下一些收获:

1、

进一步熟悉maxplusII软件的使用和操作方法,以及硬件实现时的下载方法与运行方法;

2、

对VHDL语言的自顶向下设计方法有了进一步的认识;

在底层文件具备的条件下,使用原理图可以使设置更加简单。

使程序清晰,增加可读性。

SixE2yXPq5

3、

锻炼了独立思考和解决问题的能力,也认识到团队合作的重要性。

4、

熟悉了写电子设计实验报告的方法,为写毕业设计论文奠定了一定的基础

!

参考文献

[1]卢毅.赖杰.VHDL与数字电路设计.北京:

科学出版社,

[2]潘松.VHDL使用教程.成都:

电子科技出版社,2000

[3]黄继业.EDA技术实用教程.科学出版社,2002

[4]徐志军.CPLD/FPGA的开发与应用.北京电子工业出版社,[5]曾繁泰,侯亚宁,崔元明.可编程器件应用导论,20016ewMyirQFL

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 智能 函数 发生器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

对中国城市家庭的教育投资行为的理论和实证研究.docx

对中国城市家庭的教育投资行为的理论和实证研究.docx