整理常用存储器芯片设计指南文档格式.docx

整理常用存储器芯片设计指南文档格式.docx

- 文档编号:18499206

- 上传时间:2022-12-17

- 格式:DOCX

- 页数:14

- 大小:236.09KB

整理常用存储器芯片设计指南文档格式.docx

《整理常用存储器芯片设计指南文档格式.docx》由会员分享,可在线阅读,更多相关《整理常用存储器芯片设计指南文档格式.docx(14页珍藏版)》请在冰豆网上搜索。

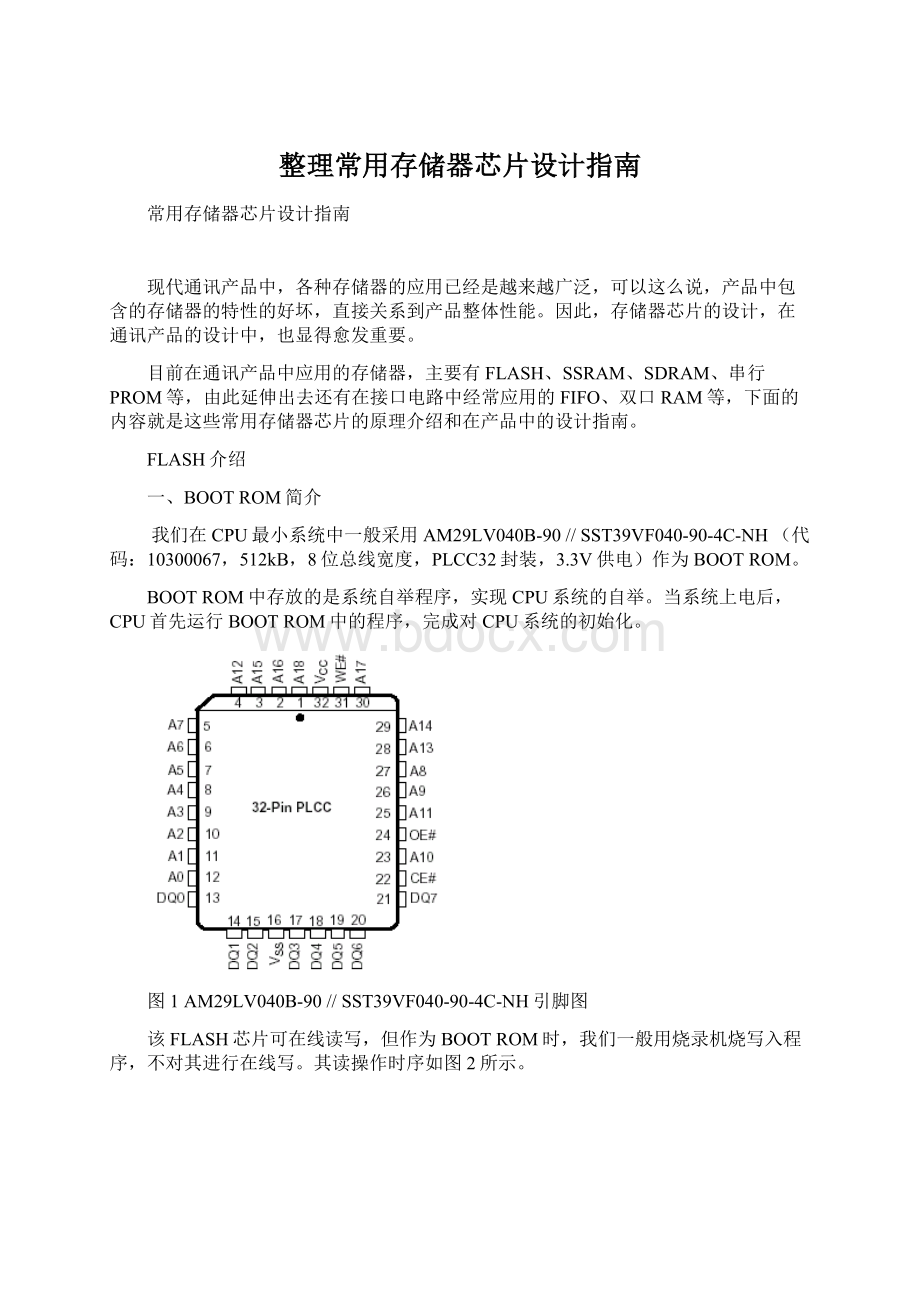

BOOTROM中存放的是系统自举程序,实现MPC860系统的自举。

当系统上电后,MPC860首先运行BOOTROM中的程序,该程序首先完成MPC860的初始化,然后根据参数,将FlashROM中的应用程序复制到SDRAM空间中,然后将控制权移交给该应用程序运行;

或准备应用程序加载,进入调试状态。

二:

大容量FLASH

由于FLASH具有在掉电情况下保持数据和容量大的特性,因此在公司的绝大多数运用中是用在CPU系统中存放系统的应用软件的,其运作过程如下:

系统上电后,首先BOOTROM的片选被选中,它里面放的是CPU的初始化程序,这样CPU就起来了,接着FLASH条的版本程序被下载到内存条中,从而整个软件就在CPU系统中运行起来,这样一来可以提高系统运行速度,二来是方便版本的管理。

因为一般来说系统支持远程加载和更新软件版本的功能,因此一般说来FLASH中必须开辟两个相同的区域,分别作为软件版本的保护和备份,这样一旦出现在系统动态加载软件失败时,能保证备用软件版本的正常启动,使系统不致崩溃。

典型介绍

生产FLASH的厂商很多,我们将以广为运用INTEL的28F128J3A芯片为例子来介绍,使大家对FLASH的操作有一个大致的了解,此芯片单片容量为128MBIT,(16BITX8M)。

由于此系列的FLASH(28F128J3,28F640J3,28F320J3)的引脚完全兼容,因此可以简单地通过器件替换提供128MBIT,64MBIT,32MBIT的容量。

28F128J3A芯片的管脚简单,分数据总线,地址总线,控制线,电源,地这么几类;

在使用的时候,只需接出使能,片选,写控制三根控制线即可,其他的控制线可以接固定电平,下图就是某CPU子卡的FLASH接法:

FLASH28F128J3A的操作是通过CPU分布各种命令来实现的,其命令是通过数据总线,地址总线,控制线呈现某个固定电平构成;

下表就是28F128J3A所有命令对应的各种信号的定义:

从上表可以看出28F128J3A大部分命令的实现分为两步实现:

例如Block_Erase命令,而普通的读命令Read_Array只要一步。

对于28F128J3A的某些操作,是非常简单的,例如读操作:

在芯片复位/上电后芯片默认为Read_Array模式,这样可以直接读取芯片的数据,但是如果在写FLASH或发布了其他命令后再想读取,那么就必须重新发布Read_Array命令才能读取;

对于其他的操作,尤其是分两步完成的命令,其操作是通过几个不同命令组合而成,具有一定的流程,并且在过程中经常需要不断地从FLASH读取状态信息以进行下一步操作来保证操作的正确。

在这里举两个操作流程的例子,通过这个例子,可以大致了解FLASH的操作:

第一个是Read_Status_Register命令,这个命令是用来读取芯片目前的状态,其他操作的流程中经常用到此命令以保证操作的正确,下图是进行Read_Status_Register命令的流图:

第二个例子是使用Write_to_Buffer命令过程,我们可以看到,在其过程中,我们可以看到需要发布Read_Status_Register命令检查芯片的状态信息以判断下一步:

FPGA配置用PROM简介

这类可编程ROM是专为FPGA加载配置所用。

其针对不同容量、型号、厂家的FPGA,其存储大小、性能不尽相同;

但其使用的电路、方法、时序基本相同。

而且,基本上是只可一次性擦写。

下面就以XILINX公司XC17S00A系列为例介绍一下。

图1XC17S00A引脚图

FPGA的配置数据是事先烧入PROM中的,FPGA采用的是主串行配置方式,上电后FPGA产生配置时钟给PROM,PROM则按照图3的时序对FPGA进行配置,当配置完成后FPGA的DONE信号就不使能PROM。

图2PROM配置FPGA电路

图3PROM的配置时序

我们公司这类器件没有一个是通用的,我们不推荐使用PROM配置这种方式。

最好用CPU进行FPGA配置,这样做增加了FPGA版本的灵活性,也大大降低了成本。

SSRAM介绍

SSRAM支持高性能CPU、DSP、网络套片等多种应用场合。

目前在公司多种产品中也有比较广泛的应用。

一、SSRAM的选用

在选用SSRAM时,一般需要考虑以下几个方面:

(1)根据设计需求、接口芯片的具体要求等确定SSRAM的芯片容量大小、数据宽度以及芯片速度等级;

(2)根据以上信息确定SSRAM型号,并尽可能在公司通用件库中选型;

(3)根据信号定义及信号时序等确定SSRAM及其接口芯片的具体的电路连接关系。

二、SSRAM的电路设计

1、概述

一般来说,SSRAM的信号主要包括以下几部分:

数据线、地址线、时钟以及写使能、输出使能等控制信号等。

在进行具体的电路设计时,一般只需将这些主要信号与其接口的特定芯片的对应信号直接对连即可,对于一些比较特殊的时序要求可以通过EPLD内做逻辑实现。

对于SSRAM上的一些不用的输入信号进行适当的上、下拉处理。

2、应用实例

下面以RNC中的一块单板ASC上采用的SSRAM为例,来说明SSRAM的具体应用。

首先根据设计要求,ASC单板上的ATM层UNI/NNI管理接口芯片ALM需要一片数据宽度为32位的SSRAM作为外部存储器。

综合考虑ALM外部存储器所需的容量大小以及目前SSRAM的价格因素及芯片可采购性等各方面因素,可以选择公司通用件CY7C1381B-100AC(代码12300217)来实现。

CY7C1381B-100AC数据宽度为32位,其信号线主要包括地址线、数据线、时钟和一些控制信号,其具体信号如下表所示。

信号类型

信号名

信号说明

处理方式

数据线

DQA[0:

8]

与其接口芯片直连

DQB[0:

DQC[0:

DQD[0:

地址线

A[0:

18]

时钟线

CLK

时钟输入,用来捕获芯片的所有同步输入

主要

控制信号

/OE

输出使能

/GW

全局写使能输入

/CE1

C.可能造成较大环境影响的建设项目,应当编制环境影响报告书

1.环境影响评价依据的环境标准体系芯片片选信号

下拉

CE2

1.建设项目环境影响报告书的内容上拉

(5)阐述划分评价单元的原则、分析过程等。

/CE3

6.提出安全对策措施建议/BWa,/BWb,/BWc,/BWd

1.筛选环境影响:

环境影响被筛选为三大类,一类是被剔除、不再作任何评价分析的影响,如内部的、小的以及能被控抑的影响;

另一类是需要作定性说明的影响,如那些大的但可能很不确定的影响;

最后一类才是那些需要并且能够量化和货币化的影响。

字节写选择输入

3)选择价值。

选择价值(OV)又称期权价值。

我们在利用环境资源的时候,并不希望它的功能很快消耗殆尽,也许会设想未来该资源的使用价值会更大。

上拉(因为使用/GW信号,/BWa,/BWb,/BWc,/BWd,/BWE将被忽略)

/BWE

字节写使能

上拉(理由同上)

/ADV

有效时,在burst访问模式时地址自动增加

上拉或下拉,可根据实际需要通过电阻选焊实现

/ADSC

控制器地址选通

上拉或下拉,本应用中下拉

/ADSP

处理器地址选通

上拉或下拉,本应用中上拉

MODE

Burst序列选择,接地时选择线性burst顺序,悬空或上拉时选择交织burst

上拉或下拉,可根据实际需要通过电阻选焊,本应用中选择下拉

分析ALM及所选SSRAM的具体接口信号可知,电路连接方面基本上只要将二者数据线、地址线、时钟以及几个主要控制信号直连,其他的信号做一些上下拉处理即可。

如下图所示,给出了二者接口的电路连接框图。

同时在表1中最后一列也给出了在该例中SSRAM各具体信号的相应处理方式。

SDRAM应用

存储器是容量数据处理电路的重要组成部分。

随着数据处理技术的进一步发展,对于存储器的容量和性能提出了越来越高的要求。

同步动态随机存储器SDRAM(SynchronousDynamicRandomAccessMemory)因其容量大、读写速度快、支持突发式读写及相对低廉的价格而得到了广泛的应用。

SDRAM的控制比较复杂,其接口电路设计是关键。

1.SDRAM的主要控制信号和基本命令

SDRAM的主要控制信号为:

·

CS:

片选使能信号,低电平有效;

RAS:

行地址选通信号,低电平有效;

CAS:

列地址选通信号,低电平有效;

WE:

写使能信号,低电平有效。

SDRAM的基本命令及主要控制信号见表1。

表1SDRAM基本操作及控制信号

命

令

名

称

CS

RAS

CAS

WE

命令禁止(NOP:

Commandinhibit)

H

X

空操作(NOP:

Nooperation)

L

激活操作(ACT:

Selectbankandactiverow)

读操作(READ:

Selectbankandcolumn,andstartREADburst)

写操作(WRITE:

Selectbankandcolumn,andstartWRITEburst)

突发操作停止(BTR:

Burstterminate)

预充电(PRE:

Deactiverowinbankorbanks)

自动刷新或自我刷新(REF:

Autorefreshorselfrefresh)

配置模式寄存器(LMR:

Loadmoderegister)

所有的操作控制信号、输入输出数据都与外部时钟同步。

一个完备的SDRAM接口很复杂。

对于常规的SDRAM应用来说,处理的事件相对来说比较简单,因而可以简化设计而不影响性能。

接口电路SDRAM的主要操作可以分为:

初始化操作、读操作、写操作、自动刷新操作。

(1)初始化操作

SDRAM上电一段时间后,经过初始化操作才可以进入正常工作过程。

初始化主要完成预充电、自动刷新模式寄存器的配置。

(2)激活操作

SDRAM在进行读写之前,必须将位于某一个BANK或所有BANK中的行(row)地址进行激活,之后才能进行对相应区域进行读写,激活操作中,地址线上出现的将是行地址和BANK选择地址。

(3)读写操作

读写操作就是对SDRAM进行数据的存取,在读写操作期间,地址线上出现的将是列地址(COLUMN)和BANK选择地址。

读写操作可以进行单字节的操作,也可以进行BURST操作。

(4)刷新操作

动态存储器(DynamicRAM)都存在刷新问题。

这里主要采用自动刷新方式,每隔一段时间向SDRAM发一条刷新命令。

2.SDRAM应用介绍

目前我们的产品中,在应用到微处理器时,基本上都要使用SDRAM作为处理器的主要内存,由于技术的不断发展,现在的CPU对SDRAM的要求也越来越高,主要体现在容量和速度上的提高,下面以美光公司的8M16为例,来介绍一下SDRAM在通讯系统中的具体应用。

MT8M16是美光公司在sdram上的一个代表产品,主要特点如下:

1)128MBIT容量:

2MX16X4BANKS

2)速度有10ns和7ns两种,最新的还有5ns,支持最高的时钟频率可达200MHZ。

3)物理地址线A0-A11总共为12根,行列地址线复用,其中,行地址线为A0-A11,列地址线为A0-A9,因此总共的逻辑地址共为22根,数据线宽为16bit,总容量为8MX16bit=128Mbit。

4)内部有4个BANK,通过和控制器相应的输出控制线相连,即可实现整个区间的访问。

下图是用MOTOROLA的MPC8260和MT8M16相连接的示意图:

其中地址线和数据线可以按照常规的CPU接外设的方法来实现,要注意的是,对于SDRAM来说,行列地址线是复用的,控制线主要包括:

1)片选CS,选中SDRAM,实际上通过对cpu寄存器的设置就可以通过该片选信号决定了该SDRAM在CPU的地址空间中的基址

2)时钟信号。

3)读写信号

4)其他:

包括数据输出屏蔽,时钟使能等信号,这些都可以由cpu相应的管脚来控制。

FIFO

FIFO(firstinfirstoutmemory)是一种先进先出的存储器,广泛应用于接口电路中的数据缓冲,数据暂存,在现代通讯产品中,许多数据的处理都是要经过许多级处理器的树立阶段,在这些阶段的结合过程中,往往需要进行数据的缓冲,这时,我们可以充分利用FIFO进行设计,使得我们的数据处理流程能够更加合理和灵活。

FIFO一般分为同步FIFO和异步FIFO,同步FIFO的读写都是和读写时钟保持同步的,而异步FIFO的读写就没有时钟同步的概念了。

一般来说,FIFO的主要信号有:

✓读写数据线:

有9位的,也有18位的。

✓读写使能线:

只有有效的时候才能进行读写。

✓FIFO满标志(full)和FIFO空标志(empty):

当满(full)标志有效时,表明目前FIFO不能在进行写操作,只有经过若干读FIFO操作之后,full标志无效时才可以进行写FIFO操作;

当空(empty)标志有效时,表明目前FIFO不能进行读操作,只有经过若干写FIFO操作之后,才可以进行读FIFO操作。

目前FIFO芯片的主要性能主要体现在:

数据宽度(9位和18位),存贮容量(从几十K到几M字节),存储速度(15ns,10ns,等),我们在具体的应用中,应该根据自己单板上的实际需求,合理的选择相应的芯片进行设计。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 整理 常用 存储器 芯片 设计 指南

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《雷雨》中的蘩漪人物形象分析 1.docx

《雷雨》中的蘩漪人物形象分析 1.docx