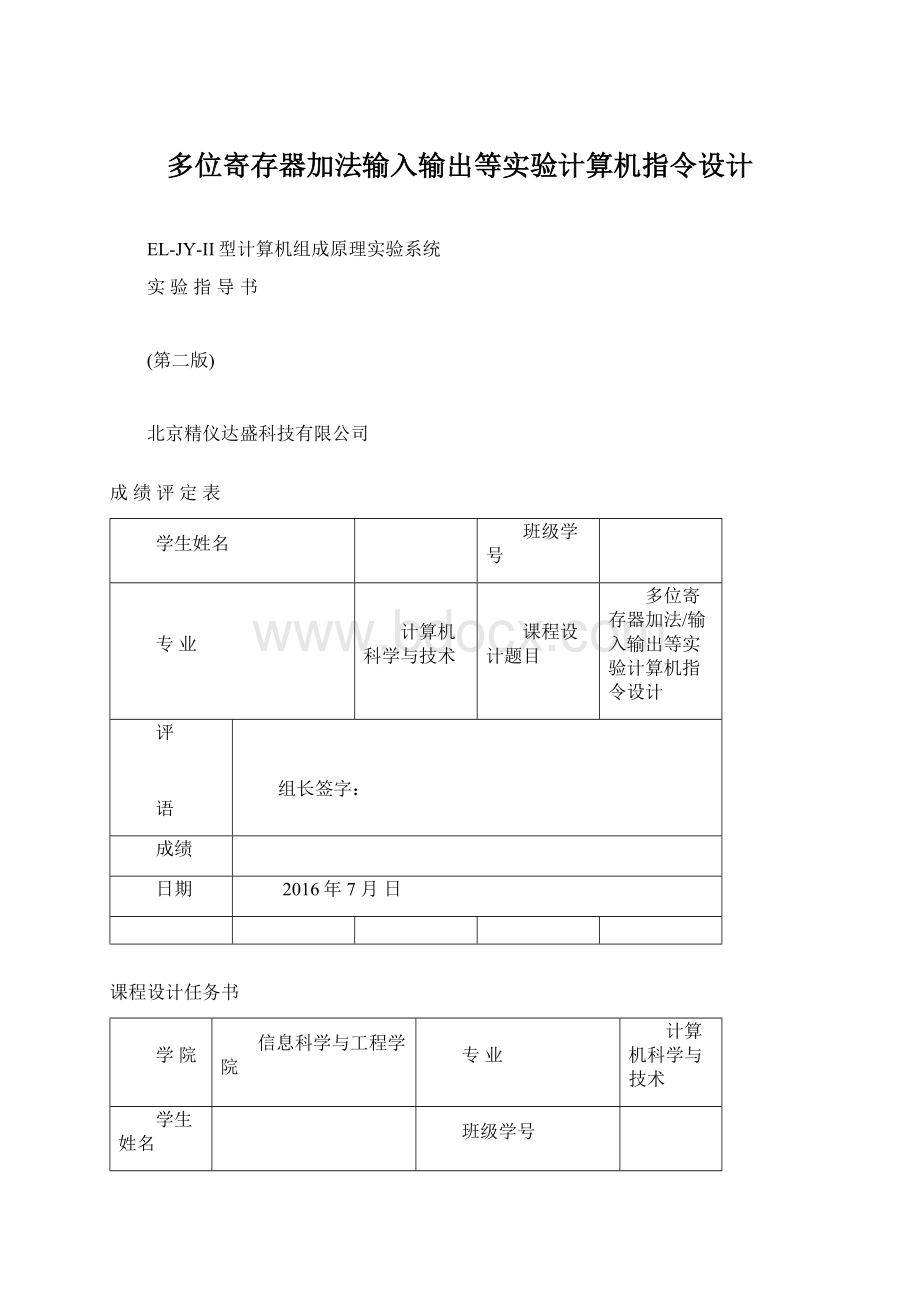

多位寄存器加法输入输出等实验计算机指令设计Word文件下载.docx

多位寄存器加法输入输出等实验计算机指令设计Word文件下载.docx

- 文档编号:18171122

- 上传时间:2022-12-13

- 格式:DOCX

- 页数:29

- 大小:3.52MB

多位寄存器加法输入输出等实验计算机指令设计Word文件下载.docx

《多位寄存器加法输入输出等实验计算机指令设计Word文件下载.docx》由会员分享,可在线阅读,更多相关《多位寄存器加法输入输出等实验计算机指令设计Word文件下载.docx(29页珍藏版)》请在冰豆网上搜索。

1.2.2指令格式7

1.2.3指令系统8

1.3微指令编码的格式设计9

1.4设计指令的执行流程,画出微程序流程图11

1.5确定微程序控制方式13

1.5.1微程序入口地址形成方法13

1.5.2微程序顺序控制方法13

1.6微程序编码14

2.实验计算机的组装17

2.1实验计算机的设计(各种芯片管脚和功能图在附录中列出)17

2.2实验计算机的组装17

3.实验计算机的调试21

3.1调试前的准备21

3.1.1按照实验指导说明书连接硬件系统21

3.1.2启动实验软件,打开实验课题菜单,选中实验课题打开实验课题参数对话窗口21

3.2调试步骤和调试结果21

3.3结果分析22

3.4设计和调试中遇到的问题和体会24

3.4.1出错24

3.4.2体会24

4.附录25

4.1各种芯片管脚和功能图25

参考文献29

1.实验计算机的设计

1.1设计整机逻辑框图并画出逻辑框图

(一)模型机的组成:

(1)模型机是由运算器,控制器,存储器,输入设备,输出设备五大部分组成。

①运算器又是有299,74LS181完成控制信号功能的算逻部件,暂存器LDR1,LDR2,及三个通用寄存器Ax,Bx,Cx等组成。

②控制器由程序计数器PC、指令寄存器、地址寄存器、时序电路、控制存储器及相应的译码电路组成。

③存储器RAM是通过CE和W/R两个微命令来完成数据和程序的的存放功能的。

④输出设备有两位LED数码管和W/R控制完成的。

(2)计算机由基板和CPU板两部分组成:

①基板:

本部分是8位机和16位机的公共部分,包括以下几个部分:

数据输入输出、显示及监控,脉冲源及时序电路,数据和地址总线,外设控制电路,单片机控制电路和键盘操作部分,与PC机通讯的接口,主存器和电源,CPLD实验板,自由实验区。

②CPU板:

本板分为8位机和16位机两种,除数据字长分为8位和16位外,都包括以下部分:

微程序控制器,运算器,寄存器堆,程序计数器,指令寄存器,

指令译码电路,地址寄存器,数据,地址和控制总线。

运算器部分:

由算术逻辑单元ALU74LS181(U29、U30)、暂存器74LS273(U27、U28)、三态门74LS244(U31)和进位控制电路GAL芯片(U32)等组成。

存储器部分:

由静态存储器1片6116(2K×

8)构成。

其数据线D0~D7接到数据总线,地址线A0~A7由地址锁存器(74LS273)给出。

黄色地址显示灯MA7-MA0与地址总线相连,显示地址总线的内容。

数据经三态门(74LS245)连至数据总线,分时给出地址和数据。

(二)本系统的结构组成为:

本板分为8位机和16位机两种,除数据字长分别为8位和16位以外,都包括以下几个部分:

微程序控制器,运算器,寄存器堆,程序计数器,指令寄存器,指令译码电路,地址寄存器,数据、地址和控制总线。

基板:

数据输入和输出,显示及监控,脉冲源及时序电路,数据和地址总线,外设控制实验电路,单片机控制电路和键盘操作部分,与PC机通讯的接口,主存储器,电源,CPLD实验板(选件),自由实验区(面包板)。

运算器:

由算术逻辑单元(ALU)、累加寄存器、数据缓冲寄存器、和状态条件寄存器组成,它是数据加工处理部件。

相对控制器而言,运算器接受控制器的命令而进行动作,即运算器所进行的全部操作都是有控制器发出的控制信号来指挥的,所以它是执行部件.

存储器:

是保存或“记忆”解题的原始数据和解题步骤。

在运算前需要把参加运算的数据和解题步骤通过输入设备送到存储器中保存。

微程序控制器:

控制部件通过控制线向执行部件发出各种控制命令,通常把这种控制命令叫做微命令,而执行部件接受命令后的操作叫做微操作。

本系统有两种外部I/O设备,一种是二进制代码开关,它作为输入设备;

另一种是数码管,它作为输出设备。

输入时,二进制开关数据直接经过三态门送到数据总线上,只要开关状态不变,输入的信息也不变。

输出时,将输出数据送到外部数据总线上,当写信号(W/R)有效时,将数据打入输出锁存器,驱动数码管显示。

整机逻辑框图如图1.1所示:

MMS1S0

数据总线(D_BUS)

74299

LPC

299-G

程序计数器PC

ALU-G

LOADPC-G

MCNALUS3S2S1S0

数据暂存器LT1数据暂存器LT2LAR地址寄存器AR

地址总线(ADDR_BUS)

LDR1LDR2存储器(MEM)READ

WRITE

寄存器R0寄存器R1寄存器R2微控器脉冲源及时序

LR0R0GLR1R1GLR2R2G指令寄存器IR

C-GLDIR

输入设备W/R

控制门输出设备

数据LED-G

控制信号

图1.1整机逻辑框图

1.2指令系统的设计

1.2.1数据格式

本实验计算机采用定点补码表示法表示数据,字长为8位,其格式如下:

7

654321

符号

尾数

其中第7位为符号位,数值表示范围是:

-1≤X<

1

1.2.2指令格式

1)算术逻辑指令

设计9条算术逻辑指令并用单字节表示,寻址方式采用寄存器直接寻址其格式如下:

7654

32

10

OP-CODE

rs

rd

其中OP-CODE为操作码,rs为源寄存器,rd为目的寄存器,并规定:

Rs或rd

选定寄存器

00

R0

01

R1

10

R2

9条算术逻辑指令的名称、功能和具体格式见表1.1。

2)访问及转移指令

本机设计有2条访问指令,即存数(STA)、取数(LDA),2条转移指令,即无条件转移(JMP)、结果为零或有进位转移指令(BZC),指令格式如下:

76

54

M

Rd

D

其中OP-CODE为操作码,rd为目的寄存器地址(LDA、STA指令使用)。

D为位移量(正负均可),M为寻址模式,其定义如下:

寻址模式M

有效地址E

说明

11

E=D

E=(D)

E=(RI)+D

E=(PC)+D

直接寻址

间接寻址

RI变址寻址

相对寻址

本机规定变址寄存器RI指定为寄存器R2。

3)I/O指令

输入(IN)和输出(OUT)指令采用单字节指令,其格式如下:

addr

其中,addr=01时,选中“数据输入电路”中的开关组作为输入设备,addr=10时,选中“输出显示电路”中的数码管作为输出设备。

4)停机指令

指令格式如下:

1.2.3指令系统

本机共有16条基本指令,其中算术逻辑指令9条,访问内存指令和程序控制指令4条。

输入输出指令2条,其它指令1条。

表8-1列出了各条指令的格式、汇编符号和指令功能。

表1.1指令格式

汇编符号

指令的格式

功能

CLRrd

MOVrs,rd

ADCrs,rd

SBCrs,rd

011100rd

1000rsrd

1001rs rd

1010rsrd

0rd

rsrd

rs+rd+cyrd

rs-rd-cyrd

INCrd

ANDrs,rd

COMrd

RRCrs,rd

1011rsrd

1100rsrd

1101rsrd

1110rsrd

rd+1rd

rs∧rdrd

rdrd

cyrs

rsrd

RLCrs,rd

1111rsrd

LDAM,D,rd

00M00rd

D

Ers

STAM,D,rd

00M01rd

D

rdE

JMPM,D

00 M 10 00

D

E PC

BZCM,D

00M1100

D

当CY=1或Z=1时,

EPC

INaddr,rd

OUTaddr,rd

010001rd

010110rd

addrrd

rdaddr

HALT

01100000

停机

1.3微指令编码的格式设计

本系统设计的微指令采用水平型微指令格式,字长共24位,其控制位顺序如下:

24

23

22

21

20

19

18

17

16

151413

121110

987

6

5

4

3

2

S3

S2

S1

S0

Cn

WE

1A

1B

F1

F2

F3

uA5

uA4

uA3

uA2

uA1

uA0

其中前18位为操作控制字段和测试字段。

uA5-uA0为6位的下地址字段微地址。

微指令中个控制位的含义如下:

S3、S2、S1、S0、M、Cn是控制运算器的逻辑和算术运算的微命令。

02

03

04

WE是写内存的微命令,状态“1”有效。

1A、1B是输入电路选通、内存RAM选通、输出LED选通控制微命令,分别对应状态“11”、“10”、“01”。

状态“00”为无效。

F1、F2、F3为三个译码字段,分别由三个控制位经指令译码电路74138译码输出8种状态,前7种状态分别对应一组互斥性微命令中的一个,状态“111”为无效。

F3字段包含P1-P4四个测试字位。

其功能是根据机器指令代码及相应微指令代码进行译码测试,使微程序转入相应的微地址入囗,从而实现微程序的顺序、分支、循环运行。

F1、F2、F3三个字段的编码方案如表1.2

表1.2F1,F2,F3三个字段的编码方案表

F1字段

F2字段

F3字段

选择

000

LDRi

RAG

P1

001

LOAD

ALU-G

AR

010

LDR2

RCG

P3

011

100

LDR1

RBG

P2

101

LAR

PC-G

LPC

110

LDIR

299-G

P4

其中微命令LDRi表示写寄存器操作。

微命令LOAD表示程序计数器PC写操作。

微命令LDR2表示数据暂存器LT2写操作。

微命令LDR1表示数据暂存器LT1写操作。

微命令LAR表示地址寄存器AR写操作。

微命令LDIR表示指令寄存器写操作。

微命令RAG表示源寄存器读操作。

微命令ALU-G表示运算器输出操作。

微命令RCG表示目的寄存器读操作。

微命令PC-G表示程序计数器PC读操作。

微命令LPC表示程序计数器PC选通操作。

微命令299-G表示移位寄存器读写操作。

微命令RBG表示变址寄存器读操作。

1.4设计指令的执行流程,画出微程序流程图

每条指令对应的微程序流程图

(1)输入指令IN

图1.2IN指令的微程序流程图

(2)输出指令OUT

图1.3OUT指令的微程序流程图

(3)

转移指令JMP

图1.4JMP指令相对寻址的微程序流程图

(4)加法指令ADD

图1.5ADD指令相对寻址的微程序流程图

1.5确定微程序控制方式

1.5.1微程序入口地址形成方法

采用多路转移方式,根据判别测试条件,通过微地址形成电路使微程序转入相应的微地址入口。

本系统有3个判别测试位:

P4判别测试位是根据指令译码输入CA1、CA2的状态为测试条件,通过修改下地址字段微地址的A0、A1位产生3路分支转移,使微程序分别转移到写机器指令、读机器指令、和执行机器指令三种状态的微程序的入口。

P1判别测试位是根据指令中的前4位操作码IR7、IR6、IR5、IR4的状态为测试条件,通过修改下地址字段微地址的A3、A2、A1、A0位产生16路分支转移,使微程序分别转移到IN指令、ADD指令、MOV指令、OUT指令、RRC指令等16条机器指令执行阶段的微程序的入口。

P2判别测试位是根据指令中的2位操作码IR3、IR2的状态为测试条件,通过修改下地址字段微地址的A1、A0位产生4路分支转移,使微程序分别转移到LDA指令、STA指令、BZC指令和JMP指令4条机器指令执行阶段的微程序的入口。

1.5.2微程序顺序控制方法

微程序顺序控制方式也即微程序执行过程中下一条微指令地址的确定方式。

常用的有两种方式:

计数增量方式和“下地址场”断定方式。

计数增量方式是指微程序在执行过程中,通过微程序控制部件中的微地址计数器MPC增量计数,来产生下一条微指令地址。

因此,采用这种方式的微指令格式中可以不设置“下地址场”字段,微程序存储在控存的若干个连续单元中。

“下地址场”断定方式是指微程序在执行过程中,通过微程序控制部件中的微地址形成电路,直接接受微指令中“下地址场”字段的信息,来产生下一条微指令地址。

因此,采用这种方式的微指令格式中设有“下地址场”字段,一条机器指令所对应的微程序在控存中可以不连续存放。

本实验计算机的顺序控制是采用“下地址场”断定方式。

无论是在微程序的顺序执行过程中,还是最后一条微指令执行结束之后进入下一条机器指令的取指过程,都是由微指令中“下地址场”字段的微地址,通过微程序控制部件中的微地址形成电路,直接来产生下一条微指令地址。

微程序控制部件组成结构示意图如图1.6。

图1.6微程序控制部件组成结构示意图

1.6微程序编码

表1.3微代码在控存中的分布表

微地址(八进制)

微地址(二进制)

微代码(十六进制)

000000

007F88

000001

005B42

000010

016FFD

000011

014FC4

000100

015F20

05

000101

015FC6

06

000110

014FC7

07

000111

001000

005B4A

001001

005B4C

12

001010

014FFB

13

001011

007FC1

14

001100

01CFFC

15

001101

014FCE

001110

0025CF

001111

9453E5

010000

005B43

010001

005B45

010010

005B4D

010011

005B66

010100

018FC1

25

010101

02F5C1

26

010110

007FD6

27

010111

3C03C1

30

011000

0001C1

31

011001

0041EA

32

011010

0021EC

33

011011

0041F2

34

011100

0041F3

35

011101

0041F6

36

011110

3001F7

37

011111

3001F9

40

100000

010FC1

41

100001

0379C1

42

100010

011F41

43

100011

007EA4

44

100100

45

100101

844920

46

100110

014FE7

47

100111

002BE8

50

10100

9459E9

51

101001

944920

52

101010

0025EB

53

101011

9403FE

54

101100

0049ED

55

101101

0449EE

56

101110

0C49EF

57

101111

0049F0

60

110000

0C7F31

61

110001

9403C1

62

110010

0003C1

63

110011

0025F5

64

110100

041341

65

110101

B803C1

66

110110

0C03C1

67

110111

287DF8

70

111000

000DC1

71

111001

187DFA

72

111010

73

111011

06F3C8

74

111100

FF73C9

75

111101

016E10

76

111110

0041C1

2.实验计算机的组装

2.1实验计算机的设计(各种芯片管脚和功能图在附录中列出)

运算器部分由算术逻辑单元ALU74LS181(U29、U30)、暂存器74LS273(U27、U28)、三态门74LS244(U31)和进位控制电路GAL芯片(U32)等组成。

电路图见图2.1。

图2.1运算器部分电路图

2.2实验计算机的组装

根据各部分的组成,连线步骤如下:

R0G---R2G(寄存器堆电路)~R0G---R2G(指令寄存器电路)

LR0---LR2(寄存器堆电路)~LR0---LR2(指令寄存器电路)

IR2---IR7(指令寄存器电路)~IR2---IR7(指令寄存器电路)

IO0---IO3(指令寄存器电路)~IO0---IO3(指令寄存器电路)

CA1(指令寄存器电路)~E4(控制总线)

CA2(指令寄存器电路)~E5(控制总线)

Y2(I/O控制电路)~D-G(输出显示电路)

Y1(I/O控制电路)~CE(主存储器电路)

WR(输出显示电路)~W/R(读写控制电路)

F1---F4(控制总线)~T1---T4(读写控制电路)

AD7---AD0(地址总线)~MA7---MA0(主存储器电路)

WE(主存储器电路)~W/R(读写控制电路)

ALUJ2(运算器电路)~BD7---BD0(数据总线)

ALUJ1(运算器电路)~BD7---BD0(数据总线)

PCJ1(程序计数器电路)~BD7---BD0(数据总线)

RJ1(寄存器堆电路)~BD7---BD0(数据总线)

MC16---MC17(微程序控制器电路)~1A---1B(I/O控制电路)

299-G(微程序控制器电路)~299-G(运算器电路)

MC24---MC19(微程序控制器电路)~S3---CN(运算器电路)

LDR1(微程序控制器电路)~LDR1(运算器电路)

LDR2(微程序控制器电路)~LDR2(运算器电路)

ALU-G(微程序控制器电路)~ALU-G(运算器电路)

AR(微程序控制器电路)~AR(运算器电路)

PC-G(微程序控制器电路)~PC-G(程序计数器电路)

LOAD(微程序控制器电路)~LOAD(程序计数器电路)

LPC(微程序控制器电路)~LPC(程序计数器电路)

LRi(微程序控制器电路)~LRi(指令译码电路)

RAG---RCG(微程序控制器电路)~RAG---RCG(指令译码电路)

SA5---SA0(微程序控制器电路)~SA5---SA0(指令译码电路)

P1---P4(微程序控制器电路)~P1---P4(指令译码电路)

LDIR(微程序控制器电路)~LDIR(指令寄存器电路)

UAJ1(微程序控制器电路)~C1---C6(控制总线)

MC18(微程序控制器电路)~WE(读写控制电路)

LAR(微程序控制器电路)~LAR(地址寄存器电路)

D0---D7(输出显示电路)~BD7---BD0(数据总线)

MD7---MD0(主存储器电路)~BD7---BD0(数据总线)

按照组装图将各接口处用连接线连接起来,连线时应按如下方法:

对于横排座,应使排线插头上的箭头面

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 寄存器 加法 输入输出 实验 计算机 指令 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《雷雨》中的蘩漪人物形象分析 1.docx

《雷雨》中的蘩漪人物形象分析 1.docx