Quartus常见错误警告分析Word下载.docx

Quartus常见错误警告分析Word下载.docx

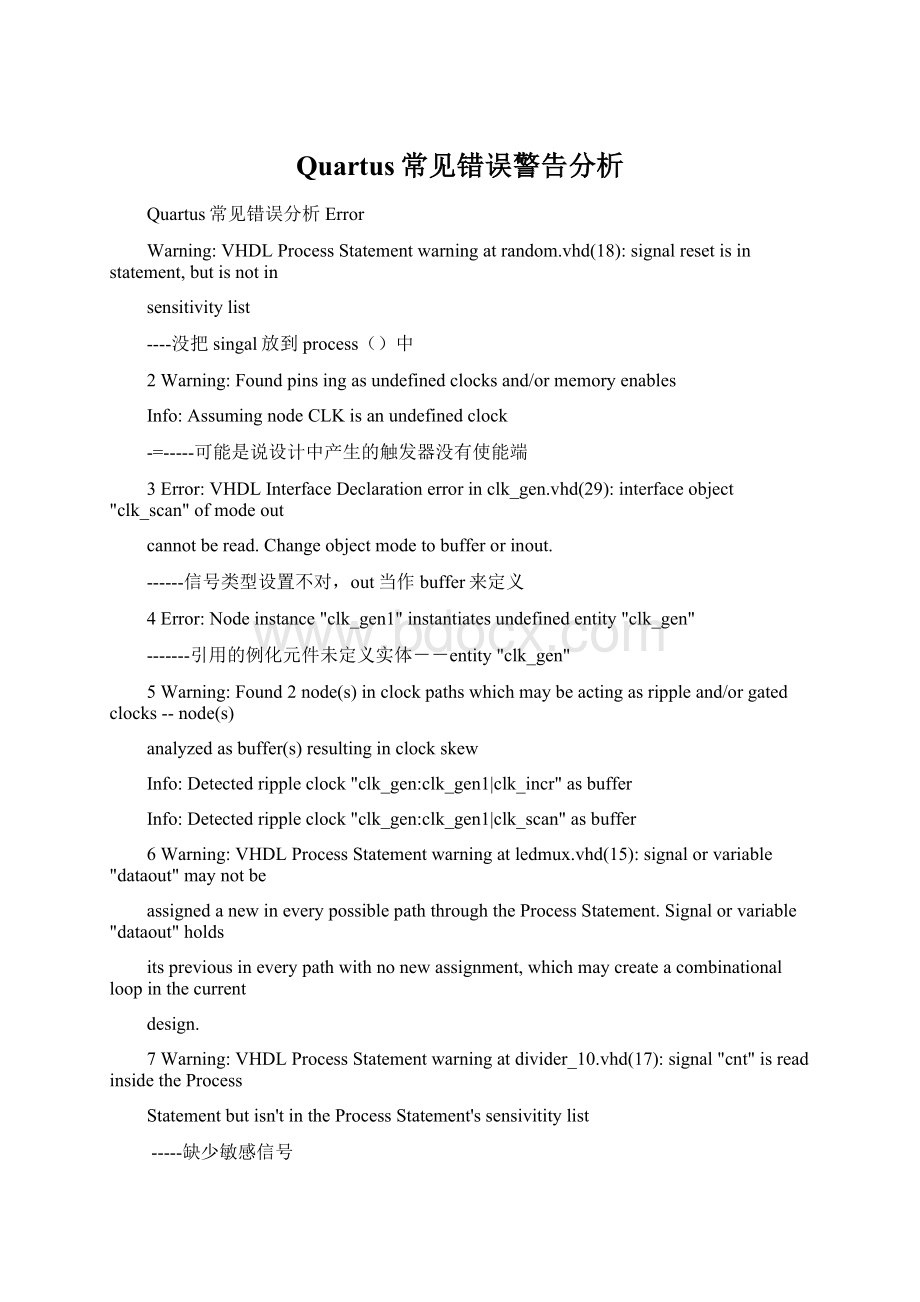

- 文档编号:18121144

- 上传时间:2022-12-13

- 格式:DOCX

- 页数:8

- 大小:20.63KB

Quartus常见错误警告分析Word下载.docx

《Quartus常见错误警告分析Word下载.docx》由会员分享,可在线阅读,更多相关《Quartus常见错误警告分析Word下载.docx(8页珍藏版)》请在冰豆网上搜索。

signalorvariable"

dataout"

maynotbe

assignedanewineverypossiblepaththroughtheProcessStatement.Signalorvariable"

holds

itspreviousineverypathwithnonewassignment,whichmaycreateacombinationalloopinthecurrent

design.

7Warning:

VHDLProcessStatementwarningatdivider_10.vhd(17):

signal"

cnt"

isreadinsidetheProcess

Statementbutisn'

tintheProcessStatement'

ssensivititylist

-----缺少敏感信号

8Warning:

Noclocktransitionon"

counter_bcd7:

counter_counter_clk|q_sig[3]"

register

9Warning:

Reducedregister"

withstuckclockporttostuck

GND

10Warning:

Circuitmaynotoperate.Detected1non-operationalpath(s)clockedbyclock"

class[1]"

with

clockskewlargerthandatadelay.SeeCompilationReportfordetails.

11Warning:

sign"

12Error:

VHDLerroratcounter_clk.vhd(90):

actualport"

class"

ofmode"

in"

cannotbeassociatedwith

formalport"

out"

------两者不能连接起来

13Warning:

Ignorednodeinvectorsourcefile.Can'

tfindcorrespondingnodename"

class_sig[2]"

in

------没有编写testbench文件,或者没有编辑输入变量的值testbench里是元件申明和映射

14Error:

VHDLBindingIndicationerroratfreqdetect_top.vhd(19):

port"

indesignentitydoes

nothavestd_logic_vectortypethatisspecifiedforthesamegenericintheassociatedcomponent

---在相关的元件里没有当前文件所定义的类型

15Error:

VHDLerrorattongbu.vhd(16):

can'

tinferregisterforsignal"

gate"

becausesignaldoesnot

holditsoutsideclockedge

16Warning:

Foundclockhightimeviolationat1000.0nsonregister

"

|fcounter|lpm_counter:

temp_rtl_0|dffs[4]"

17Warning:

Compilerpacked,optimizedorsynthesizedawaynode"

temp[19]"

.Ignoredvectorsourcefile

node.

---"

被优化掉了

18Warning:

gate~reg0"

withstuckdata_inporttostuckGND

19Warning:

Designcontains2inputpin(s)thatdonotdrivelogic

Nooutputdependentoninputpin"

clk"

------输出信号与输入信号无关,

20Warning:

Foundclockhightimeviolationat16625.0nsonregister"

|impulcomp|gate1"

21Error:

VHDLerroratimpulcomp.vhd(19):

timplementclockenableconditionspecifiedusingbinary

operator"

or"

22Error:

VHDLAssociationListerroratperiod_counter.vhd(38):

actualparameterassignedtoformal

parameter"

alarm"

butformalparameterisnotdeclared

-------连接表错误,形参"

赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

23Error:

Ignoredconstructbehavieratperiod_counter.vhd(15)becauseofpreviouserrors

--------因为前一个错误而导致的错误

24Error:

VHDLerroratperiod_counter.vhd(38):

typeofidentifier"

doesnotagreewithitsusage

asstd_logictype

--------"

的定义类型与使用的类型不一致

25Error:

VHDLerroratshift_reg.vhd(24):

tsynthesizelogicforstatementwithconditionsthat

testfortheedgesofmultipleclocks

-------同一进程中含有两个或多个if(edge)条件,(一个进程中之能有一个时钟沿)

26Error:

Can'

tresolvemultipleconstantdriversfornet"

datain_reg[22]"

atshift_reg.vhd(19)

27can'

num[0]"

becausesignaldoesnotholditsoutsideclockedge

28Error:

telaboratetop-leveluserhierarchy

29Error:

cs_in"

atled_key.vhd(32)----------有两

个以上赋值语句,不能确定“cs_in”的值,

30Warning:

over"

indesign.

---------------在源文件中找不到对应的节点“over”。

31Error:

taccessJTAGchain

无法找到下载链

32Info:

Assumingnode"

isanundefinedclock

Quartus警告分析Warning

1.Foundclock-sensitivechangeduringactiveclockedgeattime

<

time>

onregister"

name>

原因:

vectorsourcefile中时钟敏感信号(如:

数据,允许端,清零,同步加

载等)在时钟的边缘同时变化。

而时钟敏感信号是不能在时钟边沿变化的。

其后

果为导致结果不正确。

措施:

编辑vectorsourcefile

2.VerilogHDLassignmentwarningat<

location>

:

truncated

withsize<

number>

tomatchsizeoftarget(<

原因:

在HDL设计中对目标的位数进行了设定,如:

reg[4:

0]a;

而默认为32位,

将位数裁定到合适的大小

措施:

如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数

3.Allreachableassignmentstodata_out(10)assign'

0'

register

removedbyoptimization

经过综合器优化后,输出端口已经不起作用了

4.Following9pinshavenothing,GND,orVCCdrivingdatainport--

changestothisconnectivitymaychangefittingresults

第9脚,空或接地或接上了电源

有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

如果你的设计中这些端口就是这样用的,那便可以不理会这些warning

5.Foundpinsingasundefinedclocksand/ormemoryenables

是你作为时钟的PIN没有约束信息。

可以对相应的PIN做一下设定就行了。

主要是指你的某些管脚在电路当中起到了时钟管脚的作用,比如flip-flop的clk

管脚,而此管脚没有时钟约束,因此QuartusII把“clk”作为未定义的时钟。

如果clk不是时钟,可以加“notclock”的约束;

如果是,可以在clock

setting当中加入;

在某些对时钟要求不很高的情况下,可以忽略此警告或在这

里修改:

Assignments>

Timinganalysissettings...>

Individual

clocks...>

...

6.TimingcharacteristicsofdeviceEPM570T144C5arepreliminary

因为MAXII是比較新的元件在QuartusII中的時序并不是正式版的,要

等ServicePack

只影响Quartus的Waveform

7.Warning:

ClocklatencyanalysisforPLLoffsetsissupportedforthe

currentdevicefamily,butisnotenabled

将setting中的timingRequirements&

Option-->

MoreTiming

Setting-->

setting-->

EnableClockLatency中的on改成OFF

8.Foundclockhightimeviolationat14.8nsonregister

|counter|lpm_counter:

count1_rtl_0|dffs[11]"

违反了steup/hold时间,应该是后仿真,看看波形设置是否和时钟沿符

合steup/hold时间

在中间加个寄存器可能可以解决问题

9.warning:

circuitmaynotoperate.detected46non-operational

pathsclockedbyclockclk44withclockskewlargerthandatadelay

时钟抖动大于数据延时,当时钟很快,而if等类的层次过多就会出现这种问

题,但这个问题多是在器件的最高频率中才会出现

timingRequirements&

Options-->

Defaultrequired

fmax改小一些,如改到50MHZ

10.Designcontains<

inputpin(s)thatdonotdrivelogic

输入引脚没有驱动逻辑(驱动其他引脚),所有的输入引脚需要有输入逻辑

如果这种情况是故意的,无须理会,如果非故意,输入逻辑驱动.

11.Warning:

Foundclockhightimeviolationat8.9nsonnode

'

TEST3.CLK'

FF中输入的PLS的保持时间过短

在FF中设置较高的时钟频率

12.Warning:

Found10node(s)inclockpathswhichmaybeactingas

rippleand/orgatedclocks--node(s)analyzedasbuffer(s)resultingin

clockskew

如果你用的CPLD只有一组全局时钟时,用全局时钟分频产生的另一个时

钟在布线中当作信号处理,不能保证低的时钟歪斜(SKEW)。

会造成在这个时钟

上工作的时序电路不可靠,甚至每次布线产生的问题都不一样。

如果用有两组以上全局时钟的FPGA芯片,可以把第二个全局时钟作为另

一个时钟用,可以解决这个问题。

13.CriticalWarning:

Timingrequirementswerenotmet.SeeReport

windowfordetails.

时序要求未满足,

双击CompilationReport-->

TimeAnalyzer-->

红色部分(如clock

setup:

clk'

等)-->

左键单击listpath,查看fmax的SLACKREPORT再根据

提示解决,有可能是程序的算法问题

14.Can'

tachieveminimumsetupandholdrequirement<

text>

along

path(s).SeeReportwindowfordetails.

时序分析发现一定数量的路径违背了最小的建立和保持时间,与时钟歪斜

有关,一般是由于多时钟引起的

利用CompilationReport-->

hold:

等),在slack中观察是holdtime为负值还是setuptime为负值,

然后在:

Assignment-->

AssignmentEditor-->

To中增加时钟名(from

nodefinder),AssignmentName中增加

和多时钟有关的Multicycle和MulticycleHold选项,如holdtime为负,可

使Multicyclehold的值>

multicycle,如设为2和1。

15:

tanalyzefile--fileE:

//quartusii/*/*.vismissing

试图编译一个不存在的文件,该文件可能被改名或者删除了

不管他,没什么影响

16.Warning:

tfindsignalinvectorsourcefileforinputpin

|whole|clk10m

因为你的波形仿真文件(vectorsourcefile)中并没有把所有的输入

信号(inputpin)加进去,对于每一个输入都需要有激励源的

17.Error:

tnamelogicscfifo0ofinstance"

inst"

--

hassamenameascurrentdesignfile

模块的名字和project的名字重名了

把两个名字之一改一下,一般改模块的名字

18.Warning:

Usingdesignfilelpm_fifo0.v,whichisnotspecifiedasa

designfileforthecurrentproject,butcontainsdefinitionsfor1design

unitsand1entitiesinprojectInfo:

Foundentity1:

lpm_fifo0

模块不是在本项目生成的,而是直接copy了别的项目的原理图和源程序

而生成的,而不是用QUARTUS将文件添加进本项目

无须理会,不影响使用

19.Timingcharacteristicsofdevice<

arepreliminary

目前版本的QuartusII只对该器件提供初步的时序特征分析

如果坚持用目前的器件,无须理会该警告。

关于进一步的时序特征分析会

在后续版本的Quartus得到完善。

20.TimingAnalysisdoesnotsupporttheanalysisoflatchesas

synchronouselementsforthecurrentlyselecteddevicefamily

用analyze_latches_as_synchronous_elementssetting可以让

QuarutsII来分析同步锁存,但目前的器件不支持这个特性

无须理会。

时序分析可能将锁存器分析成回路。

但并不一定分析正确。

其

后果可能会导致显示提醒用户:

改变设计来消除锁存器

21.Warning:

Foundxxoutputpinswithoutoutputpinloadcapacitance

assignment(网友:

gucheng82提供)

没有给输出管教指定负载电容

该功能用于估算TCO和功耗,可以不理会,也可以在AssignmentEditor

中为相应的输出管脚指定负载电容,以消除警告

22.Warning:

Found6node(s)inclockpathswhichmaybeactingas

clockskew

使用了行波时钟或门控时钟,把触发器的输出当时钟用就会报行波时钟,

将组合逻辑的输出当时钟用就会报门控时钟

不要把触发器的输出当时钟,不要将组合逻辑的输出当时钟,如果本身如

此设计,则无须理会该警告

23.Warning(10268):

VerilogHDLinformationatlcd7106.v(63):

AlwaysConstructcontainsbothblockingandnon-blocking

assignments

一个always模块中同时有阻塞和非阻塞的赋值

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Quartus 常见 错误 警告 分析

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx