西北工业大学数集实验4.docx

西北工业大学数集实验4.docx

- 文档编号:18093267

- 上传时间:2023-04-24

- 格式:DOCX

- 页数:14

- 大小:804.46KB

西北工业大学数集实验4.docx

《西北工业大学数集实验4.docx》由会员分享,可在线阅读,更多相关《西北工业大学数集实验4.docx(14页珍藏版)》请在冰豆网上搜索。

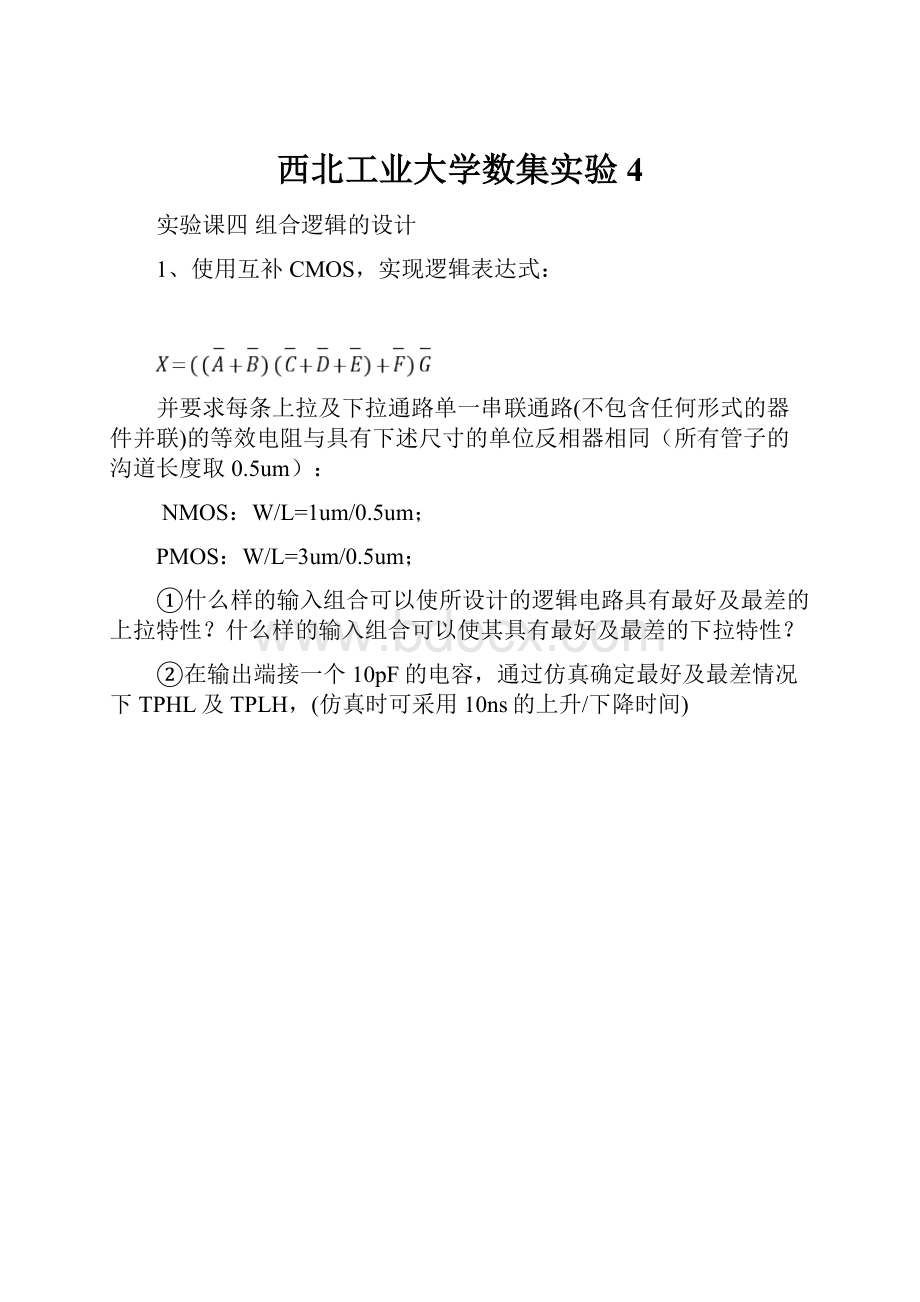

西北工业大学数集实验4

实验课四组合逻辑的设计

1、使用互补CMOS,实现逻辑表达式:

并要求每条上拉及下拉通路单一串联通路(不包含任何形式的器件并联)的等效电阻与具有下述尺寸的单位反相器相同(所有管子的沟道长度取0.5um):

NMOS:

W/L=1um/0.5um;

PMOS:

W/L=3um/0.5um;

①什么样的输入组合可以使所设计的逻辑电路具有最好及最差的上拉特性?

什么样的输入组合可以使其具有最好及最差的下拉特性?

②在输出端接一个10pF的电容,通过仿真确定最好及最差情况下TPHL及TPLH,(仿真时可采用10ns的上升/下降时间)

最好上拉特性A,B,C,D,E,F导通,内部节点电容被充电,只需G从1变0

最坏上拉特性需要对下拉网络内部节点电容充电即A,B,C,D:

1B,E,F,G从1变为0,此时上拉网络电阻最大

最好下拉特性下拉网络A,B,C,D,E导通,内部节点电容接地,G,F从0变为1,所得到的电容最小,电阻并联得到最小,这时延时最小。

最差下拉特性需要对上拉和下拉网络内部节点电容放电,并且下拉网络单一导通,下拉网络电阻最大得到输入组合:

C,D,E,G:

0A,B,F从0变为1

图4-1四种情况下输出波形(从上向下为最好、最坏上拉特性,最好、最坏下拉特性)

代码如下:

radix1111111

ioiiiiiii

vnameabcdefg

tunitus

trise0.01

tfall0.01

vih2.5

vil0.0

vol0.0

voh2.5

0.50000001

10000000

1.51111101

21011010

2.51111100

31111111

3.50000000

41100010

实验四最好及最差情况下TPLH及TPHL

.optionprobe

.unprotect

.lib'D:

\spics\cmos25_level49.lib'TT

.globalvdd

.vec'D:

\spics\experiment\vv.vec'

VDDvdd0DC=2.5v

C1out010p

M1vdda11PMOSW=12uL=0.5u

M2vddb11PMOSW=12uL=0.5u

M31c22PMOSW=12uL=0.5u

M41 d22PMOSW=12uL=0.5u

M51e22PMOSW=12uL=0.5u

M6vddf22PMOSW=6uL=0.5u

M72goutoutPMOSW=6uL=0.5u

M8outg00NMOSW=1uL=0.5u

M9outf33NMOSW=2uL=0.5u

M103a44NMOSW=4uL=0.5u

M114b00NMOSW=4uL=0.5u

M123c55NMOSW=6uL=0.5u

M135d66NMOSW=6uL=0.5u

M146e00NMOSW=6uL=0.5u

.op

.probev(out)

.tran10n5u

.meastrantplhgoodtrigv(g)val=1.25fall=1targv(out)val=1.25rise=1

.meastrantplhbadtrigv(b)val=1.25fall=1targv(out)val=1.25rise=2

.meastrantphlgoodtrigv(f)val=1.25rise=2targv(out)val=1.25fall=2

.meastrantphlbadtrigv(a)val=1.25rise=2targv(out)val=1.25fall=3

.end

2、考虑下面的逻辑电路:

解决下面的问题:

1写出这个CMOS逻辑门的逻辑表达式,标记出每一个晶体管的尺寸,使此逻辑门单一通路的上拉下拉通路的等效电阻与具有下列尺寸的反相器相同:

NMOS:

W/L=1um/0.25um;

PMOS:

W/L=2um/0.25um;

2考虑使

和

达到最大的输入方式(要考虑到内部节点电容的情况),写出产生这种最大延迟初始输入状态和最终输入状态。

在输出端连接1pF电容通过仿真比较这些最大延迟与最优延迟(输入从全0到全1变化,及全1到全0时变化的延迟)进行比较。

提示:

输入信号上升下降时间可以定义为1ns,通过measure命令测量延迟时间。

当

最大时,下拉网络单一导通,下拉电阻最大,且这时候需要对上拉内部节点电容放电;最小为C,D已导通只需A,B同时从0变为1。

最大

时,需要对下拉网络内部节点进行充电,且此时上拉网路单一导通,电阻最大。

最小情况为B为0,A,C,D同时由1变为0,上拉网络电阻最小。

1.

最大

代码如下:

实验4.2

.optionsprobe

.unprotect

.lib'D:

\spics\cmos25_level49.lib'TT

.globalvdd

VDDvdd0DC=1v

C1out01p

M1vddb11PMOSW=4uL=0.5u

M21aoutoutPMOSW=4uL=0.5u

M3vddcoutoutPMOSW=2uL=0.5u

M4vdddoutoutPMOSW=2uL=0.5u

M5outa22NMOSW=3uL=0.5u

M6outb22NMOSW=3uL=0.5u

M72c33NMOSW=3uL=0.5u

M83d00NMOSW=3uL=0.5u

Vaa0DC=0v

Vbb0PULSE(015ns1n1n1u2u)

Vcc0PULSE(015ns1n1n1u2u)

Vdd0PULSE(015ns1n1n1u2u)

.op

.probev(out)

.tran10n5u

.meastphltrigv(a)val=0.5rise=1targv(out)val=0.5fall=1

.end

最优值

2.最大

代码如下:

实验4.2.2

.optionsprobe

.unprotect

.lib'D:

\spics\cmos25_level49.lib'TT

.globalvdd

VDDvdd0DC=1v

C1out01p

M1vddb11PMOSW=4uL=0.5u

M21aoutoutPMOSW=4uL=0.5u

M3vddcoutoutPMOSW=2uL=0.5u

M4vdddoutoutPMOSW=2uL=0.5u

M5outa22NMOSW=3uL=0.5u

M6outb22NMOSW=3uL=0.5u

M72c33NMOSW=3uL=0.5u

M83d00NMOSW=3uL=0.5u

Vaa0dc=1

Vbb0dc=1

Vcc0dc=1

Vdd0PULSE(015ns1n1n1u2u)

.op

.probev(out)

.tran10n5u

.meastplhtrigv(d)val=0.5fall=1targv(out)val=0.5rise=1

.end

最优值

3如果P(A=1)=0.5,P(B=1)=0.2,P(C=1)=0.3,P(D=1)=1,计算此逻辑门消耗的功率。

设

(提示:

每次输出从0到1的反转意味着电源要提供功耗。

不计算通路电阻消耗的功耗)

3、下图是一个4级的多米诺逻辑电路,所有的预充管和求值管使用的是同一个时钟Φ。

假定所有的下拉网络都是由一个简单的NMOS来实现;每一个多米诺级都由一个动态反相器和静态反相器构成;预充时间,求值时间和静态反相器的延迟时间都为T/2;信号传播是理想的(上升和下降的时间为0)。

①IN信号和时钟Φ具有下图的关系,Φ的周期为10T,试画出Out1,Out2,Out3,Out4在10T内的波形。

2如果在后三级没有求值管的话,假定初始时时钟Φ使所有的多米诺级处于预充状态(Φ=0),然后该多米诺组合逻辑进入求值阶段(Φ=1),试问求值阶段会不会出现什么问题?

或者是不是有更好的延迟特性?

解释一下为什么?

求值阶段不会出现问题,这一操作可以使时钟负载减小并提高下拉驱动能力,延迟变小,因为下拉网络的电阻变小,所以延迟变小。

3试问在后三级的求值管被移除的情况下,假定时钟Φ初始时处于求值状态(Φ=1),然后该逻辑模块进入预充状态(Φ=0),会不会出现什么问题?

或者是不是有更好的延迟特性?

解释一下为什么?

逻辑模块可以达到最后的预充状态,但是延迟会变大。

假设IN从1变为0,第二个门输入最初为高电平,out1需要两个门延迟才会被驱动到低电平,而在此期间第二个门不能被预充电,因为它的下拉网络处于导通状态,第三个门必须等到第二门预充电后才能被预充电,这样延时会大大增加。

附录:

输入向量文件的书写

radix1111

ioiiii

vnameVin[3:

0]

tunitus

trise0.01

tfall0.01

vih2.5

vil0.0

vol0.25

voh2.25

00000

20001

40010

60011

80100

100101

120110

140111

161000

181001

201010

221011

241100

261101

281110

301111

将文本存为.vec文件.

在sp文件中的调用:

.vec'F:

\T3sim\TT.vec'

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 西北工业大学 实验

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

#全自动电容电感测试仪.docx

#全自动电容电感测试仪.docx