电子技术课程设计与CAD实习多功能数字钟Word文档下载推荐.docx

电子技术课程设计与CAD实习多功能数字钟Word文档下载推荐.docx

- 文档编号:17502218

- 上传时间:2022-12-06

- 格式:DOCX

- 页数:11

- 大小:378.63KB

电子技术课程设计与CAD实习多功能数字钟Word文档下载推荐.docx

《电子技术课程设计与CAD实习多功能数字钟Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《电子技术课程设计与CAD实习多功能数字钟Word文档下载推荐.docx(11页珍藏版)》请在冰豆网上搜索。

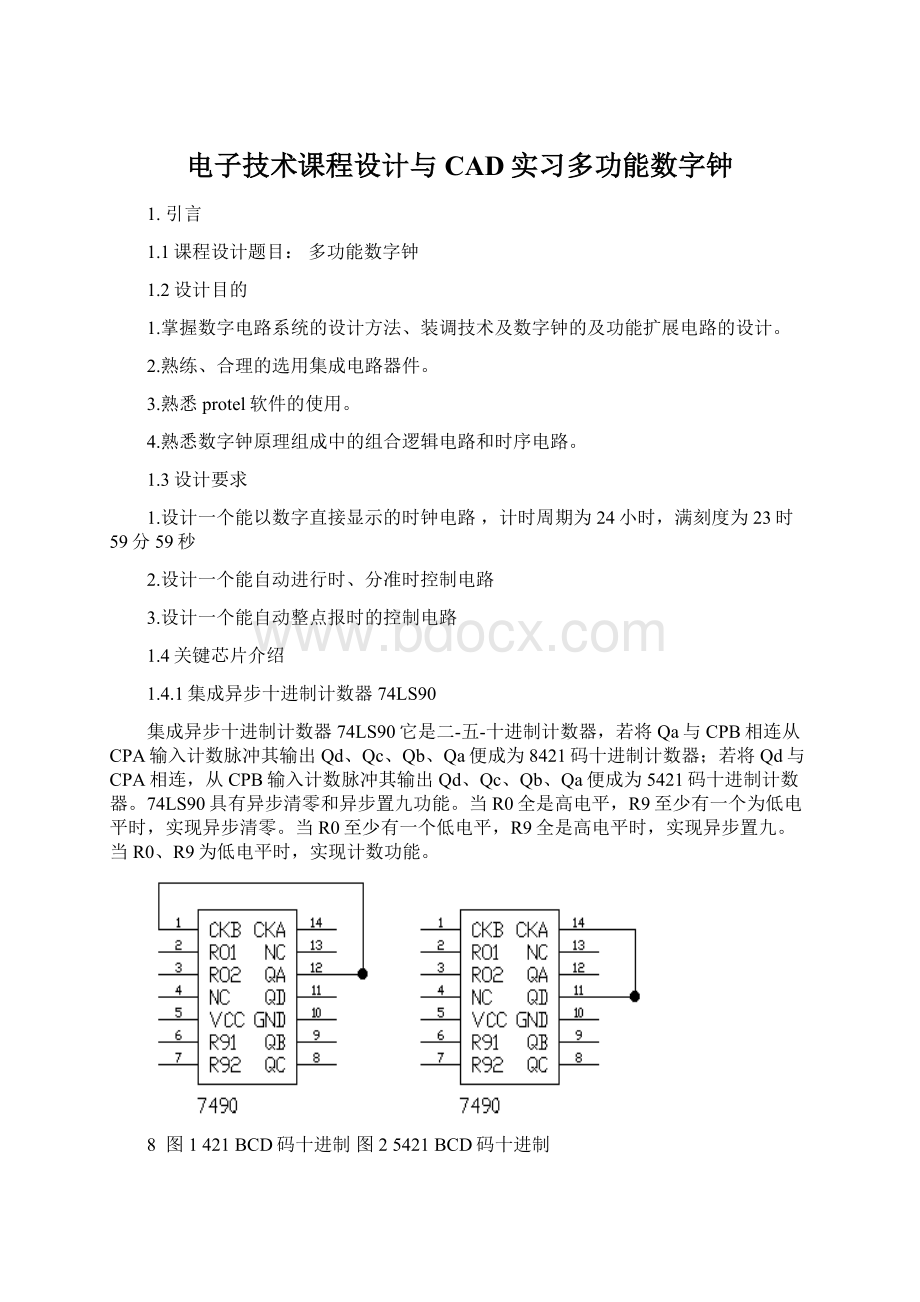

集成异步十进制计数器74LS90它是二-五-十进制计数器,若将Qa与CPB相连从CPA输入计数脉冲其输出Qd、Qc、Qb、Qa便成为8421码十进制计数器;

若将Qd与CPA相连,从CPB输入计数脉冲其输出Qd、Qc、Qb、Qa便成为5421码十进制计数器。

74LS90具有异步清零和异步置九功能。

当R0全是高电平,R9至少有一个为低电平时,实现异步清零。

当R0至少有一个低电平,R9全是高电平时,实现异步置九。

当R0、R9为低电平时,实现计数功能。

8图1421BCD码十进制图25421BCD码十进制

74LS90功能表如下:

输入

输出

R01R02R91R92

QdQcQbQA

HHL×

HH×

L

L×

HH

×

LHH

LLLL

HLLH

L×

LL×

×

计数

表1

1.4.2555定时器

图3

振荡器由555定时器构成。

在555定时器的外部接适当的电阻和电容元件构成多谐振荡器,再选择元件参数使其发出标准秒信号。

555定时器的功能主要由上、下两个比较器C1、C2的工作状况决定。

比较器的参考电压由分压器提供,在电源与地端之间加上VCC电压,且控制端VM悬空,则上比较器C1的反相端“-”加上的参考电压为2/3VCC,下比较器C2的同相端“+”加上的参考电压为1/3VCC。

若触发端S的输入电压V2≤1/3VCC,下比较器C2输出为“1”电平,SR触发器的S输入端接受“1”信号,可使触发器输出端Q为“1”,从而使整个555电路输出为“1”;

若阈值端R的输入电压V6≥2/3VCC,上比较器C1输出为“1”电平,SR触发器的R输入端接受“1”信号,可使触发器输出端Q为“0”,从而使整个555电路输出为“0”。

控制电压端VM外加电压可改变两个比较器的参考电压,不用时,通常将它通过电容(0.01μF左右)接地。

放电管T1的输出端Q′为集电极开路输出,其集电极最大电流可达50mA,因此,具有较大的带灌电流负载能力。

若复位端RD加低电平或接地,可使电路强制复位,不管555电路原处于什么状态,均可使它的输出Q为“0”电平。

只要在555定时器电路外部配上两个电阻及两个电容元件,并将某些引脚相连,就可方便地构成多谐振荡器。

2.课程设计的电路设计部分:

数字电子钟由信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路等组成。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用555构成的振荡器加分频器来实现。

将标准秒脉冲信号送入“秒计数器”,该计数器采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计数器,可以实现一天24h的累计。

译码显示电路将“时、分、秒”计数器的输出状态经七段显示译码器译码,通过六位LED显示器显示出来。

整点报时电路是根据计时系统的输出状态产生一个脉冲信号,然后去触发音频发生器实现报时。

校时电路是来对“时、分、秒”显示数字进行校对调整。

2.1设计框图

图4多功能数字钟原理框图

2.2功能模块

2.2.1译码显示电路

译码电路的功能是将秒、分、时计数器的输出代码进行翻译,变成相应的数字。

用与驱动LED七段数码管的译码器常用的有74LS48。

74LS48是BCD-7段译码器/驱动器,输出高电平有效,专用于驱动LED七段共阴极显示数码管。

若将秒、分、时计数器的每位输出分别送到相应七段译吗管的输入端,便可以进行不同数字的显示。

在译码管输出与数码管之间串联电阻R作为限流电阻。

图5译码电路

2.2.2秒脉冲信号发生器

秒脉冲信号发生器是数字电子钟的核心部分,它的精度和稳定度决定了数字钟的质量。

由振荡器与分频器组合产生秒脉冲信号。

●振荡器:

通常用555定时器与RC构成的多谐振荡器,经过调整输出1000Hz脉冲。

●分频器:

分频器功能主要有两个,一是产生标准秒脉冲信号,一是提供功能

扩展电路所需要的信号获得1Hz标准秒脉冲。

图6秒脉冲产生电路

2.2.3校时电路

校时电路是数字钟不可缺少的部分,每当数字钟与实际时间不符时,需要根据标准时间进行校时。

K1、K2分别是时校正、分校正开关。

不校正时,K1、K2开关是闭和的。

当校正时位时,需要把K1开关打开,然后用手拨动K3开关,来回拨动一次,就能使时位增加1,根据需要去拨动开关的次数,校正完毕后把K1开关闭上。

校正分位时和校正时位的方法一样。

其电路图如下:

图7时间校正电路

2.2.4计数电路

时间计数单元有时计数、分计数和秒计数等几个部分。

时计数单元一般为24进制计数器计数器,但是这里面的要求是12进制的。

其输出为两位8421BCD码形式;

分计数和秒计数单元为60进制计数器,其输出也为8421BCD码。

本实验采取了74LS90用两块芯片进行级联来产生60进制和24进制秒个位计数单元为10进制计数器,无需进制转换,只需将Q0与CP1(下降沿有效)相连即可。

CP0(下降没效)与1HZ秒输入信号相连,Q3可作为向上的进位信号与十位计数单元的CP1相连。

秒十位计数单元为6进制计数器,需要进制转换。

将10进制计数器转换为6进制计数器的电路连接,其中Q2可作为向上的进位信号与分个位的计数单元的CP0相连。

分个位和分十位计数单元电路结构分别与秒个位和秒十位计数单元完全相同,也是分个位计数单元的Q3作为向上的进位信号应与分十位计数单元的CP0相连,分十位计数单元的Q2作为向上的进位信号应与时个位计数单元的CP0相连。

60进制的连接如图4所示。

时个位计数单元电路结构仍与秒或个位计数单元相同,但是要求,整个时计数单元应为12进制计数器,所以在两块74LS90构成的100进制中截取12,就得在12的时候进行异步清零。

图8计数器

2.2.5整点报时电路

一般时钟电路应具备整点报时电路功能,即在时间出现整点前数秒内数字钟会自动报时,以示提醒。

其作用方式是发出连续的或有节奏的音频声波较复杂的可以是实时语音提示。

图9整点报时电路

2.3总电路图

图10多功能数字钟电路原理图

图11丝印层正反面

图12丝印层正面

图13丝印层反面

3.元器件使用说明

3.1元器件清单:

1位共阴数码管(6个)

74LS48(6个)

74LS90(6个)

74LS00(3片)

74LS04(1片)

74LS30(1片)

5V有源蜂鸣器一个

DPDT开关2个

NE555(1个)

44K电阻(1个)

50k电阻(1个)

0.01uF电容(2个

3.2元器件说明:

在清单中所列的元器件均为实验室中有的,与我所设计的电路图中所用元器件功能相同并且管脚相同,可以用74LS00替换7400、74LS04替换7404、74LS08替换7408、74LS21替换7421、74LS86替换7486、74LS90替换7490。

4.心得体会

以前看别人的一个电子表卖十几块钱,心里面有点愤愤不平,现在,自己做过一个电子钟,才发现,其中的不容易,还有艰辛。

其实做其他的事情也是一样,都会经过很多的困难,才能成功。

突然想起一句话“不经历风雨,怎么见彩虹”。

做了两周的课程设计,有很多的心得体会,有关于单片机的,也有关于模电数电CAD等基础科目的。

因为所涉及的知识已经很久没复习,刚拿到题目,不知道从哪入手,后来通过对书本的回顾,加深了对知识的记忆。

有些知识会迁移和联系模电数电。

课堂教学考虑到大多数同学的需求,主要强调“基本”——基本知识、基本理论、基本方法、基本技能。

而这次设计正是为我们提供了一个深入学习、探索的机会,成为课堂教学的有益补充。

我们正面临就业问题,这次课设给了我们一个机会去试验。

各种理论的学习是为课程的设计作准备的,但有时学习的理论也解决不了实践中的问题。

实践中获得的知识能让我对知识有更好的认识和理解。

虽然这次的课程设计我参考了一些文献资料,没有做到创新,但在对程序的读写过程中我明白了许多。

这次课程设计的最大收获是只有把理论用到实践中我们才能真正掌握好所学知识。

5.参考文献

数字电子技术作者:

宋卫海,杨现德出版社:

北京大学出版社出版时间:

2010...

模拟电子技术基础作者:

王卫东出版社:

电子工业出版社出版时间:

2010年5月1日

电子线路设计指导作者:

高平主编出版社:

化学工业出版社出版日期2010

数字电路实验与课程设计(吕思忠)著译者:

出版日期:

2003-09-01

电子技术实验指导书著译者:

王鲁杨主编出版日期:

2011-04-01

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 电子技术 课程设计 CAD 实习 多功能 数字

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx