注电考试最新版教材第33讲 第十九章基本逻辑电路一.docx

注电考试最新版教材第33讲 第十九章基本逻辑电路一.docx

- 文档编号:1745724

- 上传时间:2022-10-23

- 格式:DOCX

- 页数:10

- 大小:344.08KB

注电考试最新版教材第33讲 第十九章基本逻辑电路一.docx

《注电考试最新版教材第33讲 第十九章基本逻辑电路一.docx》由会员分享,可在线阅读,更多相关《注电考试最新版教材第33讲 第十九章基本逻辑电路一.docx(10页珍藏版)》请在冰豆网上搜索。

注电考试最新版教材第33讲第十九章基本逻辑电路一

第19章基本逻辑电路

大纲要求:

掌握组合逻辑电路输入输出的特点

了解组合逻辑电路的分析、设计方法及步骤

掌握编码器、译码器、显示器、多路选择器及多路分配器的原理和应用

掌握加法器、数码比较器、存储器、可编程逻辑阵列的原理和应用

一、编码器

(1)编码器的含义

一般地说,用文字、符号或者数码表示特定信息的过程称为编码,能够实现编码功能的电路称为编码器。

在数字系统中,是采用若干个二进制码0和1来进行编码的,要表示的信息越多,二进制代码的位数越多。

N位二进制代码有2n个状态,可以表示2n个信息,对N个信号进行编码时,应按公式2n>=N来确定需要使用的二进制代码的位数n。

常用的编码器有二进制编码器、二—十进制编码器、优先编码器等。

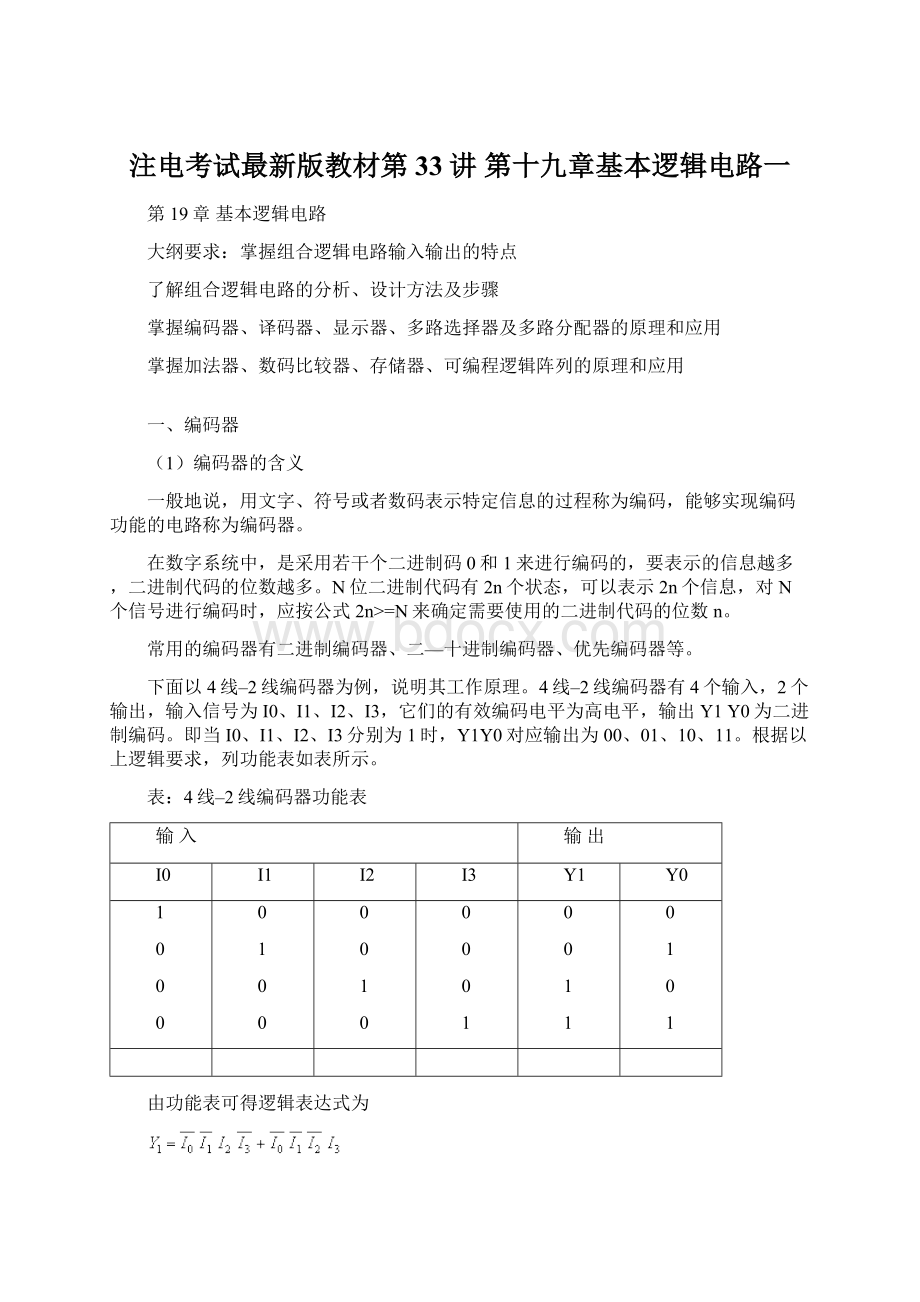

下面以4线–2线编码器为例,说明其工作原理。

4线–2线编码器有4个输入,2个输出,输入信号为I0、I1、I2、I3,它们的有效编码电平为高电平,输出Y1Y0为二进制编码。

即当I0、I1、I2、I3分别为1时,Y1Y0对应输出为00、01、10、11。

根据以上逻辑要求,列功能表如表所示。

表:

4线–2线编码器功能表

输入

输出

I0

I1

I2

I3

Y1

Y0

1

0

0

0

0

1

0

0

0

0

1

0

0

0

0

1

0

0

1

1

0

1

0

1

由功能表可得逻辑表达式为

根据上式可画出4线–2线编码器的逻辑图。

19.1.2二进制编码器

二进制编码器是由n位二进制数表示2n个信号的编码电路

19.1.3二-十进制编码器

概念:

二–十进制编码器:

实现用4位二进制数代码对1位十进制数码进行编码的电路。

亦即将0~9十个十进制数转换为二进制代码的电路。

简称BCD编码器。

举例:

8421BCD码编码器

输入10个互斥的数码,输出4位二进制代码

真值表:

真值表

输入

I

输出

Y3Y2Y1Y0

0(I0)

1(I1)

2(I2)

3(I3)

4(I4)

5(I5)

6(I6)

7(I7)

8(I8)

9(I9)

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

逻辑图:

19.1.4优先编码器

优先编码器:

在多个信息同时输入时,只对输入中优先级别最高的信号进行编码。

在优先编码器中优先级别高的信号排斥级别低的,即具有单方面排斥的特性。

优先级别:

编码者规定。

举例:

10线——4线优先编码器(8421BCD码优先编码器)

真值表(设优先级别从I9至I0递降):

集成10线-4线优先编码器输入端和输出端都是低电平有效,其逻辑符号如下:

表中的输入和输出都是原码,“0”表示无输入,“1”表示有输入,“╳”表示无关输入

19.2译码器

19.2.1基本译码器

译码是编码的反过程,是将给定的二进制代码翻译成编码时赋予的原意,完成这种功能的电路称为译码器。

译码器是多输入、多输入出的组合逻辑电路。

2线–4线译码器

设A0、A1为译码电路的输入变量,输出信号分别为~,它们的有效电平为低电平。

当输入代码分别为00、01、10、11时,分别输出低电平。

另外,设置一个使能输入端,且当=0时,允许译码器工作,否则译码器被禁止。

于是,可列出译码器的功能表如表所示。

表:

2线–4线译码器功能表

由功能表可写出各输出端的逻辑表达式为

19.2.2二进制译码器

二进制译码器将输入的个二进制代码翻译成个信号输出,又称为变量译码器。

3位二进制译码器代码输入的是3位二进制代码A2A1A0,输出是8个译码信号Y0~Y7,真值表如表所示,逻辑表达式为:

表3位二进制译码器的真值表

逻辑图如图所示。

集成二进制译码器和门电路配合可实现逻辑函数,其方法是:

首先将函数值为1时输入变量的各种取值组合表示成与或表达式,其中每个与项必须包含函数的全部变量,每个变量都以原变量或反变量的形式出现且仅出现一次,由于集成二进制译码器大多输出为低电平有效,所以还需将与或表达式转换为与非表达式,最后按照与非表达式在二进制译码器后面接上相应的与非门即可。

图3位二进制译码器

19.2.3二-十进制译码器

把二-十进制代码翻译成10个十进制数字信号的电路称为二-十进制译码器,其输入是十进制数的4位二进制编码A3~A0,输出的是与10个十进制数字相对应的10个信号Y9~Y0。

8421码译码器的真值表如表所示,逻辑表达式分别为:

表8421码译码器的真值表

逻辑图如图所示。

图8421码译码器的逻辑图

(2)显示译码器

7段LED数码显示器是将要显示的十进制数码分成7段,每段为一个发光二极管,利用不同发光段的组合来显示不同的数字,有共阴极和共阳极两种接法,如图所示。

发光二极管a~g用于显示十进制的10个数字0~9,h用于显示小数点。

对于共阴极的显示器,某一段接高电平时发光;对于共阳极的显示器,某一段接低电平时发光。

使用时每个二极管要串联一个约100Ω的限流电阻。

驱动共阴极的7段发光二极管的二-十进制译码器,设4个输入A3~A0采用8421码,真值表如表所示。

19.3二进制加法器

一、半加器

概念:

能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器。

或:

只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器。

1、半加器真值表

2、输出逻辑函数

3、逻辑图和逻辑符号

二、全加器

概念:

能对两个1位二进制数进行相加并考虑低位来的进位,即相当于3个1位二进制数相加,求得和及进位的逻辑电路称为全加器。

或:

不仅考虑两个一位二进制数相加,而且还考虑来自低位进位数相加的运算电路,称为全加器。

1、真值表

Ai、Bi:

加数,Ci-1:

低位来的进位,Si:

本位的和,Ci:

向高位的进位。

2、输出逻辑函数

3、全加器的逻辑图和逻辑符号

表达式:

4、用与或非门实现

19.3.4数据选择器和数据分配器

数据选择器

概念:

从多路输入信号中选择其中一路进行输出的电路称为数据选择器。

或:

在地址信号控制下,从多路输入信息中选择其中的某一路信息作为输出的电路称为数据选择器

数据选择器又叫多路选择器,简称MUX。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 注电考试最新版教材第33讲 第十九章基本逻辑电路一 考试 最新版 教材 33 第十九 基本 逻辑电路

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《巴黎圣母院》3000字读书心得范文.docx

《巴黎圣母院》3000字读书心得范文.docx