十六进制七段数码显示管设计文档格式.docx

十六进制七段数码显示管设计文档格式.docx

- 文档编号:17455792

- 上传时间:2022-12-01

- 格式:DOCX

- 页数:11

- 大小:9.27MB

十六进制七段数码显示管设计文档格式.docx

《十六进制七段数码显示管设计文档格式.docx》由会员分享,可在线阅读,更多相关《十六进制七段数码显示管设计文档格式.docx(11页珍藏版)》请在冰豆网上搜索。

)七段数码显示管设计

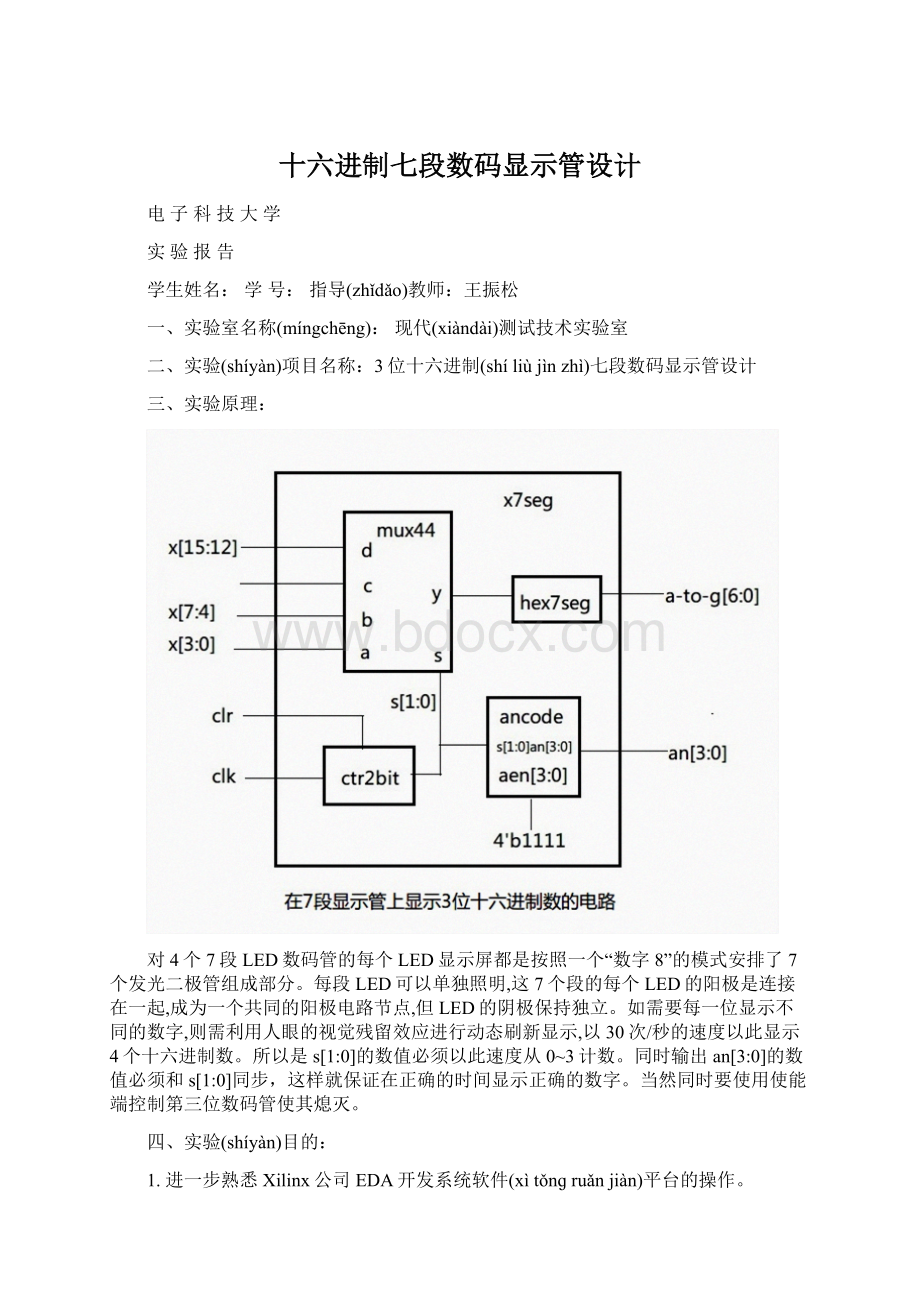

三、实验原理:

对4个7段LED数码管的每个LED显示屏都是按照一个“数字8”的模式安排了7个发光二极管组成部分。

每段LED可以单独照明,这7个段的每个LED的阳极是连接在一起,成为一个共同的阳极电路节点,但LED的阴极保持独立。

如需要每一位显示不同的数字,则需利用人眼的视觉残留效应进行动态刷新显示,以30次/秒的速度以此显示4个十六进制数。

所以是s[1:

0]的数值必须以此速度从0~3计数。

同时输出an[3:

0]的数值必须和s[1:

0]同步,这样就保证在正确的时间显示正确的数字。

当然同时要使用使能端控制第三位数码管使其熄灭。

四、实验(shí

n)目的:

1.进一步熟悉Xilinx公司EDA开发系统软件(xì

tǒnɡruǎnjià

n)平台的操作。

2.学会(xué

huì

)将50M的晶振经多次分频后得到(dé

dà

o)低频脉冲信号。

3.学会(xué

)用VerilogHDL中的case语句来创建七段译码器。

4.学会使用原理图作为顶层图实现数字电路。

5.掌握数码管动态扫描显示技术。

6.学会用BASYS2FPGA开发板下载执行并验证代码。

五、实验内容:

1)利用HDL代码输入方式在XilinxISE13.4平台上实现一个十六进制七段数码显示管设计;

2)使用原理图作为顶层图实现数字电路,使用模块实例语句连接前面所设计的七段译码器模块;

3)生成比特流文件下载到开发板上进行验证。

六、实验(shí

n)器材(设备、元器件):

1)计算机(安装(ānzhuāng)XilinxISE13.4软件平台);

2)BASYS2FPGA开发板一套(带USB-MiniUSB下载(xià

zǎi)线)。

七、实验(shí

n)步骤:

1、在XilinxISE13.4平台中,新建一个(yīɡè

)工程LED。

我们选用的BASYS2FPGA开发板采用的是Spartan3EXC3S100E芯片和CP132封装,设置好器件属性。

2、在工程管理区任意(rè

nyì

)位置单击鼠标右键,在弹出的快捷菜单中选择“NewSource”命令,弹出新建源代码对话框,这里我们(wǒmen)选择“VerilogModule”类型(lè

ixí

ng),输入Verilog文件名。

ISE会自动创建一个Verilog的模板,并在源代码编辑区打开,接下来的工作就是将代码编写(biānxiě)完整。

完整(wá

nzhěng)代码如下:

moduleLED(

inputi0,inputi1,inputi2,inputi3,

outputreg[7:

0]o

);

wire[3:

0]i;

assigni[0]=i0;

assigni[1]=i1;

assigni[2]=i2;

assigni[3]=i3;

//七段数码管

always@(*)

case(i)//控制(kò

ngzhì

)表达式

0:

o=8'

b00000011;

//分支(fēnzhī)表达式

1:

b10011111;

2:

b00100101;

3:

b00001101;

4:

b10011001;

5:

b01001001;

6:

b01000001;

7:

b00011111;

8:

b00000001;

9:

b00001001;

'

hA:

b00010001;

hB:

b11000001;

hC:

b01100011;

hD:

b10000101;

hE:

b01100001;

hF:

b01110001;

default:

endcase

endmodule

保存后,在ISE左侧菜单的DesignUtilities里点击CreatSchematicSymbol生成电路模块,这样,我们(wǒmen)自己设计的一块译码器电路就完成了,如果编译有错误,反复修改直至成功。

3、接下来设计一个(yīɡè

)顶层电路,实现我们需要的功能。

在项目(xià

ngmù

)中添加“NewSource”,选择(xuǎnzé

)“Schematic”类型,则进入(jì

nrù

)原理图设计阶段。

软件在左侧(zuǒcè

)的Symbols栏中提供大量的芯片库供使用。

接下来再连上7段码译码器就可以驱动数码管显示了,在symbols里面(lǐmià

n)选择当前的工作目录就可以看到我们设计的译码器led7segment,加入(jiārù

)电路,再增加若干个输入(shūrù

)、输出端口,这个电路就设计好了。

接下来要将电路图与实际(shí

jì

)开发板引脚绑定,需要加入引脚定义文件,Newsource->

ImplementationConstraintsFile,加入后缀为ucf的引脚定义文件,或在项目中双击I/Opinplanning)PlanAhead)-Pre-Synthesis进入向导。

最终生成的ucf引脚定义(dì

ngyì

)文件如下:

其中,NET"

CLK"

LOC="

B8"

;

的含义为将项目中的CLK线绑定在开发板的“B8”脚,具体(jù

tǐ)引脚可见开发板上的字。

接下来生成电路(dià

nlù

)文件,点击GenerateProgrammingFile,经过漫长的等待,将会出现绿色钩,表示成功了。

4、选择sch项目下的design一栏,点击ConfigureTargetDevice,展开二级菜单(cà

idān),双击ManageConfigureProcesses,打开ISEImpact,双击BoundaryScan。

在右侧(yò

ucè

)空白处右击,选择InitializeChains,选择“是”,打开对应(duì

yì

ng)的bit文件

最后(zuì

hò

u)右击器件,选择Program将程序下载到开发板上并检查结果。

八、实验数据(shù

jù

)及结果分析:

实验仿真结果证明了设计的正确性,该设计是合理的,能够(né

nggò

u)满足实验所需的。

设计的数码显示管可以完美显示十六进制数,并且(bì

ngqiě)通过一些简单的改动还可以改变亮、灭灯的个数,同时也可以改变逻辑开关输入的高低(gāodī)位,出色地完成了实验要求的同时还具有一定的扩展性。

九、实验结论:

3位十六进制七段数码显示管由数选、位选、分频器和七段译码器组成,通过四位二进制输入来显示十六进制的数。

十、总结(zǒngjié

)及心得体会:

报告(bà

ogà

o)评分:

指导(zhǐdǎo)教师签字:

内容总结

(1)电子科技大学

指导教师:

一、实验室名称:

现代测试技术实验室

二、实验项目名称:

3位十六进制七段数码显示管设计

对4个7段LED数码管的每个LED显示屏都是按照一个“数字8”的模式安排了7个发光二极管组成部分

(2)所以是s[1:

0]的数值必须以此速度从0~3计数

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 十六进制 数码 显示 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx