EDA实验报告DOCWord文档下载推荐.docx

EDA实验报告DOCWord文档下载推荐.docx

- 文档编号:17438942

- 上传时间:2022-12-01

- 格式:DOCX

- 页数:17

- 大小:287.28KB

EDA实验报告DOCWord文档下载推荐.docx

《EDA实验报告DOCWord文档下载推荐.docx》由会员分享,可在线阅读,更多相关《EDA实验报告DOCWord文档下载推荐.docx(17页珍藏版)》请在冰豆网上搜索。

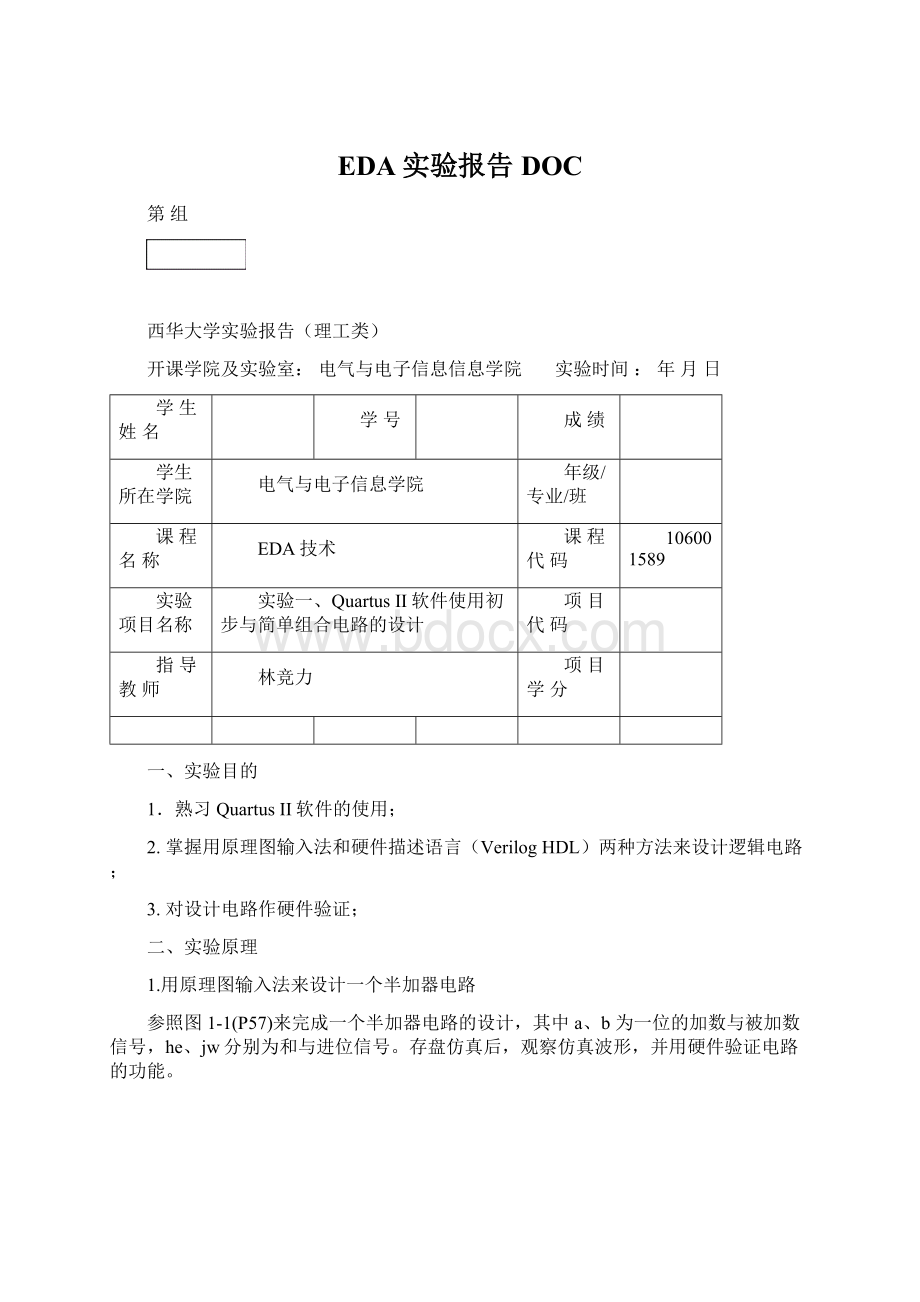

指导教师

林竞力

项目学分

一、实验目的

1.熟习QuartusII软件的使用;

2.掌握用原理图输入法和硬件描述语言(VerilogHDL)两种方法来设计逻辑电路;

3.对设计电路作硬件验证;

二、实验原理

1.用原理图输入法来设计一个半加器电路

参照图1-1(P57)来完成一个半加器电路的设计,其中a、b为一位的加数与被加数信号,he、jw分别为和与进位信号。

存盘仿真后,观察仿真波形,并用硬件验证电路的功能。

图1-1半加器电路原理图

2.QuartusII软件目前版本已达到10.0以上,但对于初学者来说采用6.0或7.1版本最为适合。

6.0与7.1版本相比更稳定,因此本实验采用QuartusII6.0,而7.1版本界面与6.0非常相似,学会6.0版本的使用也就学会了7.1版本的使用。

3.QuartusII软件设计电路流程:

(1)新建一个工程:

每设计一个电路就必须新建一个工程!

所有的设计文件都装在工程目录中,并由软件管理。

(2)设计输入:

告诉软件你要设计的电路是什么。

A.原理图设计方法-----用原理图编辑器画出电路图。

B.本文输入-----用文本编辑器采用硬件语言描述电路(电路主流设计方式)。

(3)编译

将设计电路的功能与PLD芯片结合,并提取出仿真所需的时序参数。

(4)仿真

软件验证电路功能是否实现。

(5)编程、配置与硬件测试

用下载电缆完成器件的编程与配置,做硬件测试。

原理图输入法设计半加器电路与描述语言设计3-8译码器区别在于流程的第二步设计输入。

三、实验设备、仪器及材料

电脑、EDA软件(QuartusII)、实验箱、下载电缆、连接导线。

四、实验步骤(按照实际操作过程)

(一)用原理图输入法完成半加器的设计步骤:

1.新建一个工程:

(必须完成这一步骤)

(1)进入Windows操作系统,双击QuartusII图标,启动软件。

(2)单击File\NewProjectWizard菜单,出现对话框点击next。

在界面中相应位置中输入文件名路径与设计工程的名字,最后点击finish,完成设计工程建立。

(3)在点击Assignment\Device菜单,出现如下对话框,点击选择器件(本设计选用EPF10K10)。

2.在原理图设计输入

(1)点击菜单File\New,选择BlockDiagram/SchematicFile,点OK,启动原理图编辑器。

(2)画出半加器原理图

a.在原理图空白处双击,会出现元件选择对话框,在name处输入元件名,点OK完成元件放置。

依次放置1个两输入端与门(and2)、1个异或门(xor)2个输入端口(input)、1个输出端口(output)在原理图上;

b.添加连线到器件的管脚上把鼠标移到元件引脚附近,则鼠标光标自动由箭头变为十字,按住鼠标右键拖动,即可画出连线,参照图1-1连好相应元件的输入、输出脚。

c.更改信号名

双点输入、输出管脚,在对话框中改信号名

d.保存原理图

单击保存按钮,以默认名保存。

3.编译

(1)点击菜单栏上红色箭头所指的工具图标,完成编译。

(2)锁定管脚再编译

点击Assignment\Pins菜单。

从图中可以看到信号a,b,he,jw,这些信号在硬件测试之前,必须与管脚锁定。

以锁定a信号管脚为例,双击a信号对应Location一栏,出现IO管脚选择列,选择PIN_16。

信号a就被锁在了芯片第16管脚上了。

按一样的方法将b,he,jw锁在空闲的IO口上。

信号锁定到管脚要生效,必须再按

(1)步骤重新编译一次。

4.仿真

(1)编译没有错误后进行仿真。

点击File\New菜单。

选择otherfiles中的vectorwaveformfile。

画出输入波形,执行仿真命令,启动仿真并观察仿真波形,进行设计电路的功能验证。

(2)双击空白处,弹出对话框,单击NodeFinder。

(3)按图依次操作选择信号

(4)按图操作画出信号输入波形

5.硬件测试

在教师指导下接好下载电缆,连好拔码开关与LED灯,验证电路功能。

(二)用VerilogHDL语言完成3-8译码器的设计步骤(除文本输入外,其余步骤与上一个实验一致):

(1)、运行QuartusII软件,先建立一个新的项目。

(2)、启动File\New菜单命令(如图1-21);

(3)、选择veriloghdlfile,点击OK后,键入上面“二、实验内容

(2)”中的程序。

(4)、以默认文件名和路径保存。

(5)、参照原理图输入设计进行仿真,并观察仿真波形,以验证所设计电路的功能。

五、实验过程记录(数据、图表、计算等)

学生手写

六、实验结果分析及问题讨论

学生手写(谈谈使用原理图输入法和VerilogHDL语言设计两种方法的优劣心得。

2.谈谈PLD与专用芯片ASIC的最大区别。

)

实验二、8位移位寄存器的设计

3.通过电路的仿真和硬件验证,进一步了解8位移位寄存器功能。

移位寄存器主要是将串行输入的数据依次移入到寄存中,可用于串行预置初值、串并转换等场合。

它主要在时钟作用下依次左移(或右移),通过非阻塞性过程赋值及for循环语句来实现。

难点在于理解移位寄存器的工作原理后,用VerilogHDL语言的for循环语句、非阻塞性过程赋值来设计该移位寄存器。

其难点是要仿真出移位寄存器的工作波形,然后通过观测仿真波形,来验证该移位寄存器的功能,并理解阻塞性过程赋值与非阻塞性过程赋值的区别。

用VerilogHDL语言设计移位寄存器的步骤:

(1)、运行QUARTUSII软件

(2)、启动File\New菜单命令(如图4-1);

(3)、选择veriloghdlfile,点击OK后,键入上面“二、实验内容”中的程序;

(4)、在目录中存成shiter8.V文件,然后进行编译。

(5)、仿真设计文件

启动QuartusII\File\New菜单,选择otherfiles中的vectorwaveformfile。

以默认文件名存盘,执行仿真命令,启动仿真并观察仿真波形,并对设计电路的进行功能验证。

学生手写(试设计一下8位右移移位寄存器,并比较8位左移和右移移位寄存器不同点)

实验三、十进制加法计数器的设计

2.掌握用VerilogHDL硬件描述语言来设计基于混合电路的十进制加法计数器;

3.通过电路的仿真和硬件验证,进一步了解加法计数器的功能,并深入理解VerilogHDL语言中组合逻辑电路和时序逻辑电路的设计。

实验设计的加法计数器的计数范围为20―100,当clk计数脉冲输入端有上升沿时,计数值count_reg加1,再将count_reg加上20后输出到计数输出端count。

本实验技术重点在于理解用组合逻辑电路和时序逻辑电路共同设计20―100加法计数器,并用VerilogHDL硬件描述语言来设计该加法计数器;

并熟练掌握持续赋值语句(assign)和过程赋值语句(always)的使用。

其难点是在于合理使用持续赋值语句和if语句使计数器计数初值为20,并且计数终值为100,然后通过观测仿真波形,来验证该加法计数器的功能。

用VerilogHDL语言设计20―100加法计数器的步骤:

(2)、启动File\New菜单命令,

(3)、选择veriloghdlfile,点击OK后,键入参考源程序程序;

(4)、存成couter.V文件,然后进行编译。

启动QuartusII\File\New菜单,选择otherfiles中的vectorwaveformfile。

在波形图中,设置计数脉冲输入clk时钟波形,并将波形文件以默认文件名存盘。

执行仿真命令,启动仿真并观察仿真波形,并对设计电路的进行功能验证。

学生手写(1.如要将设计的加法计数器改为减法计数器,该如何修改设计?

2.如要在所设计的加法计数器基础上增加一个进位位输出,又该如何修改设计?

实验四、基于LPM函数的加法电路设计

2.熟习使用LPM函数设计复杂的时序电路方法;

3.掌握锁定管脚、下载方法;

在电路中调用LPM函数(又叫强函数),即参数化的电路功能模块。

QUARTUSII软件支持的LPM函数种类较多,这里主要使用有加减法功能的LPM_ADD_SUB函数(其原理框如图所示。

必须要设置好该LPM函数诸如加、减法控制器、其中一个加数是否为常数、数据宽度等参数,让其实现相应的功能。

设置方法正如前述试验方法一和方法二所述。

图4.1

用VerilogHDL语言设计四位加法器的步骤:

(4)、在目录中存成test_add.V文件,点击菜单assignment\device,EPF10KLC84-3器件(family中的Flex10k),选择然后进行编译。

启动QuartusII\File\New菜单,选择otherfiles中的vectorwaveformfile。

(6)、锁定管脚、编程下载。

1)锁定管脚方法:

点击工具栏图标如图所示:

出现管脚锁定界面。

图4.2

管脚编辑过程如下:

双击出现下拉菜单,再选择器件管脚。

图4.3

管脚锁定以后,重新编译一次。

注意:

芯片上有一些特定功能管脚,进行管脚编辑时一定要注意。

另外,在芯片选择中,如果选Auto,则不允许对管脚进行再分配。

2)、器件下载:

出现编程界面,点击hardwaresetup。

图4.4

选择正确的编程电缆线。

再点上图的Start完成编程下载。

如果不能正确下载,可点击AutoDetect按钮进行测试,查找原因,最后按OK退出。

学生手写(1、在仿真时rlt信号会出现毛刺,应如何消除该信号中的毛刺?

2、如要将该电路改为一个减法器,又该如何设计?

3、方法一与方法二的相互关系怎样?

实验五、深度为4的8位RAM设计

2.掌握用硬件描述语言(VerilogHDL)来设计RAM电路;

3.通过电路的仿真和硬件验证,进一步了解RAM的功能及特点;

4X8位RAM的原理框图如图5-1所示,两位地址ad[2:

0]组成4位深度,read、we分别

控制RAM的读、写,用if语句描述来区分是否读或写,而case语句则用描述RAM对某一个地址数据的操作。

图5.1RAM的原理框图

本实验技术重点在于理解4X8位RAM的功能后,用VerilogHDL硬件描述语言来设计该电路;

并掌握if及case语句的使用方法及技巧。

其难点是要仿真出4X8位RAM的工作波形,然后通过观测仿真波形,来验证RAM设计是否能完成相应的功能。

(4)、在目录中存成RAM.V文件,然后进行编译。

学生手写(1.时序电路的特点?

2.时序电路与组合电路的区别是什么?

实验六、“101”序列检测器的设计

2.掌握用VerilogHDL硬件描述语言来设计“101”序列检测器;

3.通过电路的仿真,熟悉“101”序列检测器的工作原理。

在状态机设计中主要包括三个对象:

1、当前状态,或称为现态(currentstate,CS);

2、下一个状态,或称为次态(nextstate,NS);

3、输出逻辑(outlogic,OL)。

相应的,在用verilog描述有限状态机时,有下面几种描述方式:

1、三过程描述;

2、双过程描述;

3、单过程描述。

本设计采用三过程描述,下面给出“101”序列检测器的状态转换图,共有4个状态:

S0,S1,S2,S3,分别用几种方式对其描述。

图6.1“101”序列检测器的状态转换图

1、进入Windows操作系统,双击QuartusII图标,启动软件。

2、单击File\NewProjectWizard菜单,输入文件名路径与设计项目的名字fsm1_seq101,点击finish,完成设计项目建立。

3、点击Assignment\Device菜单,选择器件(本设计选用EPF10K10)。

4、启动File\New菜单命令,新建verilogHDLfile文件,并保存。

5、在fsm1_seq101.v文件中写出代码并保存、编译

6.2保存文件、编写代码

6、编译成功没有问题后,选择菜单中tools-netlistviewers,在出现的菜单中选择statemachineviewer,产生状态图。

图6.3产生的状态图

7、新建波形文件并保存,根据状态图、理解代码,用波形仿真“101”序列检测器的工作过程。

根据对状态图、程序的理解给出input波形,并仿真。

学生手写(1、用两个过程描述“101”序列检测器怎样编写程序;

2、用单过程描述“101”序列检测器怎样编写程序。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 实验 报告 DOC

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

z4签订与履行商务谈判的合同.ppt

z4签订与履行商务谈判的合同.ppt