最新一位全加器HSPICE设计文档格式.docx

最新一位全加器HSPICE设计文档格式.docx

- 文档编号:17335591

- 上传时间:2022-12-01

- 格式:DOCX

- 页数:12

- 大小:421.71KB

最新一位全加器HSPICE设计文档格式.docx

《最新一位全加器HSPICE设计文档格式.docx》由会员分享,可在线阅读,更多相关《最新一位全加器HSPICE设计文档格式.docx(12页珍藏版)》请在冰豆网上搜索。

与非门是与门和非门的结合,先进行与运算,再进行非运算。

与运算输入要求有两个,如果输入都用0和1表示的话,那么与运算的结果就是这两个数的乘积。

如1和1(两端都有信号),则输出为1;

1和0,则输出为0;

0和0,则输出为0

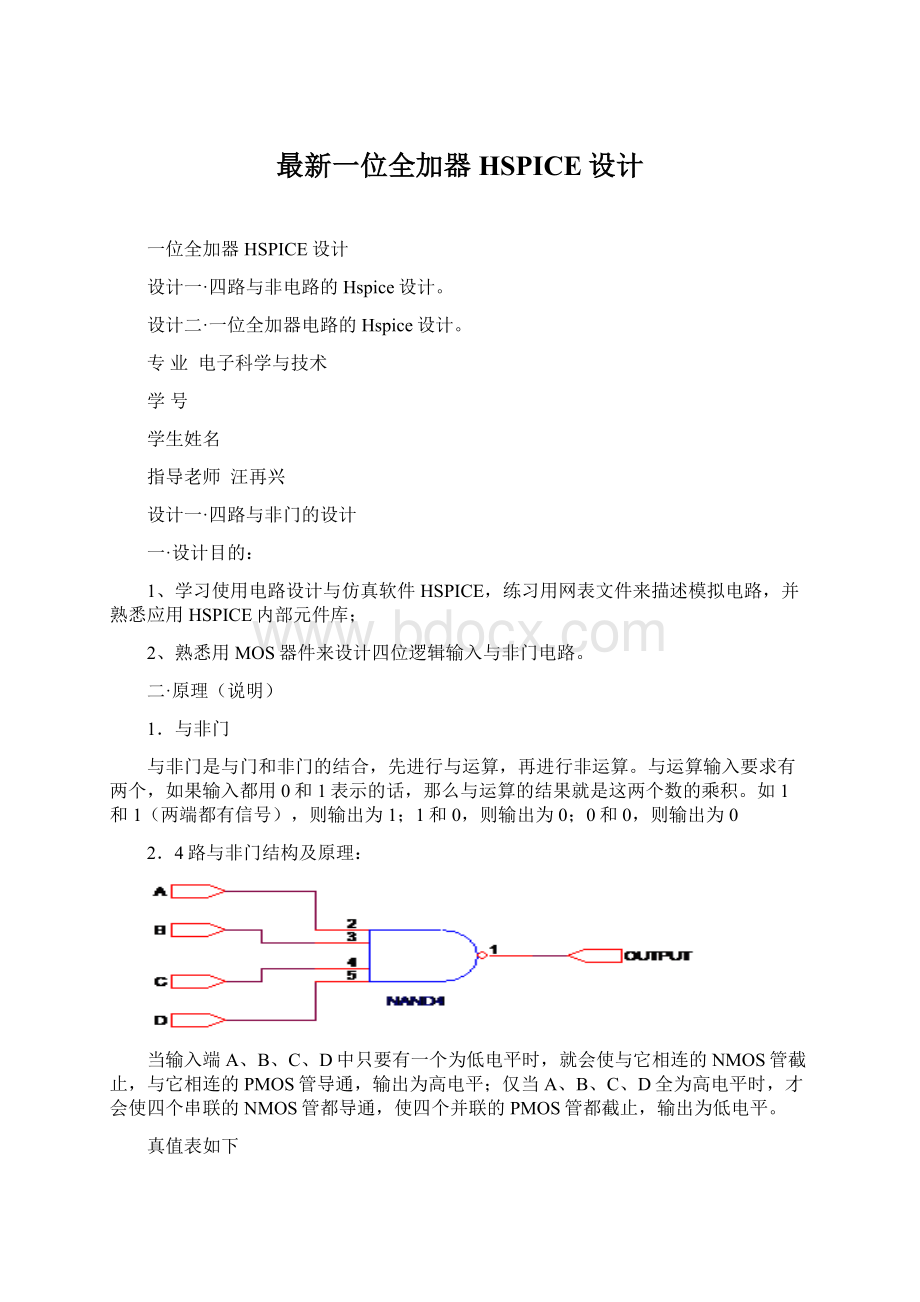

2.4路与非门结构及原理:

当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;

仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。

真值表如下

A

B

C

D

Y

1

4路与非门mos管的电路图:

三·

设计过程:

Hspice要进行仿真的时候,应事先编写好网表文件,再通过导入网表文件进行仿真。

输入的网表文件(.sp)包含以下内容:

(1)电路网表(子电路和宏,电源等)

(2)声明所要使用的库

(3)说明要进行的分析

(4)说明所要求的输出

输入的网表文件和库文件可以由原理图的网表生成器或者文本编写产生。

输入的网表文件中的第一行必须是标题行,并且.ALTER辅助模型只能出现在文件最后的.end语句之前,除此之外,其他语句可任意排列。

通过文本编写好的网表文件如下

4NANDCMOS

.OPTIONSLISTNODEPOST

.OP

.TRAN200P60N

M1OUT4VCCVCCPCHL=1UW=20U

M2OUT5VCCVCCPCHL=1UW=20U

M3OUT6VCCVCCPCHL=1UW=20U

M4OUT7VCCVCCPCHL=1UW=20U

M51400NCHL=1UW=20U

M62511NCHL=1UW=20U

M73622NCHL=1UW=20U

M8OUT733NCHL=1UW=20U

VCCVCC05

V140PULSE.24.82N1N1N5N10N

V250PULSE.24.82N1N1N5N20N

V360PULSE.24.82N1N1N5N10N

V470PULSE.24.82N1N1N5N20N

COUT0.01p

.MODELPCHPMOSLEVEL=1

.MODELNCHNMOSLEVEL=1

.END

将网表文件导入HSpui中进行仿真,得到lis等文件,并用Avanwaves软件进行观察结果。

结果图如下:

四·

仿真分析

延迟分析:

在网表文件中添加下列语句

.measuretrantpdrtrigv(4)val=2.5rise=1targv(out)val=2.5fall=1

.measuretrantpdftrigv(4)val=2.5rise=1targv(out)val=2.5fall=1

.measuretpdparam='

(tpdr+tpdf)/2'

并在.lis文件中查看结果,结果如下:

******transientanalysistnom=25.000temp=25.000*****

tpdr=340.1950ptarg=2.8402ntrig=2.5000n

tpdf=340.1950ptarg=2.8402ntrig=2.5000n

tpd=340.1950p

功耗分析:

在网表文件中添加.op语句,并在仿真结果.lis文件中查看:

****voltagesources

subckt

element0:

v10:

v20:

v30:

v40:

vcc

volts200.0000m200.0000m200.0000m200.0000m5.0000

current0.0.0.0.-226.4388n

power0.0.0.0.1.1322u

totalvoltagesourcepowerdissipation=1.1322uwatts

一位全加器的设计

一.原理(说明)

在计算机中2个二进制数之间的加减乘除算术运算都是由若干加法运算实现的.全加器是算术逻辑运算的重要组成部分,对其深入探索研究有重要的意义。

一位全加器及其表达式在将2个多位二进制数相加时,除了最低位以外,每位都应该考虑来自低位的进位,即将2个对应位的加数和来自低位的进位3个数相加,实现这种运算电路即是全加器.设A是加数,B是被加数,CI是来自低位的进位,S是本位的和,CO是向高位的进位.根据二进制数加法运算规则和要实现的逻辑功能,得出一位全加器真值表,

全加器除了两个1位二进制数相加以外,还与低位向本位的进位数相加.表为全加器的真值表。

Cin

Cout

Sum

由真值表可得出逻辑函数式

式中,Ai和Bi是两个相加的1为二进制数,Ci-1是由相邻低位送来的进位数,SI是本位的全加和,CI是向相邻高位送出的进位数。

一位全加器将A、B和进位输入Cin作为输入,计算得到和Sum以及最高位的进位输出Cout。

每一位得到的和与进位输出都直接受其上一位的影响,其进位输出也会影响下一位。

最终,整个全加器的和与输出都受进位输入Cin的影响。

二.设计过程

接下来用Cadence软件包,采用MOS管机构,对各个门电路进行设计,并最终整合成整个一位全加器。

2输入异或门的电路图

3输入或门的电路图

2输入与门的电路

最终形成的顶层电路图

三.运用Hspice进行仿真。

接下来根据电路图,写出各个部分的Hspice的网表文件,并运用hipice的子电路思想,整合整个一位全加器电路的网表文件,并添加激励,产生最后结果并验证

一位全加器的Hspice网表文件。

ADDER703

.GLOBALvdd!

.OP

.TRAN1N8u

.subcktor3abcy

m0net10a00nchL=1UW=20U

m1ynet1000nchL=1UW=20U

m2net10c00nchL=1UW=20U

m3net10b00nchL=1UW=20U

m4net14bnet033net033pchL=1UW=20U

m5ynet10vdd!

vdd!

pchL=1UW=20U

m6net10cnet14net14pchL=1UW=20U

m7net033avdd!

.MODELNCHNMOSLEVEL=1

.MODELPCHPMOSLEVEL=1

.endsor3

.subcktand2aby

m0ynet1000nchL=1UW=20U

m1net10anet3net3nchL=1UW=20U

m2net3b00nchL=1UW=20U

m3ynet10vdd!

m4net10bvdd!

m5net10avdd!

.endsand2

.subcktxor2aby

m0yanet27net27nchL=1UW=150U

m1net27b00nchL=1UW=150U

m2ynet1100nchL=1UW=150U

m3net11b00nchL=1UW=150U

m4net11a00nchL=1UW=150U

m5net11bnet020net020pchL=1UW=5U

m6net020avdd!

pchL=1UW=5U

m7net018net11vdd!

m8net018ayypchL=1UW=5U

m9net018byypchL=1UW=5U

.endsxor2

xi3net13net10net7coutor3

xi5bcinnet7and2

xi4cinanet10and2

xi2abnet13and2

xi1net14cinsumxor2

xi0abnet14xor2

VAagndPULSE050N1N1N1u2u

VBbgndPULSE050N1N1N2u4u

VCcingndPULSE050N1N1N4u8u

V1vdd!

0dc=5

将网表文件导入到hspui软件中进行仿真,再用Avanwaves软件观察结果。

一位全加器的Hspice结果截图。

结果如下:

在网表文件中添加下列语句:

.measuretrantpdrtrigv(a)val=2.5rise=2targv(sum)val=2.5fall=2

.measuretrantpdftrigv(a)val=2.5rise=2targv(cout)val=2.5fall=2

结果:

adder703

******transientanalysistnom=25.000temp=25.000*****

tpdr=-1.9985utarg=2.0020utrig=4.0005u

tpdf=1.0013utarg=5.0018utrig=4.0005u

tpd=-498.5775n

功耗结果:

因为之前有添加.OP语句,所以可以直接从lis文件中查看到

voltagesources

subckt

element0:

va0:

vb0:

vc

volts5.00000.0.0.

current-145.3239p0.0.0.

power726.6195p0.0.0.

otalvoltagesourcepowerdissipation=726.6195pwatts

总结:

这次课设真可谓步步艰辛,整个课设的过程中,遇到了许多的困难,主要因为之前没有接触过HSPICE,在网表文件的编写遇到了很大的困难,好在在团队的努力下,查阅资料,网上搜索相关教学,通过调用子电路的方式,完成了整个课设。

同时让我感受到我在这次课设中我只是学到了Hspice软件的一点皮毛,它的强大之处,还需要我继续的学习,才能领悟。

同时,也让我深刻体会到,团队精神,团队合作的重要性,如果没有大家齐心协力的努力,我想这个课设将无法完成。

这也是我以后更加需要学习的地方。

课设虽然只是暂时的,但是学习与探索精神却必须是我们都要具备的思想,学海无涯,继续学习,才能更好的提高我们的自身素质,锻炼我的意志,让我们能在以后步入社会的生活中走得更远,走的更好。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 最新 一位 全加器 HSPICE 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx