彩灯循环控制电路设计 精品文档格式.docx

彩灯循环控制电路设计 精品文档格式.docx

- 文档编号:17070208

- 上传时间:2022-11-28

- 格式:DOCX

- 页数:19

- 大小:578.34KB

彩灯循环控制电路设计 精品文档格式.docx

《彩灯循环控制电路设计 精品文档格式.docx》由会员分享,可在线阅读,更多相关《彩灯循环控制电路设计 精品文档格式.docx(19页珍藏版)》请在冰豆网上搜索。

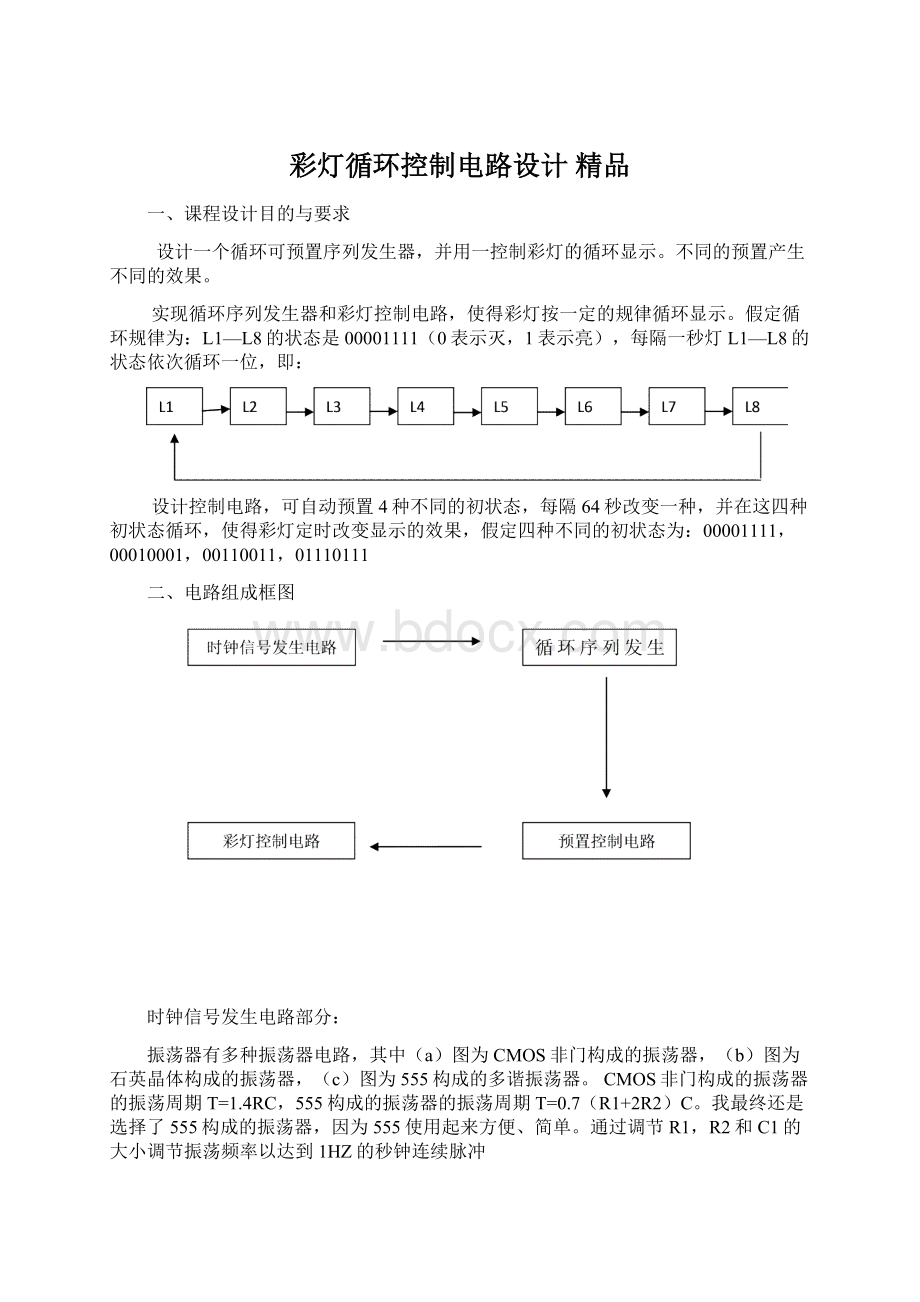

3个74LS163构成循环序列发生器部分,由于是64秒改变一种状态,所以用二片74LS163组成一个64位加法计数器(按16ⅹ4进行把2个74LS163组装计数器),每循环一次64位产生一个进位输入到第三个74LS163,第三个74LS163是一个4位加法计数器,并通过它来控制预置控制电路中的4个73LS373的使能端,从而决定输入的每种初态。

详细的控制办法是:

让第三个74LS16的输出00分别通过一个非门变成11再和头2个74LS163的进位一起通过一个三输入与非门变成低电平0加到初态为00001111的74LS373的使能端,这样就可以使器导通。

当前面的64位计数器在来一个进位时,00变成01,这样让1的那个输出端通过一个非门,然后和0的端口以及刚才的进位一起通过个与非门,是输出为0节到初态为00010001的第二个74LS373的使能端,让其导通。

再次过64秒后,计数器产生一个进位使第三个74LS373输出为10,让1的端口通过一个非门,然后把它和0的端口以及进位信号一起输送到一个三输入与非门,使之输出为0接到初态为00110011的第三个74LS373的使能端让其工作。

最后在完成一次64位的计数,产生一个进位,使之变成11,把他们都风别通过一个非门,然后在和进位信号一起通过一个三输入的与非门,并把它的输出0接到滴4个初态为01110111的74LS373的使能端,使其工作。

由于第三个的74LS373是一个4位加法计数器,所以当到了11时自己又自动返回到00,加法器完成一个64计数,就产生一个进位,00又变为01。

依次往复循环。

预置控制电路部分:

4个74LS373构成预置控制电路部分,因为存在4种不同的初态,考虑到74LS373的高阻态而且它拥有8个输出端正好符合要求,所以我们可以把这4种初态预先寄存在此。

由于使能端关闭时74LS373的输出是呈现高阻态所以可以把他们的输出端直接相互连在一起然后分别送至2个74LS194移位寄存器的输入端。

把四个74LS373的Q1都连在一起放到第一个74LS194的第一个输入端,然后把四个74LS373的Q2都连在一起放到第一个74LS194的第二个输入端,依次放置,直道把四个74LS373的Q8连在一起放到第二个74LS194的第四个输入端。

除此之外,我们还应把所存信号始终至于高电平。

就可以保证当使能信号一存在就可以输出一开始就寄存在器件里的数据。

彩灯控制电路部分:

2个74LS194构成彩灯控制电路的主电路,8个彩灯分别接在2个的输出端,考虑到题目要求8种状态是右移的,我们只需把每个的SR端和Q3端相连即可实现右移。

由于当S0S1是11时置数,S0S1是10时实现右移,所以我们可以把64位加法计数器部分产生的进位作为S1的输入信号送给S1,于是当产生一个进位时,74LS373输出的状态就可以顺利的置入双向移位寄存器74LS194内,当这个脉冲过来后时,S1又变为0,于是就可以实现右移了。

以上所有的期间的脉冲信号都是同一个脉冲信号,均由555定时器来产生,以保证同步。

三、元器件清单

本次课程设计所用器件如表一:

型号

名称

数目

74LS194

双向移位寄存器

2

74LS163

十六进制加法计数器

3

74LS373

数据寄存器

4

74LS04

非门

74LS12

三输入与非门

74LS08

与门

1

74LS00

与非门

555定时器

脉冲信号发生器

1)74LS194移位寄存器

其中D0,D1,D2,D3为并行输出端;

SR为右移串行输入端,SL为左移串行输入端;

S1,S0为操作模式控制端;

CP为时钟脉冲输入端。

内部原理图

2)74LS163计数器

它是同步十六进制加法记数器,当LOAD端输入底电平时处于预置数状态,D0、

D1、D2、D3的数据将会在CP上升沿到达时被置入Q0、Q1、Q2、Q3中,它的预置数是同步的。

下图是74LS163的引脚分配图,图中LD为预置数控制端,D0-D3为数据输入端,C为进位输出端,RC为异步置零端,Q0-Q3位数据输出端,EP和ET为工作状态控制端。

163的清除是同步的。

当清除端CLEAR为低电平时,在时钟端(CLK)上

升沿作用下,才可完成清除功能。

163的预置是同步的。

当置入控制端LOAD为低电平时,在CLK上升沿

作用下,输出端(QA-QD)与数据输入端(A-B)相一致。

当CLK由低至高跳变或跳变前,如果计数控制端(ENP、ENT)为高电平,则LOAD应避免由低至高电平的跳变.

163的计数是同步的,靠CLK同时加在4个触发器上而实现。

当ENP和ENT

均为高电平时,在CLK上升沿作用下QA-QD同时变化,从而消除了异步计数器中

出现的计数尖峰。

163有超前进位功能。

当计数溢出时,进位端(RCO)输出一个高电平脉冲,其宽度为Q0的高电平部分。

在不外加门电路的情况下,可级联成N位同步计数器。

在CLK出现前,即使ENP、ENT、CLEAR发生变化,电路的功能也不受影响。

3)74LS373寄存器

74LS373是八D锁存器(3S,锁存允许输入有回环特性),常应用在地址锁存及输出口的扩展中。

74LS373内有8个相同的D型(三态同相)锁存器,由两个控制端(11脚G或EN;

1脚OUT、CONT、OE)控制。

当OE接地时,若G为高电平,74LS373接收由PPU输出的地址信号;

如果G为低电平,则将地址信号锁存。

工作原理:

74LS373的输出端O0~O7可直接与总线相连。

当三态允许控制端OE为低电平时,O0~O7为正常逻辑状态,可用来驱动负载或总线。

当OE为高电平时,O0~O7呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端LE为高电平时,O随数据D而变。

当LE为低电平时,O被锁存在已建立的数据电平

引角图

内部逻辑图

真值表

4)555定时器应用

国产双极型定时器CB555电路结构图。

它是由比较器C1和C2,基本RS触发器和集电极开路的放电三极管TD三部分组成。

VH是比较器C1的输入端,v12是比较器C2的输入端。

C1和C2的参考电压VR1和VR2由VCC经三个五千欧电阻分压给出。

在控制电压输入端VCO悬空时,VR1=2/3VCC,VR2=1/3VCC。

如果VCO外接固定电压,则VR1=VCO,VR2=1/2VCO.

RD是置零输入端。

只要在RD端加上低电平,输出端v0便立即被置成低电平,不受其他输入端状态的影响。

正常工作时必须使RD处于高电平。

图中的数码1—8为器件引脚的编号。

图

(2)555定时器逻辑符号

555定时器是一种中规模集成电路,只要在外部配上适当阻容元件,就可以方便地构成脉冲产生和整形电路。

图(3)555定时器内部结构图

(A)电路组成

555集成定时器由五个部分组成。

1、基本RS触发器:

由两个“与非”门组成

2、比较器:

C1、C2是两个电压比较器

3、分压器:

阻值均为5千欧的电阻串联起来构成分压器,为比较器C1和C2提供参考电压。

4、晶体管开卷和输出缓冲器:

晶体管VT构成开关,其状态受

端控制。

输出缓冲器就是接在输出端的反相器G3,其作用是提高定时器的带负载能力和隔离负载对定时器的影响。

(B)基本功能

当

时,

,输出电压

为低电平,VT饱和导通。

时,C1输出低电平,C2输出高电平,

,Q=0,

,

饱和导通。

、

时,C1、C2输出均为高电平,基本RS触发器保持原来状态不变,因此

、VT也保持原来状态不变。

时,C1输出高电平,C2输出低电平,

,Q=1,

,VT截止。

555定时器功能表

输入

输出

阈值输入(vI1)

触发输入(vI2)

复位(

)

输出(

放电管T

×

导通

截止

导通

不变

表

(2)555定时器逻辑功能表

5)74LS04非门

当输入信号为高电平时,应保证三极管工作在深度饱和状态,以使输出电平接近于零。

为此,电路参数的配合必须合适,保证提供给三极的基极电流大于深度饱和的基极电流。

仔细观察一下图中给出的三极管开关电路即可发现,当输入为高电平时输出等于低电平,而输入为低电平时输出等于高电平。

因此输出与输入的电平之间是反向关系,它实际上就是一个非门。

(亦称反向器)。

为此,电路参数的配合必须合适,保证提供给三极的基极电流大于深度饱和的基极电流。

设计电路所用的芯片是74LS04,如下图所示:

图(6)74LS04的内部结构图

功能表如下图:

表(4)非门功能表

逻辑符号

逻辑函数式Y=A

74LS04的管脚图

6)74LS12三输入与非门

引出端符号1A-3A输入端

1B-3B输入端

1C-3C输入端

功能表:

四、各功能块电路图

1)555多谐振荡器组成脉冲发生器

多谐振荡器不需要外加输入信号,只要加上直流电源就能自动输出相应频率和宽度的矩形脉冲。

由于矩形脉冲含有丰富的高次谐波,所以称为多谐振荡器。

多谐振荡器电路能从一种状态翻转到另一种状态,变化极其迅速。

多谐振荡器的稳定度及频率的准确度决定了数字钟计时的准确程度,通常选用成品振构成振荡器电路。

一般来说,振荡器的频率越高,计时精度越高。

如果精度要求不高也可采用集成逻辑门与RC组成的时钟源振荡器或由集成定时器555与RC组成的多谐振荡器。

参考电路图如图所示:

图8多谐振荡器

输出波形图如下所示:

振荡器是数字钟的核心。

振荡器的稳定度及频率的准确度决定了数字钟计时的准确程度,通常选用成品振构成振荡器电路。

这里选用555组成的多谐振荡器,多谐振荡器的频率可以设为为f0=1000HZ。

2﹚循环序列发生器

两个16进制加法计数器构成了一个64进制的计数器,由于是64秒改变一种状态,所以用从右开始数的前二片74LS163组成一个64位加法计数器(按16ⅹ4进行把2个74LS163组装计数器),每循环一次64位产生一个进位输入到第三个74LS163,第三个74LS163是一个4位加法计数器,并通过它来控制预置控制电路中的4个73LS373的使能端,从而决定输入的每种初态。

用最左边的74LS163组成一个4进制的加法计数器。

电路图如下:

3)预置控制电路:

74LS373构成预置控制电路部分,因为存在4种不同的初态,考虑到74LS373的高阻态而且它拥有8个输出端正好符合要求,所以我们可以把这4种初态预先寄存在此。

4)控制显示电路

体现了题目要求的4种初态,64秒变换的方式

五、仿真电路总图

在Multism20XX中仿真此电路,64位的加法计数器每完成一次64计数,就会产生个进位信号,这个进位信号会控制4进制加法计数器的计数端使其计数,4进制的法计数器没产生一个数会和那个64位的进位信号一起通过一系列TTL门电路到达73LS373控制的预置电路。

通过控制其使能端来控制初态的导入。

我把4种不同的初态接到了两片74LS194的输入端,考虑到题目是要求右移,我把S1的直接和64位的进位信号端接到了一起,把S0一直接高电平。

有进位信号时,S0S1是11会把一种初态置进去。

01时又会实现右移。

自动预置4种不同的初状态,每隔64秒改变一种,并在这四种初状态循环,使得彩灯定时改变显示的效果,四种不同的初状态为:

00001111,00010001,00110011,0111011164秒变换一种初态,变换初态后的64秒内是一直在循环右移的。

依次往复运行。

经过对以上各个步骤的总结可以的到最终的结果,通过软件对最后的结果进行仿真,验证本次试验设计的正确性。

总体的电路图和仿真结果如下:

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 彩灯循环控制电路设计 精品 彩灯 循环 控制电路 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《雷雨》中的蘩漪人物形象分析 1.docx

《雷雨》中的蘩漪人物形象分析 1.docx