16位全加器Word文档下载推荐.docx

16位全加器Word文档下载推荐.docx

- 文档编号:16845443

- 上传时间:2022-11-26

- 格式:DOCX

- 页数:12

- 大小:247KB

16位全加器Word文档下载推荐.docx

《16位全加器Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《16位全加器Word文档下载推荐.docx(12页珍藏版)》请在冰豆网上搜索。

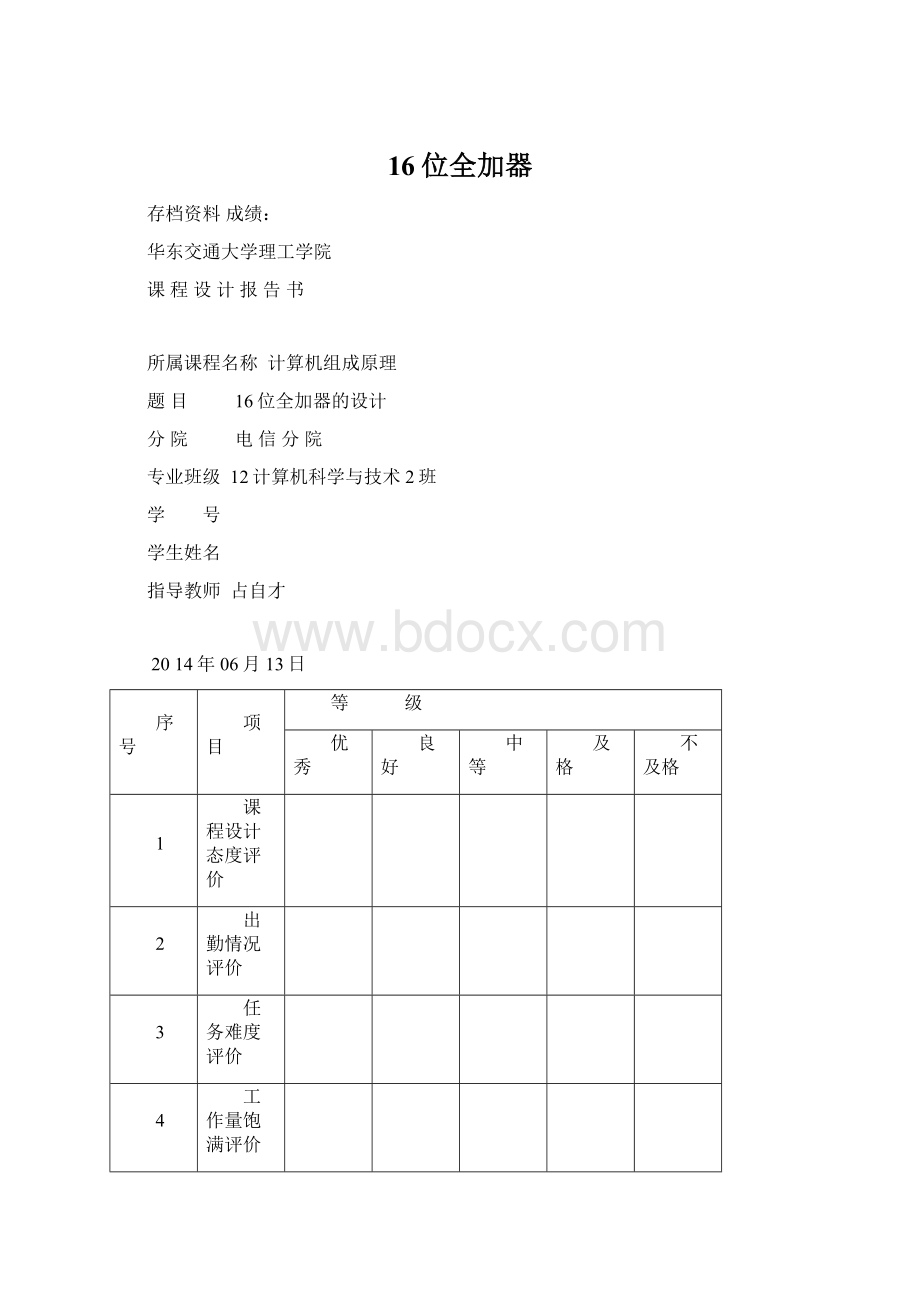

工作量饱满评价

5

6

设计中创新性评价

7

论文书写规范化评价

8

综合应用能力评价

综合评定等级

课程设计(论文)评阅意见

评阅人 职称

20年月日

第1章课程设计内容及要求

了解计算机的硬件系统,了解一位全加器的组成原理,深入讨论计算机的组成原理,在熟悉常用的门电路的组成和工作过程的基础上,要求设计出一个16位的全加器。

其中要求设计并写出产生求和结果的逻辑表达式,需要写出利用快速进位链产生进位的逻辑表达式,同时还要实现时需要用一个时钟信号控制运算的执行,如第一拍给出输入数据,第二拍给出运算控制信号,第三拍送输出数据,然后又回到第一拍,循环往复,直到运算全部结束。

根据要求设计出针对具体指令所对应的流程图;

根据流程及门电路设计出相应的全加器。

编写出VHDL程序,在仿真软件上运行并检验所设计的微程序的正确性。

第2章设计过程

2.1硬件方案

2.1.1一位全加器的原理及设计

2.1.1.1一位全加器的工作原理

全加器是实现两个一位二进制数及低位来的进位数相加即将三个一位二进制数相加,求得和数及向高位进位的逻辑电路。

全加器是组合逻辑电路中最常见也最实用的一种,考虑低位进位的加法运算就是全加运算,实现全加运算的电路称为全加器。

它主要实现加法的运算,其中分为并行全加器和串行全加器,所谓并行就是指向高位进位时是并行执行的,而串行就是从低位到高位按顺序执行,为了提高运算,必须设法减小或消除由于进位信号逐级传递所消耗的时间,为了提高运算速度,制成了超前进位加法器,这是对全加器的一种创新。

2.1.1.2一位全加器的设计

要使全加器进行加法运算,也需要用各种门电路设计出相应的逻辑电路,根据组合逻辑电路设计的步骤,我们先设计一位全加器的设计。

(1)根据全加器所需要的功能,我们可以设计出一位全加器的组合逻辑框图。

如图3.1所示。

图3.1一位全加器的逻辑结构

(2)根据逻辑图我们可以写出各个器件的逻辑功能。

Ci=XiYiCi-1+XiYiCi-1+XiYiCi-1+XiYiCi-1=(Xi

Yi)Ci-1+XiYi

Fi=XiYiCi-1+XiYiCi-1+XiYiCi-1+XiYiCi-1=Xi

Yi

Ci-1

(3)由上面可得。

Xi和Yi为两个输入的一位二进制书,Ci-1为低位二进制数相加的进位输出到本位的输入,则Fi为本位二进制数Xi、Yi和低位进位输入Ci-1的相加之和,Ci为Xi、Yi和低位进位输入Ci-1相加向高位的进位输出。

因此,该电路可以完成一位二进制数全加的功能,称为全加器。

此电路的真值表如表3-1所示。

表3-1一位全加器真值表

Xi

Ci-1

Fi

Ci

2.1.2四位全加器的原理及设计

2.1.2.1四位全加器的工作原理

加法器是数字系统中的基本逻辑器件。

例如:

为了节省资源,减法器和硬件乘法器都可由加法器来构成。

但宽位加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。

多位加法器的构成有两种方式:

并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;

串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

四位全加器可对两个多位二进制数进行加法运算,同时产生进位。

当两个二进制数相加时,较高高位相加时必须加入较低位的进位项(Ci),以得到输出为和(S)和进位(C0)。

2.1.2.2四位全加器的设计

设计四位全加器有两种方案,一种利用串行进位方式设计,另一种是利用并行进位方式进行设计。

但是这两种方式设计的电路的工作效率是恨不一样的,串行进位是需要等待低位计算的所得的进位后才能进行高位的运算的,而并行进位也就是先进位方式,每个进位只需要经历一个与非门和一个与或门的延时,这样和串行进位相比,大大提高了运算速度。

所以我们这里选择先进位全加器。

四位先行进位全加器的真值表如表3-2所示。

表中的C0为低位向高位的进位,P1~P4以及G1~G4为输入端,C1~C4为输出端。

表3-2四位先行进位全加器真值表

C0

P1

G1

P2

G2

P3

G3

P4

G4

C1

C2

C3

C4

四位加法器可以采用四个一位全加器级连成串行进位加法器,如图3.2所示,其中CSA为一位全加器。

图3.2四位先行进位加法器逻辑结构

如图3.3所示,四位先行进位全加器各个进位信号的产生只需要经历一级与非门和一级与或非门的延迟时间,所以比逐位进位全加器大大缩短了时间。

图3.3四位先行进位加法器原理

2.1.3十六位全加器的原理及设计

2.1.3.1十六位全加器的原理

16位全加器设计的基本思想,就是仿照通常的解组合逻辑电路的方法,先把原理图画出来,然后通过原理图把各个信号量描述出来,最后再根据各个器件的逻辑功能列出真值表。

当全加器工作时,先一个一个二进制数全部按位输入,从而在4位先行进位的加法器中进行运算,使相应部件执行所规定的操作。

2.1.3.2十六位全加器的设计

设计16位全加器,这里使用的方法是把4个四位全加器串联起来。

16位全加器主要由输入、输出、进位和4位先行进位的加法器这四部分组成,其原理如图3.4所示。

图3.4十六位全加器组成原理图

16位全加器总共有16位输入,而每四位为一组输入到4位先行进位加法器中进行加法运算,一般输入是两位二进制数,如图是:

Y4-1X4-1一直到Y16-13X16-13为输入;

输出为F,共16位输出,而和输出一样四位为一组一起经过运算后输出,不同的是输入有两个二进制数,而输出只有一个二进制数;

C表示进位,C0初始值为1,后面的C4,C8,C12,C16分别是每个四位加法器运算后的进位。

2.2软件方案

用VHDL编写代码验证:

在对真值表进行分析和各个功能设计完成之后,就可以使用VHDL编写程序,运用MAX-PLUSⅡ进行模拟仿真,以验证其正确性。

如下就是四位先行进位全加器和16位全加器的VHDL代码。

//导入各种所需要的库

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

--Uncommentthefollowinglinestousethedeclarationsthatare

--providedforinstantiatingXilinxprimitivecomponents.

--libraryUNISIM;

--useUNISIM.VComponents.all;

entitytestis

port(

a,b:

instd_logic_vector(3downto0);

//a,b为输入,为4位标准逻辑矢量类型

cin:

instd_logic;

//cin为输入,为标准矢量类型

s:

outstd_logic_vector(3downto0);

//s为输出,为4位标准逻辑矢量类型

cout:

outstd_logic);

//cout为输出,为标准矢量类型

endtest;

architectureBehavioraloftestis

signald,t:

std_logic_vector(3downto0);

//信号量d,t为4位标准逻辑矢量

signalc:

std_logic_vector(4downto0);

//信号量c为5位标准逻辑矢量

begin

as_add:

foriin0to3generate//i从0循环到3,循环4次

d(i)<

=a(i)andb(i);

//把a,b相与的结果赋给d

t(i)<

=a(i)orb(i);

//把a,b相或的结果赋给t

s(i)<

=a(i)xorb(i)xorc(i);

//把a,b,c进行异或的结果赋给s

endgenerate;

//以下为赋值语句

c(0)<

=cin;

c

(1)<

=d(0)or(t(0)andc(0));

c

(2)<

=d

(1)or(t

(1)andd(0))or(t

(1)andt(0)andc(0));

c(3)<

=d

(2)or(t

(2)andd

(1))or(t

(1)andt

(2)andd(0))or(t

(1)andt

(2)andt(0)andc(0));

c(4)<

=d(3)or(t(3)andd

(2))or(t(3)andt

(2)andd

(1))or(t

(1)andt

(2)andt(3)andd(0))or(t(3)andt

(2)andt

(1)andt(0)andc(0));

cout<

=c(4);

endBehavioral;

如下是16位全加器的VHDL代码。

useIEEE.std_logic_1164.all;

//导入各种需要的库

entityadder16is

generic(n:

integer:

=16);

port(a:

instd_logic_vector(16downto1);

//a为16位标准逻辑矢量类型的输入

b:

//b为16位标准逻辑矢量类型的输入

cin:

instd_logic;

//c为标准逻辑类型的输入

sum:

outstd_logic_vector(16downto1);

//sum为16位标准逻辑矢量类型的输入

cout:

outstd_logic);

endadder16;

--structuralimplementationofthe16-bitadder

architecturestructuralofadder16is

componentadder

//以下a,b,cin,sum,cout都为标准逻辑类型,其中a,b,cin为输入,sum,cout为输出

outstd_logic;

endcomponent;

signalcarry:

std_logic_vector(0to16);

carry(0)<

=cin;

//把信号量cin的值赋给carry(0)

cout<

=carry(16);

//把信号量carry(16)的值赋给cout

--instantiateasingle-bitadder16times

gen:

forIin1to16generate//I从1循环至16,循环16次

add:

adderportmap(

//以下为赋值语句

a=>

a(I),

b=>

b(I),

cin=>

carry(I-1),

sum=>

sum(I),

cout=>

carry(I));

endgenerate;

endstructural;

--behavioralimplementationofthe16-bitadder

architecturebehavioralofadder16is//定义结构体

p1:

process(a,b,cin)//过程开始

variablevsum:

std_logic_vector(16downto1);

variablecarry:

std_logic;

begin

carry:

foriin1to16loop//I从1循环至16,循环16次

vsum(i):

=(a(i)xorb(i))xorcarry;

//变量vsum(i)的赋值

=(a(i)andb(i))or(carryand(a(i)orb(i)));

//变量carry的赋值

endloop;

sum<

=vsum;

//把vsum赋给信号量sum

=carry;

//把carry赋给信号量cout

endprocessp1;

//进程结束

endbehavioral;

第3章测试

根据4位先行进位全加器VHDL的代码,用MAX-PLUSⅡ进行模拟,得到仿真图,如图3.5所示

图3.5四位先行进位全加器仿真图

根据表3-2和图3.5,可以进行分析四位先行进位全加器的正确性,用表中的数据和图中所表示出来的数据段进行对比分析,如图3.5,第一行为cin的输入值,对应表中的C0;

第二行为cout进位信号量的输出;

第三行是a的输入值,对应表中的Gi;

第四行为b的输入值,对应表中的Pi;

第五行为s的输出值,对应表中的Ci。

由分析可得,四位先行进位全加器的设计和仿真以及真值表的建立的过程都是正确的。

根据十六位全加器的VHDL代码,用MAX-PLUSⅡ进行模拟,得到仿真图,如图3.6所示。

图3.6十六位全加器仿真图

图3.6中,第一行cin为信号量初试值,第二行cout为信号量进位的输出,第三行和第四行中的a和b都为输入,第五行sum为16位的结果输出,从图中分析可得,十六位全加器的设计是正确的,能准确的执行十六位二进制数的加法运算。

第4章课程设计心得

通过本次课程设计对全加器的设计和实现,确实积累和总结了不少的经验,锻炼了我独立工作和实际动手能了,加深了对计算机中的全加器工作原理的认识,提高了对复杂的综合性时间环节具有分析问,解决问题概括总结的实际工作能力,对涉及全加器项目开发、设计过程有了初步认识。

经过了一周的设计和开发,门电路设计的16位全加器基本设计完毕。

其功能基本符合用户需求,能够玩成16位进位加法的运算。

但是由于课程设计时间较短,还有许多不尽如人意的地方。

从中我学到了不少的道理,真正理解到,理论与实践之间还是有很大的距离,这必将有利于我们以后的学习。

使我明白,在以后的学习中,要不断的完善自己的知识体系结构,注意理论与实践的结合,学知识的关键是要学活,而不能死记死搬书本上的知识,关键是要会灵活运用,这样所学到的东西才真正的学以致用,才达到了学习的真正目的。

在本次的课程设计中,我学到了很多东西,通过本次课程设计,无论在理论上还是在实践中,我的计算机应用水平得到了很大的提升,这对于今后的工作和学习都是一种巨大的财富。

参考文献

[1].彭蔓蔓计算机组成原理[M].上海:

上海交通大学出版社,2012年10月

[2].唐朔飞计算机组成原理[M].北京:

高等教育出版社,2010年01月

[3].白中英计算机组成原理(第五版)[M].科学出版社2013年03月

[4].秦磊华计算机组成原理(计算机系列教材)北京清华大学出版社2011年02月

[5].罗克露计算机组成原理[M]高等教育出版社.2010年07月

致谢

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 16 全加器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx