Allegro166约束管理系统器及使用示例Word格式文档下载.docx

Allegro166约束管理系统器及使用示例Word格式文档下载.docx

- 文档编号:16773077

- 上传时间:2022-11-26

- 格式:DOCX

- 页数:10

- 大小:704.92KB

Allegro166约束管理系统器及使用示例Word格式文档下载.docx

《Allegro166约束管理系统器及使用示例Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《Allegro166约束管理系统器及使用示例Word格式文档下载.docx(10页珍藏版)》请在冰豆网上搜索。

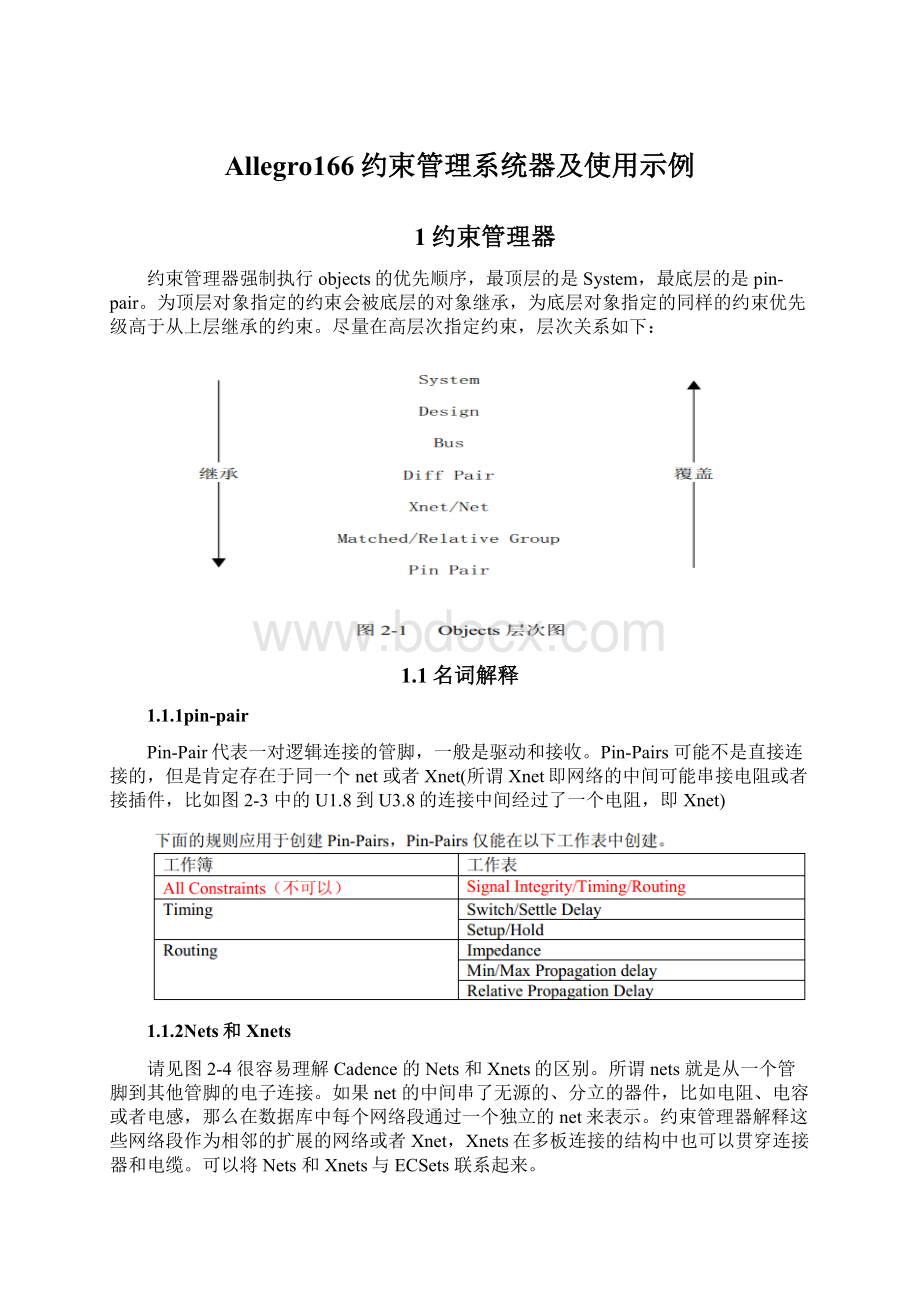

1.1.3MatchGroups

MatchGroup是nets,Xnets或者pin-pairs的集合,此集合一定要都匹配(delay或者length)或者相对于组内的一个明确的目标。

如果delta值没有定义,组内的所有成员都将是

绝对匹配的,并允许有一定的偏差。

如果定义了delta值,那么组内所有成员将相对匹配于

明确的目标网络。

1.2在线检查设置

首先在约束管理器中需要进展以下设置

Analyze->

AnalysisModes

这样在布线后,在相应的地方都会显示线长或约束相差值;

如如下图

1.3示例

通过一个实例来理解约束管理器

U1看作是MCU,

U2为DDR,ADDR0-3为地址线,需要作等长处理;

CLK为时钟线,差分处理;

U3,U4为连接同一个MCU的DDR;

地址线是复用的,设置通过T型网络连接;

需要作等长处理

U5为DDR,DDR_DQ0-3为数据线,需要作等长处理

1.3.1差分对约束

即上图中的DDR_CLKP,DDR_CLKN

设置Electrical->

ElectricalConstraintSet->

DifferentialPair

在Object的Name下方Project右键Create->

ElectricalCSet;

并输入参数

差分对约束参数主要有以下几个:

Minlinespacing:

内间距最小线距,假设实际走线内间距小于这个值,DRC就会出错。

PrimaryGap:

默认内间距,差分对最优先线间距〔边到边间距〕。

Primarywidth:

默认线宽,差分对最优先线宽。

NeckGap:

NECKMODE模式下默认内间距差分对Neck模式下的线间距〔边到边间距〕,用于差分对走线在布线密集区域时切换到Neck值。

(NECK下的线宽用于NECKMODE下的线宽,一般在bga下面走线的时候有时候两个管脚间距过小,需要使用NECKMODE,走线时,鼠标右键,选择NECKMODE即进入NECK模式。

)

NeckWidth:

NECKMODE模式下默认线宽差分对Neck模式下的线宽,用于差分对走线在布线密集区域时切换到Neck值;

DynamicPhase:

动态相位检查,在16.3版本新参加的功能。

对差分对路径中每个转角之间造成的路径差异进展检查。

如在整个差分对网络中,正向与反向之间的走线差距不能超过“xmils〞。

如果整个路径中的某一个位置,发生了两个信号之间相位偏移超过了规定的“xmils〞,这个误差必须在“ymils〞X围内补偿回来。

如如下图x=20,y=600.设定约束时tolerance填入x值,maxlength填入y值。

StaticPhaseTolerance:

这个约束设置了两根差分线之间的差值,单位是mil或ns。

设置了此项后,在走线时会实时的显示走线差,在绿灯时符合约束。

Uncoupledlength:

该约束限制了差分对的一对网络之间的不匹配长度。

差分对刚刚从芯片出来的走线通常是不耦合的,“gathercontrlo〞可以设置为“ignore〔忽略〕〞和“include〔包括〕〞,意思为在计算不匹配长度时是否包含差分对刚从芯片出来的这段不耦合的线长。

然后在Net->

routing->

DifferentialPair中,这时差分对就可以选择刚刚设置的规如此了;

选中规如此布线后如如下图

1.3.2设置不过电阻的NET等长

即上图中的DDR_DQ0-3,布线要求,DQ1-3以DQ0为参考,线长在±

10mil内

Net->

Routing->

RelativePropagationDelay

选中所需NET,右键Create->

MatchGroups,弹出的对话框中命名约束条件并确定;

假设是先已经创建了MG_DQGROUP,需要添加其他的NET,选中需要添加的NET,右键,Addto->

MatchGroups;

选择已有的约束条件添加;

在刚刚设置的网络组中,可以选择其中的一根作为参考,在对应的【Delta:

tolerance】栏中右键Setastarget,即可设置为参考网络;

假设不设置参考网络,如此所有的网络都要匹配到+tolerance;

【Delta:

tolerance】

100mil:

10mil假设参考线1000mil,如此线X围为1000+100加减10mil;

即990~1110mil

-100mil:

10mil假设参考线1000mil,如此线X围为1000-100加减10mil;

890~990mil

布线后如图:

1.3.3设置过电阻的XNET等长

即上图中的ADDR0-3,布线要求,ADDR1-3以ADDR0为参考,线长在±

设置XNet

ModelAssigment;

弹出对话框,可以选择某种电阻,也可以选择某个电阻;

现在选中某种电阻;

Create->

Model;

弹出对话框默认确定,在弹出如下对话框;

因为在原理图中,ADDR3_A和ADDR3连接排阻的1和8;

类推,所以是以1826....对应;

如如下图,ADDR3_A和ADDR3两条NET合并成一条XNRT;

创建Pin-Pair

在ADDR0上右键Create->

Pin-Pair;

选中电阻两端MCU和DDR的管脚腿

创建完后如如下图

创建MatchGroup

选中上面的4个PPr,右键Create->

MatchGroup;

接下来就和设置不过电阻的NET等长的步骤一样了;

布线之后如如下图

1.3.4设置T型等长

1.3.4.1在PCB和约束管理器中创建T型节点

在PCB菜单栏中选中Logic->

NetSchedule,然后选中要设置的T型网络的鼠线,在选中要设置网络的其中一个引脚,右键InsertT命令,在适宜的地方左键放置T点,然后选其他的引脚再选中刚放置的T点,依次设置完该T型网络上的所有的节点;

删除某个T节点,PCB菜单栏中选中Logic->

NetSchedule,选中网络右键UnscheduleNet,然后右键Done;

在约束管理器中,右键刚刚设置的那根Net,Create->

ElectricalCSet,命名,注意勾选CopyConstraintsFrom;

然后其他网络就可以使用这个规如此了。

然后在其他需要设置T型网络的NET中ReferencedElectricalCset中选中刚刚设置的规如此;

1.3.4.2在SigXplorer和约束管理器中创建

Electrical->

Wiring

选中需要设置T型网络的net,右键选中SigXplorer,进入界面,重新设置拓扑结果之后,注意上面有元件的编号,Set->

Constraints;

弹出界面,在Wiring中VerifySchedule中选中YSE,单击OK;

File>

UpdateConstraintManager;

到如下的拓扑结构:

然后在其他需要设置T型网络的NET中ReferencedElectricalCset中选中刚刚设置的规如此

然后通过Pin-Pair的方式设置等长

1.3.4.3设置线长

选中PropDelay标签,设置方法,在Pins/Tees中先选中T.2再选U4.4,在RuleType中选择Length,分别在minlength,maxlength中输入500,510;

依次把所有的都设置好;

上面解释:

从从T.2到U4.4的线长为500~510mil;

设置相对延时:

选中RelPropDelay标签,方法:

先在【RuleEditing】栏点击New按钮,

再点击U4.4

注意【Scope】栏为“Local〞,

在【DeltaType】栏,选择“None〞,

在【TolType】栏,选择“Length〞,

在【Tolerance】栏,输入“20〞,

点击ADD按钮。

按上面的方法设置其余三线;

单击OK;

注意:

。

好似走线有过孔时很麻烦,拓扑结构改变?

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Allegro166 约束 管理 系统 使用 示例

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

如何打造酒店企业文化2刘田江doc.docx

如何打造酒店企业文化2刘田江doc.docx