北航电子电路设计数字部分实验报告文档格式.docx

北航电子电路设计数字部分实验报告文档格式.docx

- 文档编号:16584713

- 上传时间:2022-11-24

- 格式:DOCX

- 页数:35

- 大小:712.67KB

北航电子电路设计数字部分实验报告文档格式.docx

《北航电子电路设计数字部分实验报告文档格式.docx》由会员分享,可在线阅读,更多相关《北航电子电路设计数字部分实验报告文档格式.docx(35页珍藏版)》请在冰豆网上搜索。

b[0]={$random}%2;

b[1]={$random}%2;

b[2]={$random}%2;

b[3]={$random}%2;

b[4]={$random}%2;

b[5]={$random}%2;

b[6]={$random}%2;

b[7]={$random}%2;

begin#100000$stop;

end

comparem(.equal(equal),.a(a),.b(b));

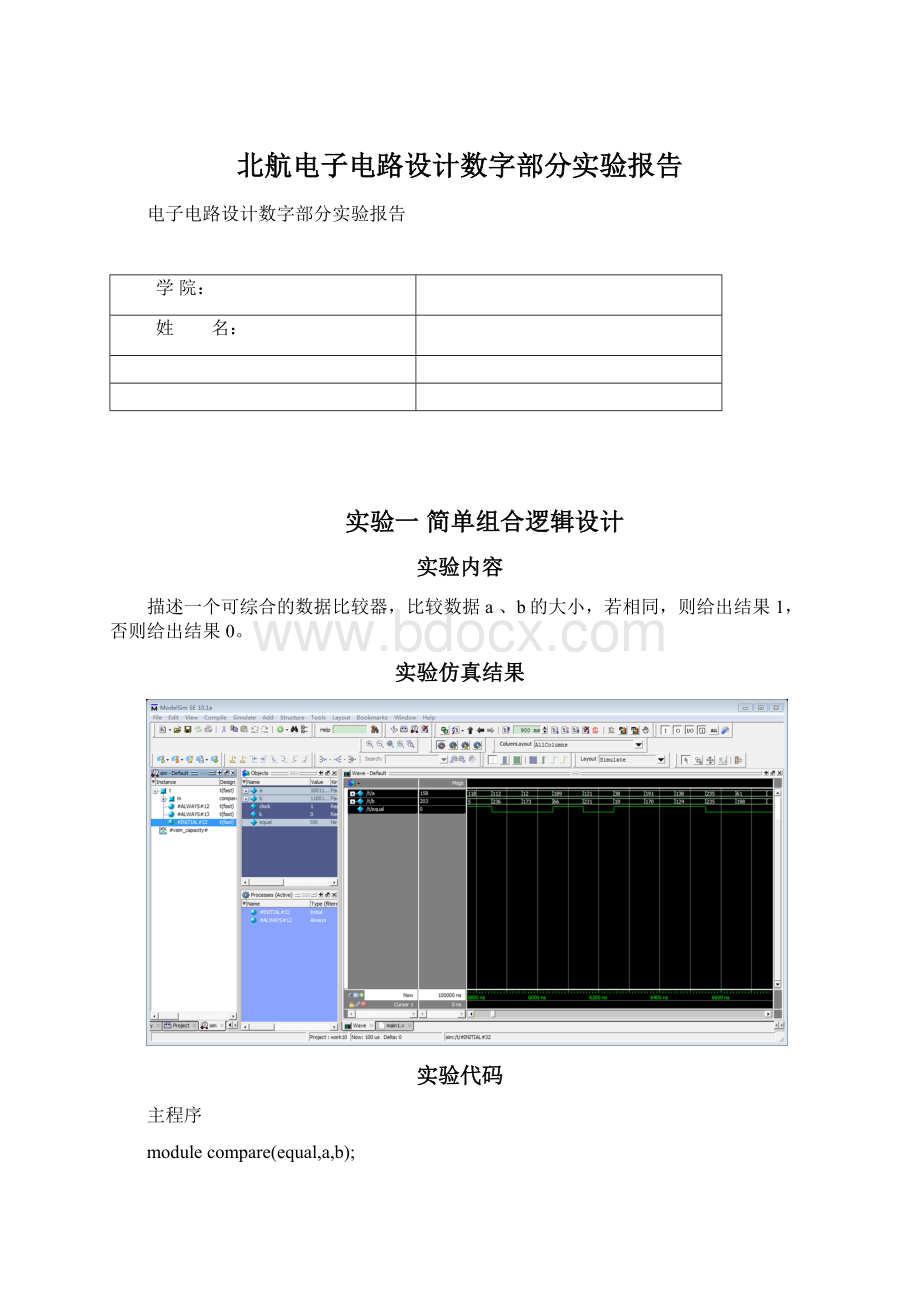

实验二简单分频时序逻辑电路的设计

用always块和@(posedgeclk)或@(negedgeclk)的结构表述一个1/2分频器的可综合模型,观察时序仿真结果。

modulehalf_clk(reset,clk_in,clk_out);

inputclk_in,reset;

outputclk_out;

regclk_out;

always@(negedgeclk_in)

if(!

reset)

clk_out=0;

else

clk_out=~clk_out;

`timescale1ns/100ps

`defineclk_cycle50

moduletop;

regclk,reset;

wireclk_out;

always#`clk_cycleclk=~clk;

clk=0;

reset=1;

#10reset=0;

#110reset=1;

#100000$stop;

half_clkm0(.reset(reset),.clk_in(clk),.clk_out(clk_out));

endmodule

实验三利用条件语句实现计数分频时序电路

利用10MHz的时钟,设计一个单周期形状的周期波形。

modulefdivision(RESET,F10M,out);

inputF10M,RESET;

outputout;

regout;

0]i;

always@(posedgeF10M)

RESET)

out<

=0;

i<

elseif(i==2||i==3)

out=~out;

=i+1;

elseif(i==5)

=1;

moduledivision_top;

regF10M,RESET;

wireout;

always#50F10M=~F10M;

RESET=1;

F10M=0;

#90RESET=0;

#100RESET=1;

#10000$stop;

fdivisionfdivision(.RESET(RESET),.F10M(F10M),.out(out));

实验四阻塞赋值与非阻塞赋值的区别

比较四种不同的写法,观察阻塞与非阻塞赋值的区别。

Blocking:

always@(posedgeclk)

b=a;

c=b;

Blocking1:

b=a;

Blocking2:

always@(posedgeclk)b=a;

always@(posedgeclk)c=b;

non_Blocking:

always@(posedgeclk)

b<

=a;

c<

=b;

End

moduleblocking(clk,a,b,c);

output[3:

0]b,c;

input[3:

0]a;

inputclk;

reg[3:

always@(posedgeclk)

测试部分

`timescale1ns/100ps

`include"

./blocking.v"

./blocking1.v"

./blocking2.v"

./non_blocking.v"

modulecompareTop;

wire[3:

0]b11,c11,b12,c12,b13,c13,b2,c2;

0]a;

regclk;

forever#50clk=~clk;

a=4'

h3;

$display("

%d"

a);

#100a=4'

h7;

hf;

ha;

h2;

#100$stop;

blockingblocking(clk,a,b11,c11);

blocking1blocking1(clk,a,b12,c12);

blocking2blocking2(clk,a,b13,c13);

non_blockingnon_blocking(clk,a,b2,c2);

实验五用always块实现较复杂的组合逻辑

实验目的

运用always块设计一个8路数据选择器。

要求:

每路输入数据与输出数据均为4位2进制数,当选择开关(至少3位)或输入数据发生变化时,输出数据也相应地变化。

modulealu(out,opcode,a1,a2,a3,a4,a5,a6,a7,a8);

0]out;

0]a0,a1,a2,a3,a4,a5,a6,a7;

input[2:

0]opcode;

always@(opcodeora1ora2ora3ora4ora5ora6ora7ora0)

case(opcode)

3'

d0:

out=a0;

d1:

out=a1;

d2:

out=a2;

d3:

out=a3;

d4:

out=a4;

d5:

out=a5;

d6:

out=a6;

d7:

out=a7;

default:

out=4'

b0000;

endcase

`timescale1ns/1ns

./main5.v"

modulealutext;

0]a1,a2,a3,a4,a5,a6,a7,a8;

reg[2:

a1={$random}%16;

a2={$random}%16;

a3={$random}%16;

a4={$random}%16;

a5={$random}%16;

a6={$random}%16;

a7={$random}%16;

a8={$random}%16;

repeat(100)

#100opcode={$random}%8;

alualu(out,opcode,a1,a2,a3,a4,a5,a6,a7,a8);

实验六在VerilogHDL中使用函数

设计一个带控制端的逻辑运算电路,分别完成正整数的平方、立方和最大数为5的阶乘运算。

moduletryfunct(clk,n,result1,result2,result3,reset);

output[31:

0]result1,result2,result3;

0]n;

inputreset,clk;

reg[31:

always@(posedgeclk)

reset)

result1<

result2<

result3<

=fun1(n);

=fun2(n);

=fun3(n);

function[31:

0]fun1;

0]operand;

fun1=operand*operand;

endfunction

0]fun2;

fun2=operand*operand;

fun2=operand*fun2;

0]fun3;

0]index;

fun3=1;

if(operand<

11)

for(index=2;

index<

=operand;

index=index+1)

fun3=index*fun3;

=10;

`include"

./main6.v"

moduletryfunctTop;

0]n,i;

regreset,clk;

wire[31:

n=0;

#100reset=0;

#100reset=1;

for(i=0;

i<

=15;

i=i+1)

#200n=i;

always#50clk=~clk;

tryfunctm(.clk(clk),.n(n),.result1(result1),.result2(result2),.result3(result3),.reset(reset));

实验七在VerilogHDL中使用任务(task)

用两种不同方法设计一个功能相同的模块,该模块能完成四个8位2进制输入数据的冒泡排序。

第一种,模仿原题例子中用纯组合逻辑实现;

第二种,假设8位数据是按照时钟节拍串行输入的,要求用时钟触发任务的执行法,每个时钟周期完成一次数据交换操作。

主程序1

modulerank(ra,rb,rc,rd,a,b,c,d);

output[7:

0]ra,rb,rc,rd;

0]a,b,c,d;

0]ra,rb,rc,rd,va,vb,vc,vd,tmp;

regi;

always@(aorborcord)

{va,vb,vc,vd}={a,b,c,d};

repeat(7)

exchange(va,vb);

exchange(vb,vc);

exchange(vc,vd);

{ra,rb,rc,rd}={va,vb,vc,vd};

taskexchange;

inout[7:

0]x,y;

0]tmp;

if(x>

y)

tmp=x;

x=y;

y=tmp;

endtask

测试部分1

main7.v"

moduletask_Top;

wire[7:

b=0;

c=0;

d=0;

repeat(50)

#100a={$random}%255;

b={$random}%255;

c={$random}%255;

d={$random}%255;

rankrank(.ra(ra),.rb(rb),.rc(rc),.rd(rd),.a(a),.b(b),.c(c),.d(d));

主程序2

modulerank(a,rst,clk,ra,rb,rc,rd);

inputclk,rst;

0]va,vb,vc,vd;

0]i;

always@(posedgeclkornegedgeclk)

rst)

va=0;

vb=0;

vc=0;

vd=0;

i=0;

if(i<

8)

i=i+1;

va=a;

end

测试部分2

main7_other.v"

regclk,rst;

rst=0;

#50rst=1;

#100a={8{$random}};

always#100clk=~clk;

rankrank(.a(a),.rst(rst),.clk(clk),.ra(ra),.rb(rb),.rc(rc),.rd(rd));

实验八利用有限状态机进行时序逻辑的设计

设计一个串行数据检测器。

要求连续四个或四个以上为1时输出1,其他输入情况下为0.

moduleseqdet(x,z,clk,rst,state);

inputx,clk,rst;

outputz;

output[2:

0]state;

wirez;

parameterIDLE='

d0,A='

d1,B='

d2,C='

d3,D='

d4;

assignz=(state==D&

&

x==1)?

state<

=IDLE;

casex(state)

IDLE:

if(x==1)

=A;

A:

=B;

B:

=C;

C:

=D;

D:

state=IDLE;

endmodule

测试代码

main8.v"

moduleseqdet_Top;

reg[23:

0]data;

wire[2:

wirez,x;

assignx=data[23];

always#10clk=~clk;

data={data[22:

0],data[23]};

rst=1;

#2rst=0;

#30rst=1;

data='

b1001_1111_0111_1110;

#500$stop;

seqdetm(x,z,clk,rst,state);

实验九楼梯灯

楼下到楼上依次有3个感应灯:

灯1、灯2、灯3。

当行人上下楼梯时,各个灯感应到后自动点亮,若在8s内感应信号消失,则点亮8s,若感应信号存在时间超过8s,则感应信号消失4s后灯自动关闭。

任务1:

做出如上逻辑电路设计并仿真;

任务2:

考虑去抖情况,对于感应信号到达存在毛刺(小于0.5s),设计合适逻辑并剔出。

任务3:

若为节约能源,下一个灯点亮的同时将自动关闭上一个灯,做出如上逻辑设计并仿真(仅考虑一个人的情况)

modulelight_All(clk10,rst,switch,light);

inputclk10,rst;

0]switch;

0]light;

0]state1,state2,state3;

0]count1,count2,count3;

0]count_1,count_2,count_3;

parameter

state1_start=3'

b000,state2_start=3'

b000,state3_start=3'

b000,

state1_work=3'

b001,state2_work=3'

b001,state3_work=3'

b001,

state1_up=3'

b010,state2_up=3'

b010,state3_up=3'

b010,

state1_down=3'

b011,state2_down=3'

b011,state3_down=3'

b011,

state1_other=3'

b100,state2_other=3'

b100,state3_other=3'

b100;

always@(posedgeclk10)

state1<

=state1_start;

count1<

=8'

b0;

count_1<

=3'

if(switch[0]=='

b1&

count_1<

4)

=count_1+1;

case(state1)

state1_start:

b1)

=state1_up;

=

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 北航 电子 电路设计 数字 部分 实验 报告

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《雷雨》中的蘩漪人物形象分析 1.docx

《雷雨》中的蘩漪人物形象分析 1.docx