哈工大2011年数电期末试题+答案.doc

哈工大2011年数电期末试题+答案.doc

- 文档编号:1642852

- 上传时间:2022-10-23

- 格式:DOC

- 页数:10

- 大小:2.75MB

哈工大2011年数电期末试题+答案.doc

《哈工大2011年数电期末试题+答案.doc》由会员分享,可在线阅读,更多相关《哈工大2011年数电期末试题+答案.doc(10页珍藏版)》请在冰豆网上搜索。

试题:

班号:

姓名:

本题得分

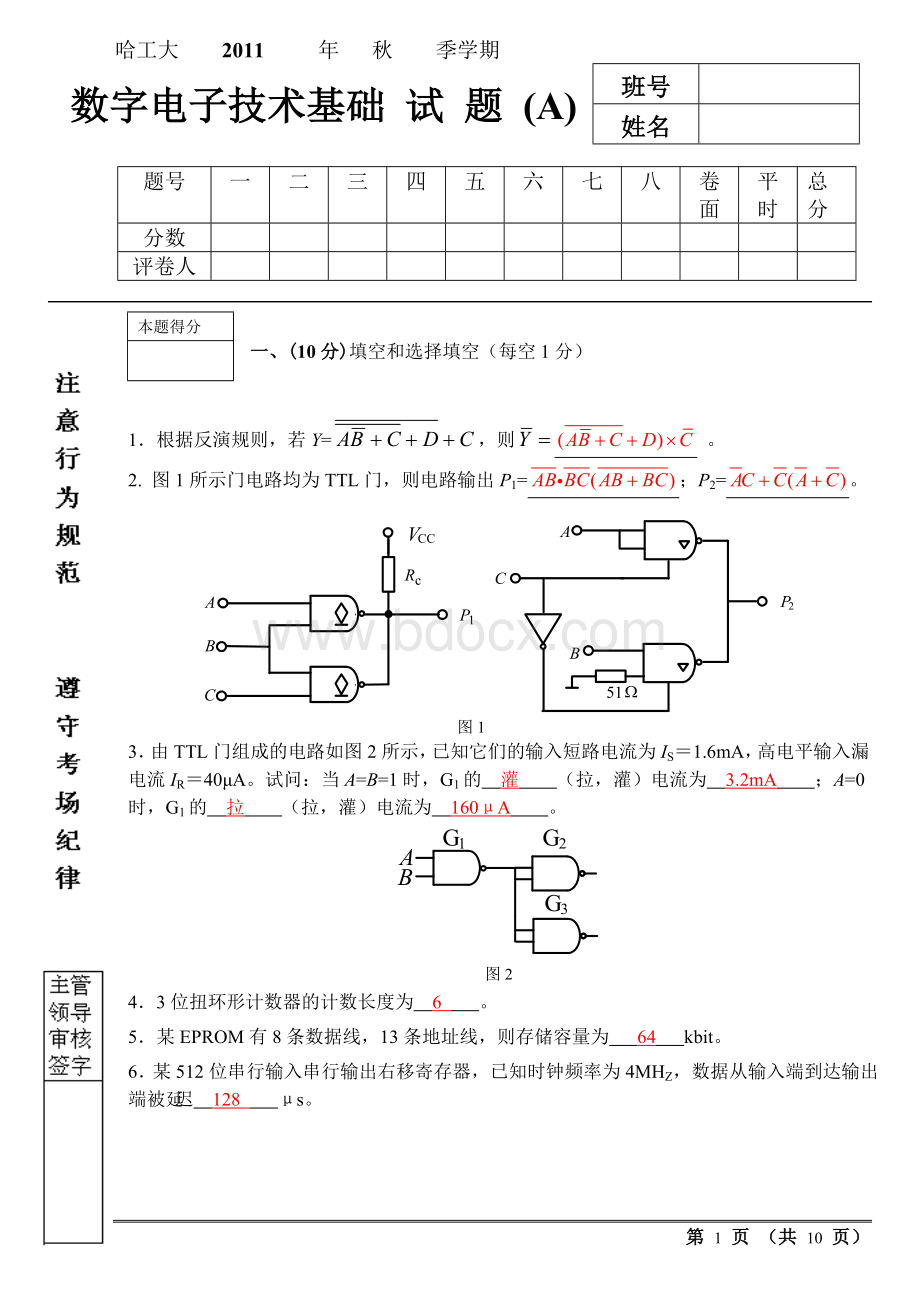

一、(10分)填空和选择填空(每空1分)

1.根据反演规则,若Y=,则。

2.图1所示门电路均为TTL门,则电路输出P1=;P2=。

图1

3.由TTL门组成的电路如图2所示,已知它们的输入短路电流为IS=1.6mA,高电平输入漏电流IR=40μA。

试问:

当A=B=1时,G1的灌(拉,灌)电流为3.2mA;A=0时,G1的拉(拉,灌)电流为160μA。

图2

4.3位扭环形计数器的计数长度为6。

5.某EPROM有8条数据线,13条地址线,则存储容量为64kbit。

6.某512位串行输入串行输出右移寄存器,已知时钟频率为4MHZ,数据从输入端到达输出端被延迟128μs。

本题得分

二、(6分)F(A,B,C,D)=,用两片74LS138和最少的二输入与门实现F。

图3

解:

本题得分

三、(6分)已知图4中AD7524为8位D/A转换器,当D6=1,其它各位均为“0”时,UO=-1V。

74LS90为2/5分频异步加法计数器,时钟CP的频率为10kHz。

1.74LS90构成几进制计数器;

2.计算|UO|的最大值及其频率;

图4

解:

1.5进制;

2.;

本题得分

四、(6分)根据下面二段VerilogHDL语言的描述,说明所描述电路的逻辑功能。

moduletest1(a,b,s,y);

inputa,b;

inputs;

outputy;

assigny=(s==0)?

a:

b;

endmodule

moduletest2(clk,clr,out);

inputclk,clr;

output[3:

0]out;

reg[3:

0]out;

always@(posedgeclkornegedgeclr)

begin

if(!

clr)out<=4'h0;

else

begin

out<=(out>>1);

out[3]<=~out[0];

end

end

endmodule

解:

test1:

2选1数据选择器;

test2:

扭环型计数器。

本题得分

五、(14分)电路如图5所示,时钟脉冲CP的频率为12kHz。

(1)画出74LS161构成电路的完整状态转换图;

(2)分析由触发器FF1、FF2构成的计数器,画出完整的状态转换图、说明为几进制

计数器;

(3)指出Qd、Q2的频率和占空比。

(4)CP频率不变,使Qd的频率降为现在的,应如何改变74LS161的接线?

(不允许增加器件。

)

图5

解:

1.74LS161构成6进制计数器,电路的状态转换表为:

CP

D

C

B

A

0

0

0

0

0

1

0

1

1

0

2

0

1

1

1

3

1

0

0

0

4

1

1

1

0

5

1

1

1

1

6

0

0

0

0

完整的状态转换图如图为:

2.驱动方程:

状态方程:

状态转换表:

状态转换图:

CP

Q2Q1

0

00

1

11

2

10

3

00

0

01

1

00

3.

4.欲使的频率降为现在的,应使74LS161变为十二进制计数器。

改变74LS161的连线,如图所示:

十二进制计数器的状态转换表如表所示:

CP

D

C

B

A

0

0

0

0

0

1

0

0

1

0

2

0

0

1

1

3

0

1

0

0

4

0

1

1

0

5

0

1

1

1

6

1

0

0

0

7

1

0

1

0

8

1

0

1

1

9

1

1

0

0

10

1

1

1

0

11

1

1

1

1

12

0

0

0

0

本题得分

六、(10分)由555定时器构成的电路如图6所示,设输出高电平为5V,输出低电平为0V;VD为理想二极管。

试问:

1.当开关S断开时,两个555定时器各构成什么电路?

计算输出信号uo1、uo2的频

率f1和f2。

2.当开关S闭合时,定性画出uo1、uo2的波形。

3.电容C2和C5的作用分别是什么?

图6

解:

1.多谐振荡器。

2.当开关S闭合时,振荡器2的工作状态受控于振荡器1的输出。

uo1为高电平,VD截止,振荡器2工作,uo1为低电平,VD导通,振荡器2停振,uo2输出高电平。

3电容C2的作用是定时,C5的作用是滤波,滤除高频干扰。

本题得分

七、(10分)图7(a)中,,,

1.写出P的逻辑函数表达式。

2.在图7(b)中可外接必要的非门实现图7(a)所示电路(输入A、B、C、D,

输出P)。

图7(a) 图7(b)

解:

本题得分

八、(8分)用ROM和两个D触发器设计能够进行加法计数和减法计数的二进制同步可逆计数器。

当输入X=0时,进行加法计数;当X=1时,进行减法计数。

输出Y为进位/借位信号。

当计数器加法计数加到11,进位信号输出正脉冲,当计数器

减法计数减到00,借位信号输出正脉冲。

工作时序图如图8(a)所示,假设Q2Q1初

始状态为00。

1)完整填写表1中的内容。

2)求状态方程和输出方程。

3)在图8(b)中完成电路设计,不允许使用D触发器的端。

(只需在图中连线,不允许增加其它的门电路)。

图8(a)

表1可逆计数器的真值表

X

Y

图8(b)

解:

1

X

Y

000

010

001

100

010

110

011

001

100

111

101

000

110

010

111

100

2

3

第10页(共10页)

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 哈工大 2011 年数电 期末 试题 答案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

第2章外币会计(含前言).ppt

第2章外币会计(含前言).ppt