ESD中资料Word下载.docx

ESD中资料Word下载.docx

- 文档编号:16423602

- 上传时间:2022-11-23

- 格式:DOCX

- 页数:19

- 大小:2.20MB

ESD中资料Word下载.docx

《ESD中资料Word下载.docx》由会员分享,可在线阅读,更多相关《ESD中资料Word下载.docx(19页珍藏版)》请在冰豆网上搜索。

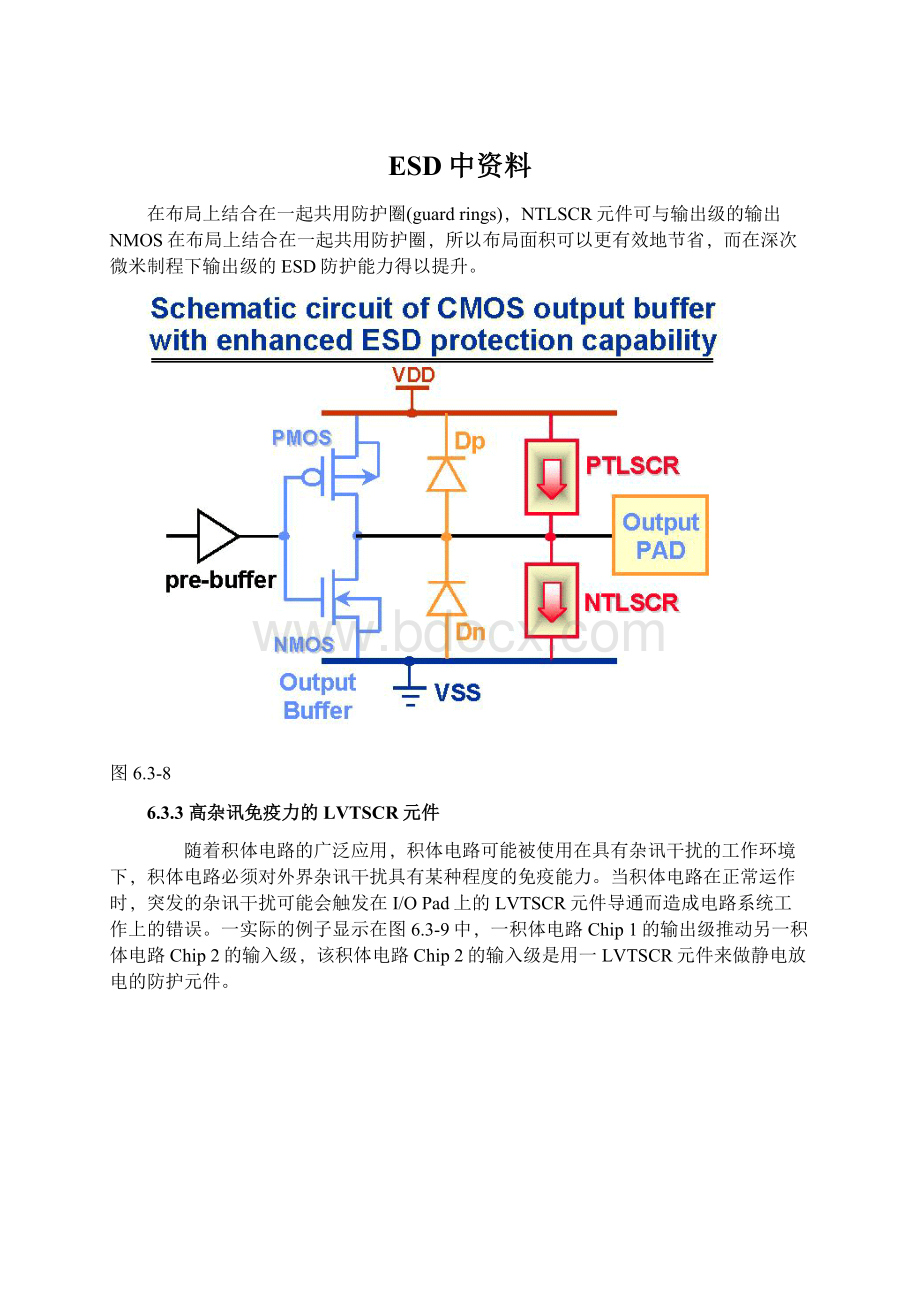

在电路系统的电磁干扰(EMC)测试下﹐经常会产生过高的电压脉冲耦合到该电路系统中各积体电路的输出或输入脚位上﹐若该输出或输入脚位是使用LVTSCR元件当作静电放电的防护元件﹐便会有上述电路系统操作错误的现象发生﹐在某些应用LVTSCR元件当作静电放电防护元件的积体电路产品已经被证实有系统操作错误的问题。

这导致原本在静电放电防护上极被看好的LVTSCR元件在实际电路系统应用上﹐反而不能被安全地采用。

类似的杂讯干扰情形亦显示于图6.3-10的左图中﹐一积体电路Chip3的输出级是用一LVTSCR元件来做静电放电的防护元件﹐该积体电路Chip3的输出级送出一Logic1的讯号至外界负载﹐此时若一过高的电压脉冲恰巧出现而耦合到该输出级的OutputPad﹐这过高的电压脉冲便会意外地触发导通在OutputPad上的LVTSCR元件﹐因此在该输出级OutputPad上的电路状态变会转变成Logic0的讯号﹐造成电路系统操作错误的发生。

PMOS元件的I-V曲线在图6.3-10的漏电路径上即成为LVTSCR元件的负载﹐其电性上的关系如图6.3-10中的右图所示﹐两曲线的交叉点即是漏电电流的大小。

图6.3-10

在图6.3-10中所产生的漏电电流(IL)大小跟积体电路Chip3输出级内的PMOS元件尺寸有关﹐积体电路输出级为了能快速推动外界负载﹐经常设计有大尺寸的输出级元件﹐因此相对引起的漏电电流可达数百mA之谱﹐这造成电路系统上严重的电能漏损问题。

为了避免当静电放电防护用的LVTSCR元件在电路系统杂讯干扰下意外地被导通﹐该LVTSCR元件必需对杂讯干扰具备一定程度的免疫能力﹐如此该LVTSCR元件才能够被安全地应用在积体电路内。

为达到这个目的﹐已有两种解决之道如图6.3-11所示﹐一是提升该LVTSCR元件的触发电流到约200mA左右﹐另一是提升该LVTSCR元件的握住电压(holdingvoltage)比电路系统的VDD电位来得高。

在接下来的文章中将介绍此类具有高杂讯免疫力的LVTSCR元件。

图6.3-11

在图6.3-12中显示了一高电流低电压NMOS触发之横向

硅控整流器(high-currentNMOS-triggerlateralSCR)元件结构图﹐叫做HINTSCR元件。

图6.3-12

在图6.3-13中显示了一高电流低电压PMOS触发之横向硅控整流器(high-currentPMOS-triggerlateralSCR)元件结构图﹐叫做HIPTSCR元件。

这两个元件可以与积体电路的输出级PMOS元件与NMOS元件合并在布局中以提升该输出级的静电放电防护能力﹐其应用在积体电路输出级的等效电路图显示于图6.3-14中﹐而其相对应之实际布局图显示于图6.3-15中。

图6.3-13

图6.3-14

图6.3-15

该HINTSCR元件系利用一旁通二极体Dp2埋入一N型的LVTSCR元件中而成﹐该HIPTSCR元件系利用一旁通二极体Dn2埋入一P型的LVTSCR元件中而成。

此特别埋入的二极体会分流掉一部份的触发电流﹐因此该HINTSCR元件与HIPTSCR元件必须要有更大的外界触发电流才会被触发导通﹐改变二极体在该HINTSCR元件与HIPTSCR元件结构内的面积大小即可设计出不同触发电流的HINTSCR元件与HIPTSCR元件。

该HINTSCR元件与HIPTSCR元件在一0.6微米的CMOS制程中已被实际制作出来﹐其I-V特性曲线分别显示于图6.3-16与图6.3-17中。

图6.3-16

图6.3-17

在图6.3-16中﹐该HINTSCR元件具有两个触发点﹐第一触发点是因其内建之NMOS元件崩溃导通所致﹐因该HINTSCR元件内具有一旁通二极体Dp2流掉一部份的触发电流﹐因此该HINTSCR元件并不会马上进入握住区域(holdingregion)﹐当外界所加的触发电流大于第二触发点电流时﹐该HINTSCR元件便会完全导通而进入握住区域(holdingregion)﹐此HINTSCR元件之握住区域与前述之LVTSCR元件之握住区域完全相同﹐因此该HINTSCR元件的静电放电防护能力与前述之LVTSCR元件相同﹐但该HINTSCR元件却具有极高的杂讯干扰免疫能力。

由图6.3-16中可知﹐该HINTSCR元件的第二触发点电流高达218.5mA﹐具有如此高的第二触发点电流﹐该HINTSCR元件对过高电压脉冲的免疫能力大于VDD+12V﹐即一过高电压脉冲具有一电压位准比VDD高12V也不会触发导通该HINTSCR元件。

相类似地﹐由图6.3-17中可知﹐该HIPTSCR元件的第二触发点电流高达-225.5mA﹐因此该HIPTSCR元件亦具有极高的杂讯干扰免疫能力。

由于SCR元件对温度变化具有敏感性﹐因此该HINTSCR元件在不同温度下的第二触发点电流与电压特性亦被测量显示于图6.3-18中﹐当温度上升到150℃时﹐该HINTSCR元件的第二触发点电流亦高达170mA左右﹐因此在高温状况下该HINTSCR元件仍具有高的杂讯干扰免疫能力。

有关上述各种SCR元件的触发点电压电流比较表显示于表6.3-2中﹐其中该HINTSCR与HIPTSCR元件具有高达200mA以上的触发电流﹐但也具有仅约10V左右的触发电压﹐因此该HINTSCR与HIPTSCR元件能够提供积体电路有效的静电放电防护能力﹐亦对杂讯干扰具备一定程度的免疫能力﹐这使得HINTSCR与HIPTSCR元件能够被安全地应用在积体电路的静电放电防护电路上。

图6.3-18

Devices

LSCR

MLSCR

LVTSCR

HIPTSCR/HINTSCR

Characteristics

TriggerVoltage

~50V

~25V

~10V

TriggerCurrent

~10mA

~200mA

NoiseMargin

?

~+/-3V

~+/-12V

表6.3-2

另一种设计是把该LVTSCR元件的握住电压(holdingvoltage)提升至比电路系统的VDD电位来得高﹐成为一高握住电压硅控整流器(high-holding-voltageSCR)元件﹐但其触发点(triggerpoint)电压电流仍保持跟先前所述的LVTSCR元件一样低﹐如图6.3-11之右图所示。

由于此高握住电压硅控整流器的握住电压比VDD电位来得高﹐即使该硅控整流器被杂讯干扰而导通﹐但在杂讯干扰暂态消失之后﹐因电路系统的VDD电位无法支持该硅控整流器维持在导通状态﹐该硅控整流器便会自动关闭﹐因此不会造成电路系统的错误操作或漏电电流产生。

但在一般的(bulk)CMOS制程技术下﹐要使一SCR元件的握住电压比VDD电位来得高并不容易﹐需要利用到防止CMOS积体电路锁住效应(latchup)的防护圈以及较宽大的布局间隔﹐如此虽可提升该SCR元件的握住电压﹐但该SCR元件变得很难被导通﹐将无法即时导通来排放静电放电发生时的瞬间大电流﹐这将导致需要被保护的元件会先被静电放电所破坏。

但在磊晶沉积(eptiaxialsubstrate)的晶片上﹐其基体(substrate)阻值被大幅降低以防止CMOS积体电路锁住效应的发生﹐在这种磊晶沉积的晶片上﹐要单纯地提升一SCR元件的握住电压就容易多了。

图6.3-19中显示一LVTSCR元件在磊晶沉积的晶片上因不同的布局间距"

S"

所导致的不同握住电压关系图﹐当布局间距"

增加时该LVTSCR元件的握住电压亦相对增加﹐然而该LVTSCR元件的静电放电耐受能力随着握住电压的增加却反而降低﹐盖因LVTSCR元件的握住电压增加将使得静电放电电流流过该LVTSCR元件时﹐在该LVTSCR元件上产生更大的电能(power)消耗﹐这导致更多的放电热能必须由该LVTSCR元件来承受﹐也因此一LVTSCR元件的握住电压相对增加时﹐其静电放电耐受能力却反而降低。

图6.3-19

在图6.3-19中﹐一适当的布局间距"

(约3-4微米)可以提升该LVTSCR元件的握住电压但不致降低该LVTSCR元件的静电放电耐受能力﹐这适当的布局间距"

在不同的磊晶沉积晶片的CMOS制程中亦会不同﹐因此要有事先的实验调查才能找出最佳的布局间距"

。

6.4电路上(CircuitLevel)的改进方法

本节介绍利用电路上的技巧来提升CMOSIC的ESD防护能力﹐其主要是利用ESD放电的瞬间电压快速变化的特性﹐藉由电容耦合(coupling)作用来使ESD防护电路或元件达到更有效率的防护动作。

6.4.1闸极耦合(Gate-Couple)技术

在次微米或深次微米制程下﹐元件的ESD防护能力下降﹐为提升CMOSIC的ESD防护能力﹐在输入/输出PAD的ESD防护用元件或输出级电晶体元件都会被做得较大﹐以期利用大尺寸的元件设计来提升ESD防护能力。

大尺寸的元件在布局上经常画成手指状(finger-type)﹐例如一个NMOS元件其W/L=1000/0.6﹐则会在布局上画成10支finger﹐彼此互相并联在一起。

但是﹐在ESD放电发生时﹐这10支finger并不一定会同时导通(一般是因Breakdown而导通)﹐常见到只有2-3支finger会先导通﹐这是因布局上无法使每finger的相对位置及拉线方向完全相同所致﹐这2~3支finger一导通﹐ESD电流便集中流向这2~3支的finger﹐而其他的finger仍是保持关闭的﹐所以其ESD防护能力等效于只有2~3支finger(约300/0.6)的防护能力﹐而非10支finger的防护能力。

这也就是为何元件尺寸已经做得很大﹐但ESD防护能力并未如预期般地上升的主要原因。

为克服大尺寸电晶体在ESD放电情下﹐不均匀导通的情况﹐图6.4-1显示了利用电容耦合作用来使大尺寸电晶体的每一finger能均匀地导通的设计。

图6.4-1(a)的设计是美国德州仪器(TI)公司在1992年所报导的设计﹐该设计利用NMOS的杂散Cgd电容做耦合元件﹐那个field-oxidedevice加强了耦合电容的效用﹐当有正的ESD电压突然出现在PAD上时﹐此瞬间的电压变化会导致NMOS闸极电压跟着上升﹐由于电容耦合作用之故。

因NMOS的闸极上有耦合的正电压﹐故大尺寸NMOS元件的finger会被一起导通而进入骤回崩溃区(snapbackregion)﹐由于大尺寸输出元件NMOS的每一finger能够均匀导通﹐ESD放电能量便可均匀分散到每一finger来承受﹐因此其ESD防护能力才能够被有效地提升﹐真正发挥大尺寸电晶体元件应有的ESD防护水准。

图6.4-1(a)

图6.4-1(b)

因此﹐闸极耦合技术就是用来促使大尺寸电晶体在ESD放电下能够均匀导通来旁通ESD电流的一个有效方法。

图6.4-1(b)是此电容耦合技术应用于输入级ESD防护电路上的一种安排﹐GCNMOS(Gate-CoupleNMOS)是ESD电流旁通用的元件﹐具有大的尺寸。

因应用在输入端﹐故其闸极需经由一电阻Rg(~10KΩ)接地﹐以使该GCNMOS在CMOSIC正当工作时是关闭的。

另有一NMOS连接成电容状Cc﹐此NMOS乃被用来加强电容耦合作用﹐当有正的ESD电压在输入PAD上发生时﹐一部份的正电压会经由Cd与Cc耦合到GCNMOS的闸极﹐此闸极电压会经由Rg放电到地去﹐Rg的大小会影响闸极电压的维持(Holding)时间。

GCNMOS因而可以达到均匀导通的目的﹐以提升其ESD防护能力。

6.4.2互补式的闸极耦合静电放电防护电路

在第三章中已强调过﹐在任一I/OPin上的ESD放电有四种测试组合﹐所以ESD防护设计必需要考虑这四种测试组合的ESD放电路径﹐以免引起内部电路损伤的问题。

图6.4-2显示了互补式闸极耦合静电放电防护电路﹐在此电路中﹐除了闸极耦合的NMOS之外﹐另有一闸极耦合的PMOS﹐其在四种放电测试组合下的工作原理请参见图6.4-3。

图6.4-2

图6.4-3

在这电路中提供了四种不同的放电路径来有效旁通ESD电流﹐ND-modeESD放电是利用闸极耦合PMOS元件来旁通ESD电流﹐PS-modeESD放电是利用闸极耦合NMOS元件来旁通ESD电流。

选择合适的Cn(Cp)与Rn(Rp)﹐此电路能够提供有效的ESD防护而不影响该CMOSIC的正常工作。

图6.4-4显示此电路的实现技巧﹐该耦合电容可以利用PAD与其下方Poly层的寄生电容来做﹐这可以不用占用额外的布局面积来实现这个电路。

其实际布局方式请参见图6.4-5。

图6.4-4

图6.4-5

6.4.3闸极耦合互补式LVTSCR静电放电防护电路

图6.4-6显示了CMOS制程在深次微米低电压下的输入级及传统的输入级ESD防护电路﹐在低电压制程下﹐PMOS及NMOS的GateOxide越来越薄﹐例如﹐在0.25μm的CMOS制程技术下﹐Gate-Oxide厚度只剩50A左右﹐如此薄的GateOxide很容易便会被ESD所破坏。

然而在传统的输入级ESD防护电路设计上﹐常用一shortchannel的NMOS元件做第二级保护﹐利用此NMOS的drainbreakdown电压来箝制gate-oxide上的ESD电压。

但是随着低电压制程的演进﹐gate-oxidebreakdown电压与drainbreakdown电压越来越接近﹐甚至可能低于drainbreakdown电压﹐这时传统的ESD防护设计便无法有效地保护这种愈来愈薄的GateOxide。

因此一种结合前述LVTSCR元件与电容闸极耦合技术的静电放电电路设计便被发展出来。

图6.4-6

结合图6.3-3与图6.4-2的设计﹐可得图6.4-7。

在图6.4-7中﹐有一Gate-CoupledPTLSCR安排于PAD与VDD之间﹐有一Gate-CoupledNTLSCR安排于PAD与VSS之间。

在LVTSCR元件介绍时已说明LVTSCR元件的导通电压已下降到NMOS(或PMOS)元件的drainbreakdown电压﹐但此drainbreakdown电压在深次微米低电压制程下﹐仍可能极接近(甚至大于)Gate-Oxidebreakdown电压﹐为使LVTSCR元件的导通电压能够再下降﹐利用Gate-Couple技术即可达成。

当正的ESD电压发生在PAD上时﹐Cn会耦合正电压到Mn1的闸极﹐因此Mn1便会被导通﹐该被导通的Mn1会进一步触发NTLSCR元件的导通﹐当NTLSCR元件一被导通﹐其低的HoldingVoltage即可有效地箝制ESD电压而得以保护输入级内部的薄闸极氧化层。

相同地在ND-modeESD放电情形下﹐PTLSCR元件便会因Mp1的导通而触发导通来保护内部的薄闸极氧化层。

因此﹐闸极耦合NTLSCR与PTLSCR元件的等效导通电压可以更被降低﹐且此导通电压可藉由Cn(Cp)与Mn1(Mp1)的耦合作用来控制﹐也就是说可以做到可调性(tunable)的设计。

图6.4-7

因此在深次微米低电压的制程下﹐不需利用额外的制程处理﹐其ESD防护能力仍可藉由图6.4-7的设计而大幅提升。

当制程技术进步到深次微米的地步﹐前述的磊晶沉积晶片将已大幅地被采用﹐且由于低电压的工作需求﹐电路的VDD电压亦下降至仅约2.5V或1.8V而已﹐因此NTLSCR与PTLSCR元件的HoldingVoltage可以很容易地利用适当的布局间距而稍大于VDD电位﹐因此闸极耦合NTLSCR与PTLSCR元件在深次微米低电压的制程下﹐可是安全地用来保护积体电路产品避免静电放电的破坏。

图6.4-8显示图6.4-7电路的元件剖面设计图﹐该耦合电容Cn与Cp可利用PAD与Poly的寄生电容来达成﹐在布局上改变这两层重叠的面积即可调整耦合电容的大小﹐其实际实施布局图参见图6.4-9。

图6.4-8

图6.4-9

在图6.4-9中的Rp与Rn是利用Poly电阻来做﹐但在深次微米制程下﹐Poly层已大多用Ploycide﹐其具有更低的阻值﹐在这种制程下﹐大阻值(~KΩ)的Rp与Rn若用Polycide的Polylayer来拉﹐会占用很大的布局面积﹐此时可用小尺寸的PMOS或NMOS来达成Rp与Rn的相同功能。

这种适合用在有Polycide或Salicide制程的闸极耦合互补式LVTSCR静电放电防护电路显示于图6.4-10中。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- ESD 资料

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx