跨时钟域信号同步的IP解决方案snps资料下载.pdf

跨时钟域信号同步的IP解决方案snps资料下载.pdf

- 文档编号:16125365

- 上传时间:2022-11-20

- 格式:PDF

- 页数:27

- 大小:1.01MB

跨时钟域信号同步的IP解决方案snps资料下载.pdf

《跨时钟域信号同步的IP解决方案snps资料下载.pdf》由会员分享,可在线阅读,更多相关《跨时钟域信号同步的IP解决方案snps资料下载.pdf(27页珍藏版)》请在冰豆网上搜索。

这些主题和解决方案包括:

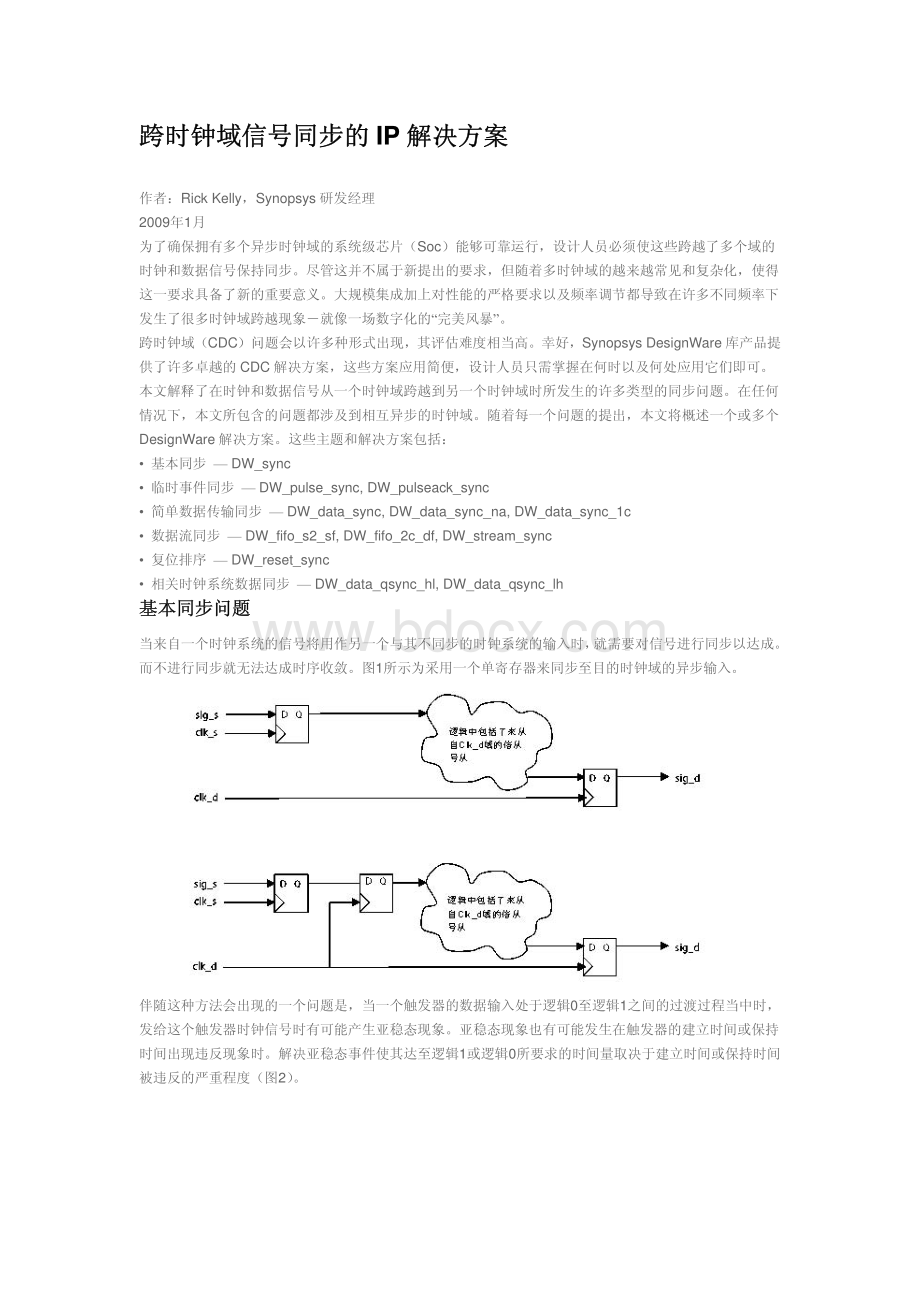

基本同步DW_sync临时事件同步DW_pulse_sync,DW_pulseack_sync简单数据传输同步DW_data_sync,DW_data_sync_na,DW_data_sync_1c数据流同步DW_fifo_s2_sf,DW_fifo_2c_df,DW_stream_sync复位排序DW_reset_sync相关时钟系统数据同步DW_data_qsync_hl,DW_data_qsync_lh基本同步问题基本同步问题当来自一个时钟系统的信号将用作另一个与其不同步的时钟系统的输入时,就需要对信号进行同步以达成。

而不进行同步就无法达成时序收敛。

图1所示为采用一个单寄存器来同步至目的时钟域的异步输入。

伴随这种方法会出现的一个问题是,当一个触发器的数据输入处于逻辑0至逻辑1之间的过渡过程当中时,发给这个触发器时钟信号时有可能产生亚稳态现象。

亚稳态现象也有可能发生在触发器的建立时间或保持时间出现违反现象时。

解决亚稳态事件使其达至逻辑1或逻辑0所要求的时间量取决于建立时间或保持时间被违反的严重程度(图2)。

ClocktoQdelay时钟至Q延迟FFMinimumspecs触发器最小规格图图2解决亚稳态事件所用时间解决亚稳态事件所用时间当亚稳态事件持续时间长至足以影响到下一个逻辑阶段时,同步器就发生了故障。

故障间平均时间(MTBF)通常计算如下:

其中:

fclk是采样时钟频率fdata是数据变化频率tres是解决亚稳态所允许占用的时间T0和T1是与具体触发器相关的常数(下文将进一步叙述)通常,由于在综合时会尝试在时序能够满足的条件下缩减门电路数以节省占用面积,所以设计人员无法控制至下一阶段间的时间预算。

为了保持稳定一致的解决用时,设计人员可以采用一个2个触发器组成的序列。

但是,这种传统解决方案肯定会增加时延。

在采用2个触发器的解决方案,时钟树就以减去触发器FF1的时钟至Q延时后的时钟周期以及FF2的建立时间要求为基础。

对于有着相对较高数据传输速率的高速应用来说,即使两级同步器也有可能无法获得足够的MTBF,特别是在FPGA实现方案中。

如果加入第3级,则只有在第1级在亚稳态保持了足够长的时间,导致侵占了FF2的建立时间的情况下,第2级才有可能发生亚稳态事件(图3)。

图图33级同步器级同步器SampeMTBFtestMTBF测试电路示例ErrorCounter错误计数器采用这一方法,MTBF可计算为:

T0和T1常数与所选用的具体触发器相关,并有可能从库供应商处获得。

库供应商会采用如图4所示的电路来测定这些常数。

错误计数器用于测量在输入时钟处于某一特定组合的输入频率下的MTBF。

通过在不同频率比率下让此电路运行,就可以测定T0和T1的数值。

图图4用于测定触发器常数的电路用于测定触发器常数的电路参见以下资料,可以了解更多有关亚稳态和MTBF计算的信息:

“确保亚稳态不会破坏您的数字设计方案”,作者:

DeboraGrosse,Unisys,EDN,1994http:

/TransactionsonComputers,ol.C-36,No.1,Jan.,1987Google:

MTBF亚稳态同步另一个基本同步问题涉及到扫描测试。

扫描链经常采用保持锁存以确保在时钟域之间实现正确的扫描切换。

如果在扫描测试排序时,让最后一个扫描输入循环后面直接跟一个捕获循环,且让两者的时钟均由测试时钟来驱动,则有可能无法正确捕获到跨越时钟域的功能信号(图5)。

在源侧域之间插入一个锁存器能够提供1/2时钟周期的延迟,确保了扫描测试期间的正确捕获操作,从而解决了这个问题。

在不处于扫描模式时,可由一个复用器将这个锁存器旁路,实现正常功能运行。

另一种解决方案是在较小型的时钟域之间插入一个负边沿触发器。

图图5a扫描测试中不受控制的偏移有可能导致跨域捕获发生违反扫描测试中不受控制的偏移有可能导致跨域捕获发生违反图图5b在域之间复用一个锁存器可以确保在域之间复用一个锁存器可以确保1/2时钟周期的保持时钟周期的保持图图5c一个负边沿一个负边沿D触发器也可保持触发器也可保持1/2时钟周期的保持时钟周期的保持图图5跨时钟域扫描测试问题跨时钟域扫描测试问题对于基本同步来说,设计人员可以使用DesignWare的DW_sync组件,此组件有以下参数:

宽度f_sync_type:

级数tst_mode:

0=无保持,1=锁存,2=负边沿触发器verif_en(下文讨论;

不影响综合)在以f_sync_type参数指定了级数后,将获得如图6所示的配置方式之一。

图图6采用采用DW_sync组件时可能的级数组件时可能的级数同步临时事件同步临时事件有些时间,您需要在一个时钟域内设置逻辑电路以告知另一个异步时钟域内的逻辑电路,有某一特定事件已经发生。

一种方法是采用如图7所示的方案,其中通过门选复位来清空源域内的脉冲。

图图7a较差的设计方案较差的设计方案图图7b较好但仍存在门选复位较好但仍存在门选复位图图7c更好的设计方案,但仍不是最佳方案更好的设计方案,但仍不是最佳方案图图7另一个时钟域内事件的通知逻辑另一个时钟域内事件的通知逻辑在使用一个高电平有效的脉冲作为跨时钟域事件的信号时,这个脉冲的宽度必须足以确保采样操作的完成,而且必须在脉冲之间存在明显的无信号时间。

为了避免采用脉冲拉伸机制,您可以使用不归零(NRZ)信号发生方式,而不要使用归零(RZ)信号发生方式。

图8所示为clk_d域是如何在后一种类型的信号下捕获变化的,这是一种在许多状况下难于采用的方法。

Eventinclk_s:

clk_s内的事件Returnto:

Clk_d内捕获的归零信号Capturedin:

在clk-d内捕获的信号图图8NRZ信号发生方式的优点信号发生方式的优点为了简化时钟域之间的脉冲传递,可采用DW_pulse_sync双时钟脉冲同步器(图9)。

标为“clk_s”的虚线框内的逻辑电路运行在clk_s(源)时钟域下,而标为“clk_d”的虚线框内的逻辑电路运行在clk_d(目的)时钟域内。

在域之间采用NRZ信号可以实现更高的事件处理流量,而且由于无需反馈,所要求的逻辑电路也较少。

Register:

可以通过parameter,reg_event在器件外配置寄存器NRZ:

跨域的NRZ信号Multiple:

多寄存器同步器History:

用于检测变化的历史寄存器图图9DW_pulse_sync双时钟脉冲同步器双时钟脉冲同步器Multiple:

多寄存器同步器Multiple:

多寄存器同步器Busystate:

忙碌状态NRZfeedbackack_delay=1:

NRZ反馈ack_delay=1:

Multiple:

图图10加了确认的加了确认的DW_pulseack_sync脉冲同步器脉冲同步器如果需要反馈,则可以采用DW_pulseack_sync,这是一种带有确认的脉冲同步器。

如图10所示,这个IP产品提供了一个NRZ反馈信号,能够比无确认版本提供更高的事件处理流量。

DW_pulseack_sync还提供了可配置的标志寄存器和反馈延时。

同步数据总线同步数据总线在从一个时钟域跨越至另一个时钟域时,在目的时钟对接近过渡状态的总线进行采样时,数据总线上有可能出现瞬时虚假数值(图11)。

例如,一条从11011001变为01011010的8位总线上有3个位发生了改变。

在所涉及的偏移存在时序上不确定性的情况下,就有会看到8个可能出现的数值:

theinitialvalue(11011001),thefinalvalue(01011010)andsixpossibleintermediatevalues(11011000,11011011,11011010,01011001,01011000and01011011).Source:

源总线Destinationclk:

目的时钟1st:

第1个同步寄存器2nd:

第2个同步寄存器Intermediatevalue:

过渡数值Intermediatevalue:

过渡数值图图11瞬时总线数值瞬时总线数值一种在同步数据总线时避免不想要的过渡数值的方法是,采用一个带有确认的临时事件同步器。

这种逻辑可以采用以下次序对跨越时钟边界的数据进行同步交换:

保持数据,发送“请接受”,发回“已接受”,释放数据寄存器。

DW_pulseack_sync组件能够发送必要的“请接受”和“已接受”事件。

而一种带确认信号的数据总线同步器DW_data_sync能更好地完成此项任务。

此IP消除了过渡虚拟数据,而且您可以对其进行配置,提供临时性的数据存储能力(图12)。

Optional:

可选用的临时数据寄存器Handshake:

同步交换逻辑Send:

发送控制图图12带确认的带确认的DW_data_sync总线同步器总线同步器确认延迟问题确认延迟问题在源时钟比目的时钟快得并不多(或根本相同)时,提供一个确认信号的同步器可能会引发时延问题。

如果在应用当中时延具有关键性的意义,则应考虑采用一种“提前”确认方式,即通过设置参数ack_delay=0来进行配置。

如果源时钟比目的时钟快出很多,则可以同步确认信号,而且数据可以在不到目的时钟1个周期内的时间内改变。

在时延并非关键性问题时,最好采用默认的ack_delay=1设置。

如果没有使用延迟,则在本地注释块内记录此项附加说明就是一种很好的处理方式。

以下是使用ack_delay=0的通用规则1:

clk_d的周期不应当超过clk_s*的周期(r_sync_type0.25)clk_s的频率不应当超过clk_d*的频率(f_sync_type0.25)例如,在f_sync_type=r_sync_type=2,Fclk_d=200MHz时MaxFclk_s=Fclk_d*(20.25)MaxFclk_s=200MHz*1.75=350MHz如果确保目的时钟速率超过了(Fclk_s*(f_sync_type+1.25))2,则可以使用更简单的信号同步体系。

在目的时钟较快的情况下,可以对“请接受”事件进行同步,并在不到源域1个时钟周期的时间内捕获数据。

因此,也就不需要发回“已接受”事件了。

在需要最大程度地减少时延和/或不必要的逻辑电路时,例如,在对一个实时时钟寄存器进行更新并将其内容发送到一个高速逻辑区块时,这种方法就较为实用。

为了实现这一方法,可以采用DesignWare的不带确认的数据总线同步器DW_data_sync_na(图13)。

此IP提供了比双向

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 时钟 信号 同步 IP 解决方案 snps

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

保育笔记.doc

保育笔记.doc

幼儿园日常安全检查记录表.xls

幼儿园日常安全检查记录表.xls