Verilog的150个经典设计实例资料下载.pdf

Verilog的150个经典设计实例资料下载.pdf

- 文档编号:16125099

- 上传时间:2022-11-20

- 格式:PDF

- 页数:83

- 大小:148.22KB

Verilog的150个经典设计实例资料下载.pdf

《Verilog的150个经典设计实例资料下载.pdf》由会员分享,可在线阅读,更多相关《Verilog的150个经典设计实例资料下载.pdf(83页珍藏版)》请在冰豆网上搜索。

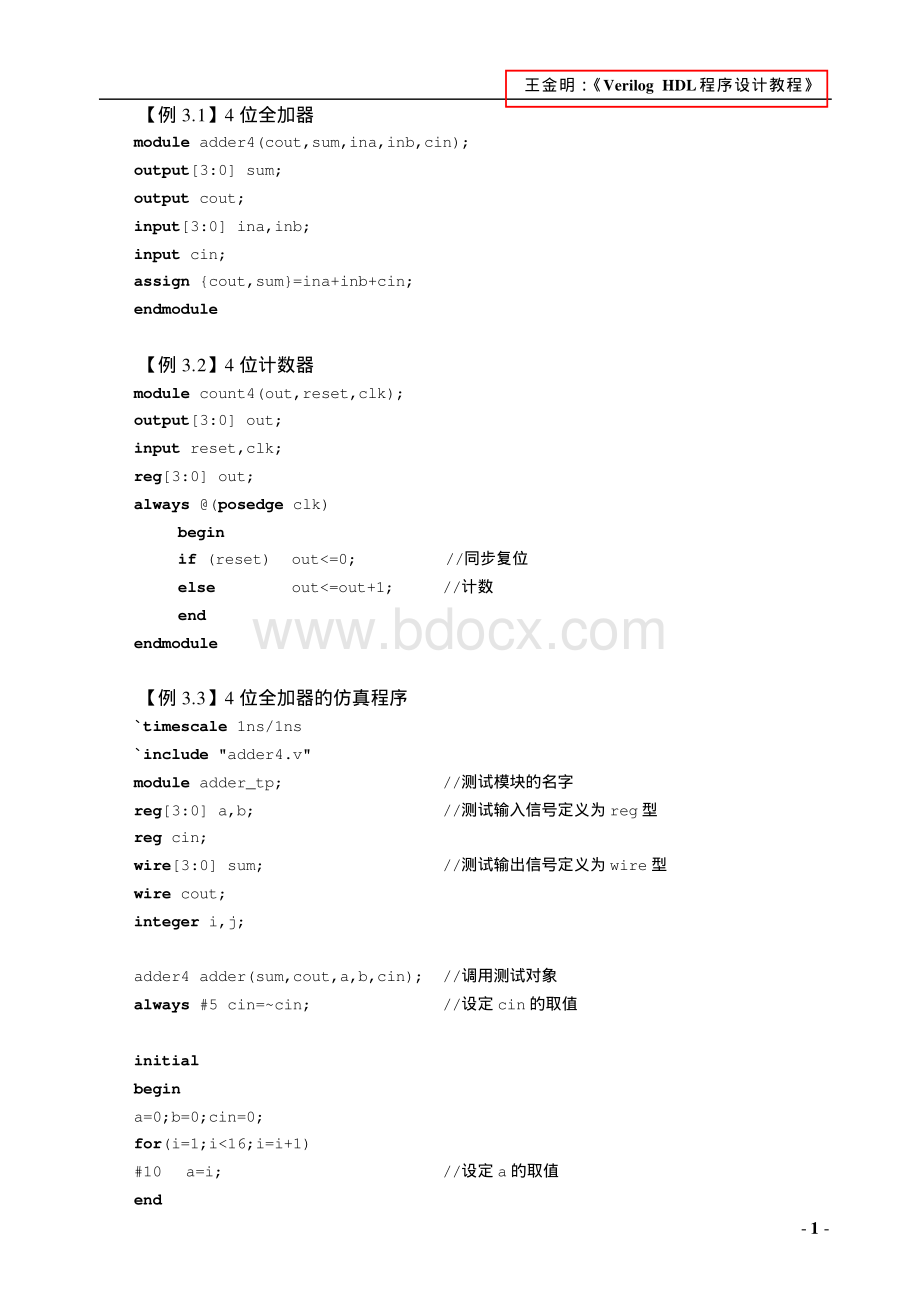

integeri,j;

adder4adder(sum,cout,a,b,cin);

/调用测试对象always#5cin=cin;

/设定cin的取值initialbegina=0;

b=0;

cin=0;

for(i=1;

i16;

i=i+1)#10a=i;

/设定a的取值end程序文本-2-initialbeginfor(j=1;

j16;

j=j+1)#10b=j;

/设定b的取值endinitial/定义结果显示格式begin$monitor($time,%d+%d+%b=%b,%d,a,b,cin,cout,sum);

#160$finish;

endendmodule【例3.4】4位计数器的仿真程序timescale1ns/1nsincludecount4.vmodulecoun4_tp;

regclk,reset;

/测试输入信号定义为reg型wire3:

/测试输出信号定义为wire型parameterDELY=100;

count4mycount(out,reset,clk);

/调用测试对象always#(DELY/2)clk=clk;

/产生时钟波形initialbegin/激励信号定义clk=0;

reset=0;

#DELYreset=1;

#DELYreset=0;

#(DELY*20)$finish;

end/定义结果显示格式initial$monitor($time,clk=%dreset=%dout=%d,clk,reset,out);

endmodule【例3.5】“与-或-非”门电路moduleAOI(A,B,C,D,F);

/模块名为AOI(端口列表A,B,C,D,F)inputA,B,C,D;

/模块的输入端口为A,B,C,DoutputF;

/模块的输出端口为F王金明:

VerilogHDL程序设计教程-3-wireA,B,C,D,F;

/定义信号的数据类型assignF=(A&

B)|(C&

D);

/逻辑功能描述endmodule【例5.1】用case语句描述的4选1数据选择器modulemux4_1(out,in0,in1,in2,in3,sel);

outputout;

inputin0,in1,in2,in3;

input1:

0sel;

regout;

always(in0orin1orin2orin3orsel)/敏感信号列表case(sel)2b00:

out=in0;

2b01:

out=in1;

2b10:

out=in2;

2b11:

out=in3;

default:

out=2bx;

endcaseendmodule【例5.2】同步置数、同步清零的计数器modulecount(out,data,load,reset,clk);

output7:

input7:

0data;

inputload,clk,reset;

reg7:

always(posedgeclk)/clk上升沿触发beginif(!

reset)out=8h00;

/同步清0,低电平有效elseif(load)out=data;

/同步预置elseout=out+1;

/计数endendmodule【例5.3】用always过程语句描述的简单算术逻辑单元defineadd3d0defineminus3d1defineband3d2definebor3d3definebnot3d4程序文本-4-modulealu(out,opcode,a,b);

input2:

0opcode;

/操作码input7:

/操作数always(opcodeoraorb)/电平敏感的always块begincase(opcode)add:

out=a+b;

/加操作minus:

out=a-b;

/减操作band:

out=a&

b;

/求与bor:

out=a|b;

/求或bnot:

out=a;

/求反default:

out=8hx;

/未收到指令时,输出任意态endcaseendendmodule【例5.4】用initial过程语句对测试变量A、B、C赋值timescale1ns/1nsmoduletest;

regA,B,C;

initialbeginA=0;

B=1;

C=0;

#50A=1;

B=0;

#50A=0;

C=1;

#50B=1;

#50B=0;

#50$finish;

endendmodule【例5.5】用begin-end串行块产生信号波形timescale10ns/1nsmodulewave1;

regwave;

parametercycle=10;

initialbegin王金明:

VerilogHDL程序设计教程-5-wave=0;

#(cycle/2)wave=1;

#(cycle/2)wave=0;

#(cycle/2)$finish;

endinitial$monitor($time,wave=%b,wave);

endmodule【例5.6】用fork-join并行块产生信号波形timescale10ns/1nsmodulewave2;

parametercycle=5;

initialforkwave=0;

#(cycle)wave=1;

#(2*cycle)wave=0;

#(3*cycle)wave=1;

#(4*cycle)wave=0;

#(5*cycle)wave=1;

#(6*cycle)$finish;

joininitial$monitor($time,wave=%b,wave);

endmodule【例5.7】持续赋值方式定义的2选1多路选择器moduleMUX21_1(out,a,b,sel);

inputa,b,sel;

assignout=(sel=0)?

a:

/持续赋值,如果sel为0,则out=a;

否则out=bendmodule【例5.8】阻塞赋值方式定义的2选1多路选择器moduleMUX21_2(out,a,b,sel);

程序文本-6-outputout;

always(aorborsel)beginif(sel=0)out=a;

/阻塞赋值elseout=b;

endendmodule【例5.9】非阻塞赋值modulenon_block(c,b,a,clk);

outputc,b;

inputclk,a;

regc,b;

always(posedgeclk)beginb=a;

c=b;

endendmodule【例5.10】阻塞赋值moduleblock(c,b,a,clk);

endendmodule【例5.11】模为60的BCD码加法计数器modulecount60(qout,cout,data,load,cin,reset,clk);

0qout;

inputload,cin,clk,reset;

always(posedgeclk)/clk上升沿时刻计数王金明:

VerilogHDL程序设计教程-7-beginif(reset)qout=0;

/同步复位elseif(load)qout=data;

/同步置数elseif(cin)beginif(qout3:

0=9)/低位是否为9,是则beginqout3:

0=0;

/回0,并判断高位是否为5if(qout7:

4=5)qout7:

4=0;

elseqout7:

4=qout7:

4+1;

/高位不为5,则加1endelse/低位不为9,则加1qout3:

0=qout3:

0+1;

endendassigncout=(qout=8h59)&

cin)?

1:

0;

/产生进位输出信号endmodule【例5.12】BCD码七段数码管显示译码器moduledecode4_7(decodeout,indec);

output6:

0decodeout;

0indec;

reg6:

always(indec)begincase(indec)/用case语句进行译码4d0:

decodeout=7b1111110;

4d1:

decodeout=7b0110000;

4d2:

decodeout=7b1101101;

4d3:

decodeout=7b1111001;

4d4:

decodeout=7b0110011;

4d5:

decodeout=7b1011011;

4d6:

decodeout=7b1011111;

4d7:

decodeout=7b1110000;

4d8:

decodeout=7b1111111;

4d9:

decodeout=7b1111011;

decodeout=7bx;

endcaseend程序文本-8-endmodule【例5.13】用casez描述的数据选择器modulemux_casez(out,a,b,c,d,select);

inputa,b,c,d;

0select;

always(selectoraorborcord)begincasez(select)4b?

4b?

1?

:

out=b;

out=c;

4b1?

out=d;

endcaseendendmodule【例5.14】隐含锁存器举例moduleburied_ff(c,b,a);

outputc;

inputb,a;

regc;

always(aorb)beginif(b=1)&

(a=1)c=a&

endendmodule【例5.15】用for语句描述的七人投票表决器modulevoter7(pass,vote);

outputpass;

input6:

0vote;

reg2:

integeri;

regpass;

always(vote)beginsum=

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- Verilog 150 经典 设计 实例

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

保育笔记.doc

保育笔记.doc

幼儿园日常安全检查记录表.xls

幼儿园日常安全检查记录表.xls