基于FPGA的VGA显示详解附VHDL代码资料下载.pdf

基于FPGA的VGA显示详解附VHDL代码资料下载.pdf

- 文档编号:16086543

- 上传时间:2022-11-19

- 格式:PDF

- 页数:8

- 大小:287.56KB

基于FPGA的VGA显示详解附VHDL代码资料下载.pdf

《基于FPGA的VGA显示详解附VHDL代码资料下载.pdf》由会员分享,可在线阅读,更多相关《基于FPGA的VGA显示详解附VHDL代码资料下载.pdf(8页珍藏版)》请在冰豆网上搜索。

当一行扫描完毕后然后电子枪又转到下一行的这段时间或是扫描完所有的行后电子枪回到第一行的这段时间,这两段时间都要消隐。

在消隐的时间内,数据是无效的。

这样就保证电子枪的回扫的个动作不干扰显示,因为回扫这个动作是很频繁的,若在这个时间段内数据有效,那么就回在显示屏上出现电子枪回扫的轨迹。

消隐的时候我们干什么?

消隐这个动作是显示屏(CRT)执行的,我们在编程时只要注意有这么个东西就行。

同步信号(包括HS和VS)是什么?

这个就相当于一个数据起始信号,表明数据马上就要开始了。

如果撇开具体的设备,那么这个信号和AD、DA中常用的Sync(同步)、CS(片选)信号相当。

该信号一般为负电平,但对于有的显示器可不关心该信号的极性,因为它内部可自动转换正负逻辑。

对于普通的VGA显示器,需要引出5个信号:

R,G,B:

三原色;

HS:

行同步信号;

VS:

场同步信。

对于VGA显示器的上述五个信号的时序驱动要严格遵循“VGA工业标准”,即64048060HZ模式,否则无法显示正确地图象。

VGA工业标准要求的频率:

时钟频率:

25.175MHz(像素输出的频率)行频:

31469Hz(即行信号HS的频率)场频:

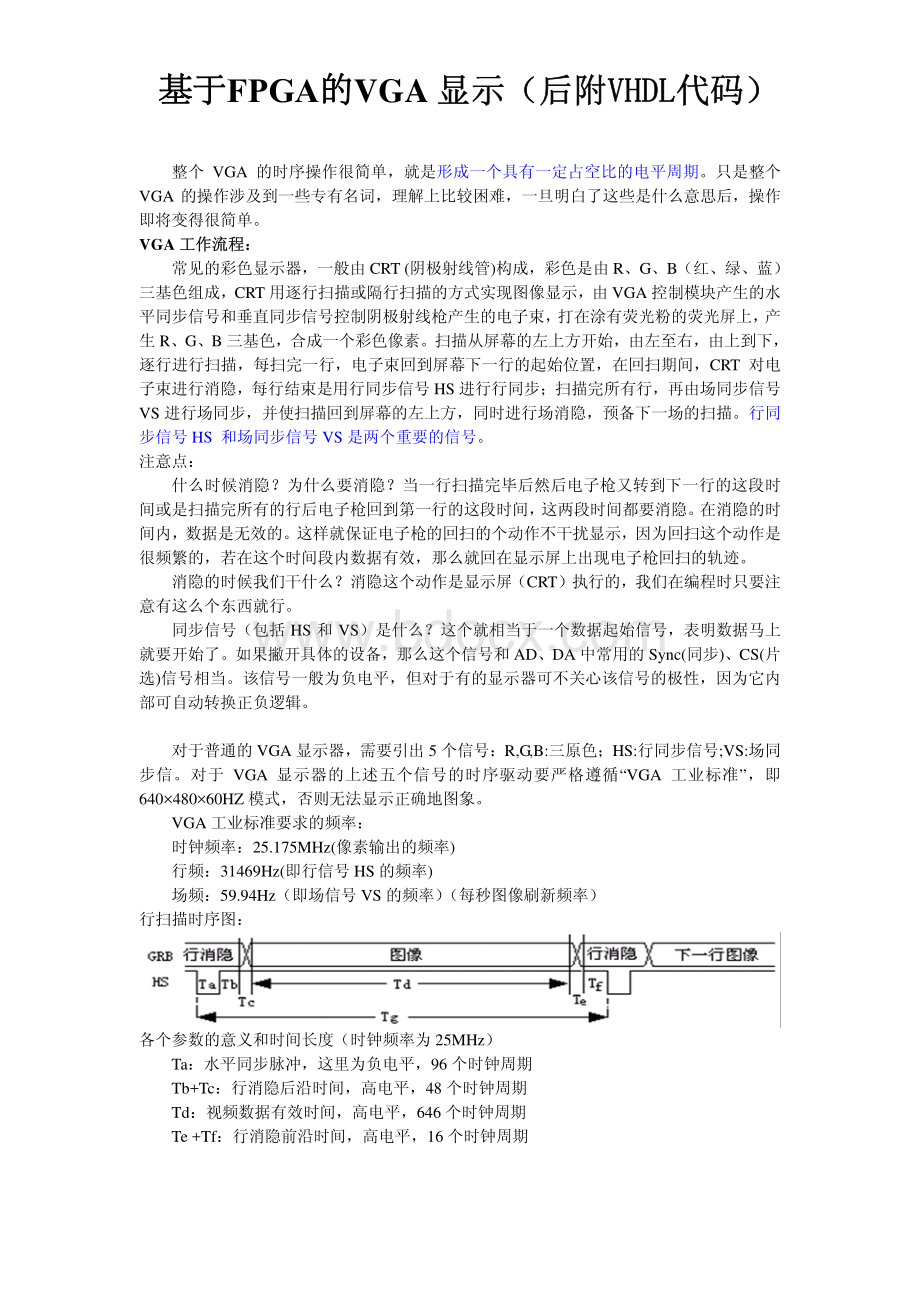

59.94Hz(即场信号VS的频率)(每秒图像刷新频率)行扫描时序图:

各个参数的意义和时间长度(时钟频率为25MHz)Ta:

水平同步脉冲,这里为负电平,96个时钟周期Tb+Tc:

行消隐后沿时间,高电平,48个时钟周期Td:

视频数据有效时间,高电平,646个时钟周期Te+Tf:

行消隐前沿时间,高电平,16个时钟周期Tg;

行周期时间。

Tg=Ta+Tb+Tc+Td+Te+Tf=800个时钟周期。

场扫描时序图:

各个参数意义和时间长度(单位是行周期)Ta:

垂直同步脉冲,这里为负电平,2个行周期Tb+Tc:

列消隐后沿时间,高电平,32个行周期Td:

视频数据有效时间,高电平,480个行周期Te+Tf:

列消隐前沿时间,高电平,11个行周期Tg;

场视频周期。

Tg=Ta+Tb+Tc+Td+Te+Tf=524个行周期。

观察电平情况,可以发现这个两个时序本质上就是由一个低电平(同步信号)加一个高电平(前沿+后沿+数据有效时间)构成。

所以,编写这个时序的时候,只要按照上述的时间要求构成这么一个占空比的周期就可以。

当时钟频率不是25MHz时,我们只要把以上的参数按比例适当调整即可。

我们给出不同时钟频率下的时间参数。

逐行解释:

12:

40M时钟输入,复位信号输入(低电平复位)13:

行同步信号和场同步信号输出14:

红、绿、蓝信号输出15:

拨码开关输入。

根据拨码开关的状态选择是横彩条还是竖彩条显示21-25:

定义一些常量,表示行同步信号的相关参数,具体值可见上表27-31:

定义一些常量,表示场同步信号的相关参数,具体值可见上表33:

自定义一种枚举类型h_state,表示整个扫描过程中行同步信号的状态34:

自定义一种枚举类型v_state,表示整个扫描过程中场同步信号的状态36:

定义一个行同步信号的内部信号量37-38:

分别用上述的自定义枚举类型定义两个信号。

在程序中需要用这两个信号分别实现行同步信号和场同步信号的状态改变。

40-41:

定义两个计数器,它们分别从两个进程中把变量的值传出来。

46:

将内部行同步信号并行输出到端口48-100:

产生行同步信号。

用状态机实现。

50:

定义一个计数器52-55:

系统复位。

状态机置为hs_front,即下一步进入消隐前沿;

清零计数器;

把行同步信号拉高56-99:

系统正常工作,通过状态机产生行同步信号。

整个状态的流程是:

行消隐前沿-行同步脉冲-行消隐后沿-行有效数据时间-行消隐前沿,如此循环。

57:

计数器加159-66:

行消隐前沿行消隐前沿。

60-62:

行消隐前沿未结束,状态机状态不变(即还是hs_front);

根据时序要求,拉高行同步信号63-66:

行消隐结束,状态机转到下一个状态hs_sync-行同步脉冲;

同时根据时序要求拉低行同步信号67-74:

行同步脉冲行同步脉冲68-70:

行同步脉冲未结束,状态机状态不变(即还是hs_sync);

根据时序要求拉低行同步信号71-74:

行同步脉冲结束,状态机转到下一个状态hs_back-行消隐后沿;

同时根据时序要求拉高行同步脉冲75-82:

行消隐后沿行消隐后沿,类似与59-66或者是67-7483-91:

行有效数据时间行有效数据时间,类似与59-66或者是67-74。

状态机重新回到hs_front-行消隐前沿92-95:

其它的状态其它的状态。

把行同步信号拉高99:

把计数器变量的值传递到外部的信号量中去,我们需要用这个信号量做颜色值的设置。

102-154:

产生场同步信号。

该实现过程类似于行同步信号的产生,在此不再赘述。

只是要注意一点:

场时序中是以行周期为单位,所以我们用行同步信号脉冲来触发计数,非40M的像素时钟(即输入时钟)156-196:

根据拨码开关的状态和两个计数器的值分别设置颜色信号R、G、B159-176:

拨码开关全0,产生竖彩条。

其原理就是将行有效时间平分成几段,在每段内填充不同的颜色。

注意:

颜色数据只在行数据有效时间有效,所以要跳过前沿+同步+后沿时间。

具体操作就是在不同的行时间段内填充不同的颜色。

程序比较简单,大家可自行读懂。

177-194:

拨码开关全0,产生横彩条。

其原理就是将场有效时间平分成几段,在每段内填充不同的颜色。

具体操作和注意点同竖彩条的实现,在此不再赘述。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 基于 FPGA VGA 显示 详解 VHDL 代码

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整版)固定资产盘点表.xls

(完整版)固定资产盘点表.xls