常用数字处理算法的Verilog实现Word格式文档下载.docx

常用数字处理算法的Verilog实现Word格式文档下载.docx

- 文档编号:15890093

- 上传时间:2022-11-16

- 格式:DOCX

- 页数:16

- 大小:282.29KB

常用数字处理算法的Verilog实现Word格式文档下载.docx

《常用数字处理算法的Verilog实现Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《常用数字处理算法的Verilog实现Word格式文档下载.docx(16页珍藏版)》请在冰豆网上搜索。

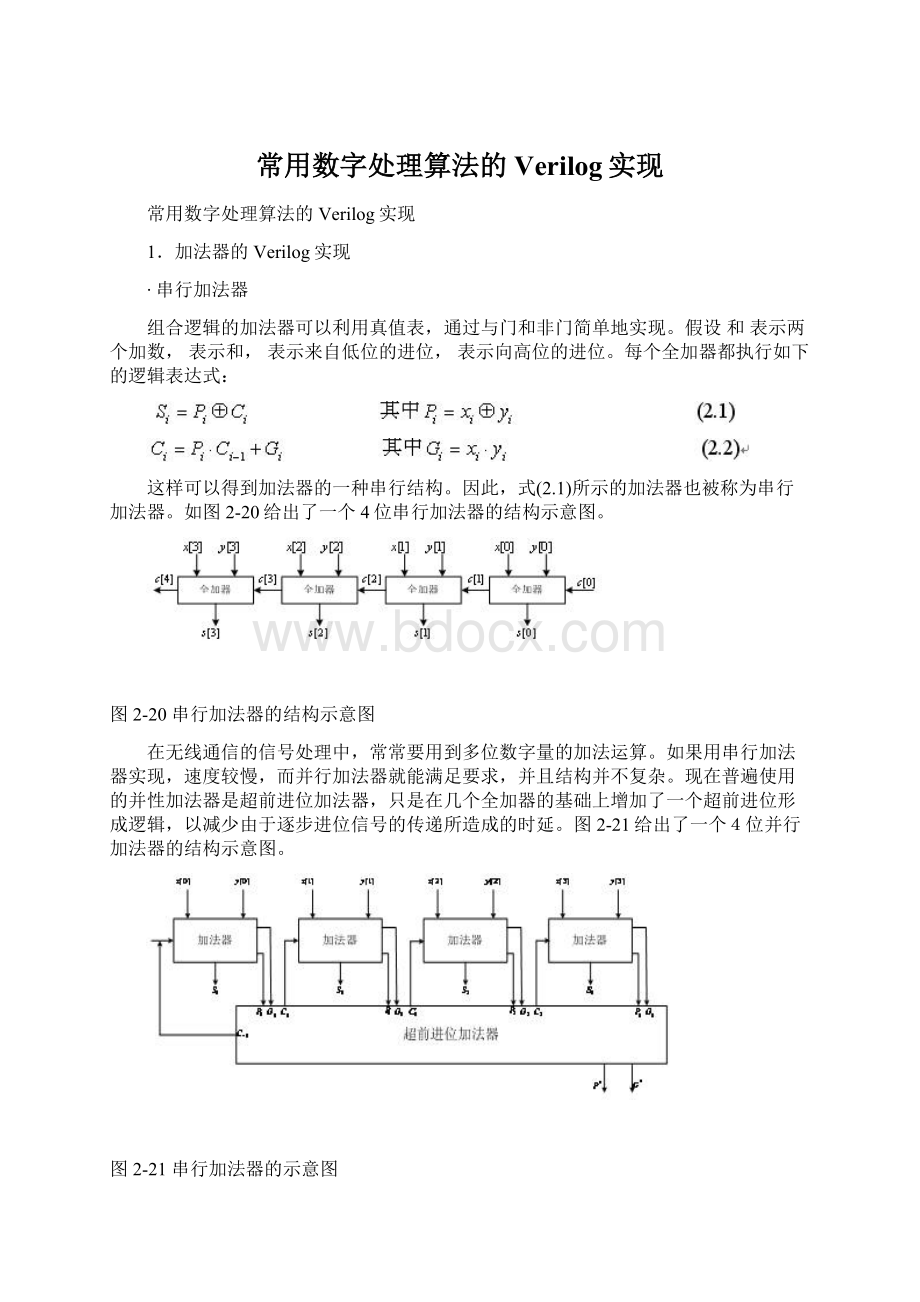

在使用了并行加法器后,仍旧只有在输出稳定后才能输入新的数进行下一次计算,即计算的节拍必须大于运算电路的延迟;

此外,许多门级电路和布线的延迟会随着位数的增加而累加,因此加法器的频率还是受到了限制。

但如果采用流水线,就有可能将一个算术操作分解为一些小规模的基本操作,将进位和中间值存储在寄存器中,并在下一个时钟周期内继续运算,这样就可以提高电路的利用效率。

将流水线规则应用于FPGA中,只需要很少或根本不需要额外的成本。

这是因为每个逻辑单元都包含两个触发器,大多数情况下这两个触发器或者没有用到,或者用于存储布线资源,那么就可以利用其来实现流水线结构。

如果采用了流水线后,加法器的速度仍然不能满足需要的话,可以采用第3章中将会提到的串并转换来进一步提高计算的并行度。

由于一个slice中有两个触发器,还需要有1个触发器来作为进位输出,那么采用级流水线,就可以构造一个最大位数为位的加法器。

下面给出一个16位流水线加法器的代码。

例2-2416位2级流水线加法器的Verilog设计

moduleadder16_2(cout,sum,clk,cina,cinb,cin);

input[15:

0]cina,cinb;

inputclk,cin;

output[15:

0]sum;

outputcout;

regcout;

regcout1;

reg[7:

0]sum1;

reg[15:

always@(posedgeclk)begin//低8位相加;

{cout1,sum1}={cina[7],cina[7:

0]}+{cinb[7],cinb[7:

0]}+cin;

end

always@(posedgeclk)begin//高8位相加,并连成16位

{cout,sum}={{cina[15],cina[15:

8]}+{cinb[15],cinb[15:

8]}+cout1,sum1};

endmodule

上述程序经过synplifyPro综合后,得到如图2-22所示的RTL级结构图。

2-2216位加法器的RTL结构图

在ModelSim6.2b中完成仿真,其结果如图2-23所示,正确地实现了16比特加法。

图2-2316位加法器的RTL结构图

2.乘法器的Verilog实现

∙串行乘法器

两个N位二进制数x、y的乘积,最简单的方法就是利用移位操作来实现,用公式可以表示为:

(2.3)

这样输入量随着k的位置连续地变化,然后累加

。

例2-25用Verilog实现一个8位串行乘法器

moduleade(clk,x,y,p);

inputclk;

input[7:

0]x,y;

output[15:

0]p;

reg[15:

parameters0=0,s1=1,s2=2;

reg[2:

0]count;

reg[1:

0]state;

0]p1,t;

//比特位加倍

reg[7:

0]y_reg;

always@(posedgeclk)begin

case(state)

s0:

begin//初始化

y_reg<

=y;

state<

=s1;

count=0;

p1<

=0;

t<

={{8{x[7]}},x};

end

s1:

begin//处理步骤

if(count==7)//判断是否处理结束

=s2;

elsebegin

if(y_reg[0]==1)

p1<

=p1+t;

=y_reg>

>

1;

//移位

=t<

<

count<

=count+1;

s2:

begin

p<

=p1;

state<

=s0;

endcase

上述程序在SynplifyPro中综合后,得到如图2-24所示的RTL级结构示意图。

图2-24串行乘法器的RTL结构图

图2-25给出了串行乘法器模块在ModelSim中的仿真结果,验证了功能的正确性。

图2-25串行乘法器的局部仿真结果示意图

从仿真结果可以看出,上述串行乘法器,速度比较慢,时延很大,但这种乘法器的优点是所占用的资源是所有类型乘法器中最少的,在低速的信号处理中有着广泛的应用。

∙流水线乘法器

一般的快速乘法器通常采用逐位并行的迭代阵列结构,将每个操作数的N位都并行地提交给乘法器。

但是一般对于FPGA来讲,进位的速度快于加法的速度,这种阵列结构并不是最优的。

所以可以采用多级流水线的形式,将相邻的两个部分乘积结果再加到最终的输出乘积上,即排成一个二叉树形式的结构,这样对于N位乘法器需要log2(N)级来实现。

一个8位乘法器,如图2-26所示。

图2-26流水线乘法器结构图

例2-26用VerilogHDL实现一个4位的流水线乘法器

modulemul_addtree(mul_a,mul_b,mul_out,clk,rst_n);

parameterMUL_WIDTH=4;

parameterMUL_RESULT=8;

input[MUL_WIDTH-1:

0]mul_a;

0]mul_b;

inputclk;

inputrst_n;

output[MUL_RESULT-1:

0]mul_out;

reg[MUL_RESULT-1:

0]stored0;

0]stored1;

0]stored2;

0]stored3;

0]add01;

0]add23;

always@(posedgeclkornegedgerst_n)

if(!

rst_n)

begin//初始化寄存器变量

mul_out<

=8'

b0000_0000;

stored0<

stored1<

stored2<

stored3<

add01<

add23<

else

begin//实现移位相加

=mul_b[3]?

{1'

b0,mul_a,3'

b0}:

8'

b0;

=mul_b[2]?

{2'

b0,mul_a,2'

=mul_b[1]?

{3'

b0,mul_a,1'

=mul_b[0]?

{4'

b0,mul_a}:

add01<

=stored1+stored0;

add23<

=stored3+stored2;

=add01+add23;

上述程序在SynplifyPro软件中综合后,得到如图2-27所示的RTL级结构示意图。

图2-27流水线乘法器的RTL结构示意图

图2-28给出了流水线乘法器模块在ModelSim中的仿真结果,验证了功能的正确性。

图2-28流水线乘法器的局部仿真结果示意图

从仿真结果可以看出,上述流水线乘法器比串行加法器的速度快很多,在非高速的信号处理中有着广泛的应用。

至于高速信号的乘法一般需要利用FPGA芯片中内嵌的硬核DSP单元来实现。

3.无符号除法器的Verilog实现

两个无符号二进制数(如正整数)相除的时序算法是通过“减并移位”的思想来实现的,即从被除数中重复地减去除数,直到已检测到余数小于除数。

这样可以通过累计减法运算的次数而得到商;

而余数是在减法运算结束时被除数中的剩余值。

当除数较小时,这种基本电路都必须进行多次减

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 常用 数字 处理 算法 Verilog 实现

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx

广东省普通高中学业水平考试数学科考试大纲Word文档下载推荐.docx