异步清零和同步时钟使能的4位加法计数器Word文档格式.doc

异步清零和同步时钟使能的4位加法计数器Word文档格式.doc

- 文档编号:15510257

- 上传时间:2022-11-03

- 格式:DOC

- 页数:4

- 大小:68.50KB

异步清零和同步时钟使能的4位加法计数器Word文档格式.doc

《异步清零和同步时钟使能的4位加法计数器Word文档格式.doc》由会员分享,可在线阅读,更多相关《异步清零和同步时钟使能的4位加法计数器Word文档格式.doc(4页珍藏版)》请在冰豆网上搜索。

当ENA为‘0’时锁存器输出为高阻态。

当计数器输出“1111”时,进位信号COUT为“1”。

三、实验内容

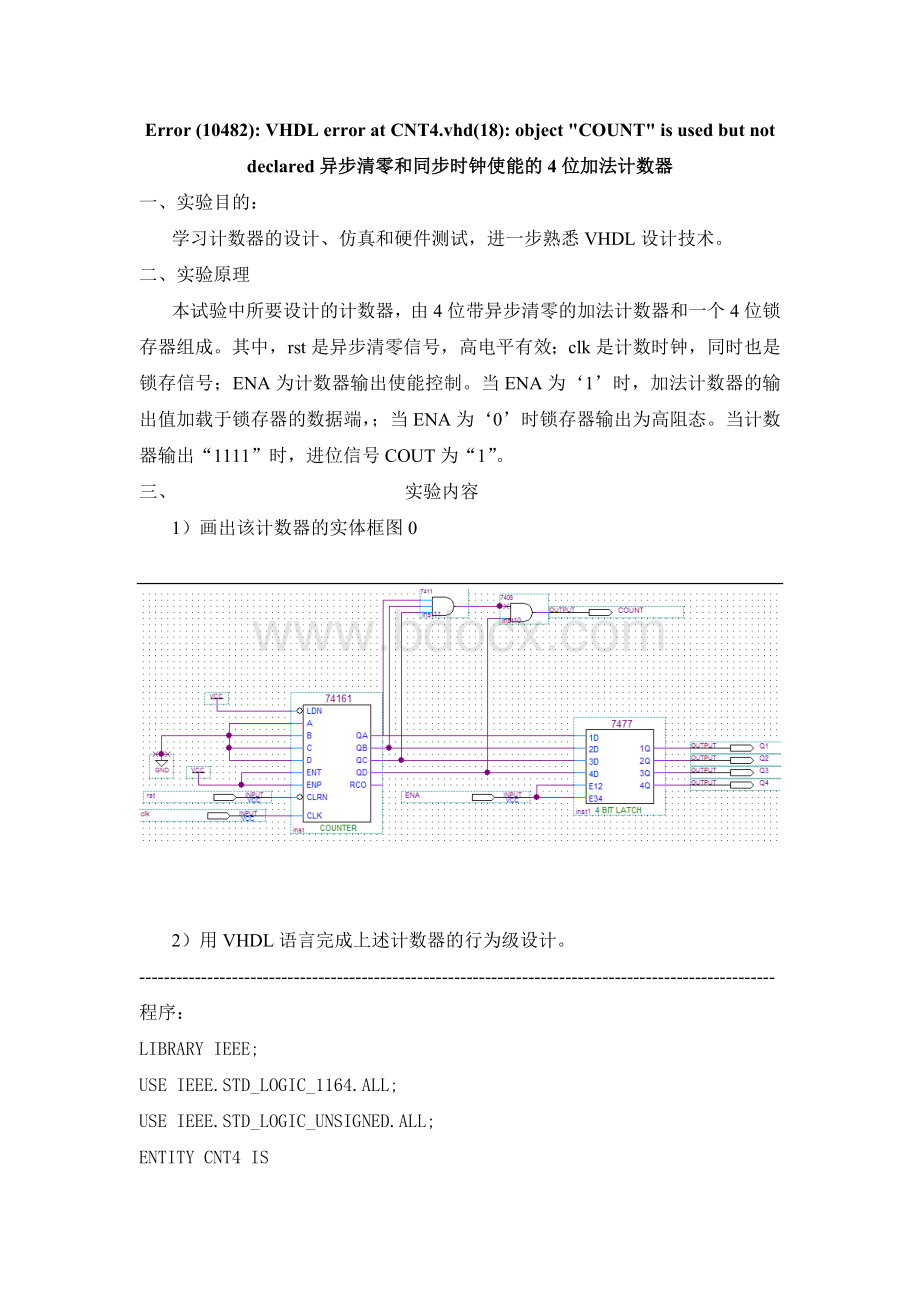

1)画出该计数器的实体框图0

2)用VHDL语言完成上述计数器的行为级设计。

-------------------------------------------------------------------------------------------------------

程序:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT4IS

PORT(RST,CLK,ENA:

INSTD_LOGIC;

COUT:

OUTSTD_LOGIC;

OUTY:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDCNT4;

ARCHITECTUREbehvOFCNT4IS

BEGIN

PROCESS(RST,ENA,CLK)

VARIABLECQI:

STD_LOGIC_VECTOR(3DOWNTO0);

IFRST='

1'

THENCQI:

=(OTHERS=>

'

0'

);

ELSIFCLK'

EVENTANDCLK='

THEN

IFENA='

THEN

IFCQI<

15THENCQI:

=CQI+1;

ELSECQI:

ENDIF;

ENDIF;

ENDIF;

IFCQI=15THENCOUT<

='

;

ELSECOUT<

OUTY<

=CQI;

ENDPROCESS;

ENDbehv;

3)用QuartusII对上述设计进行编译、综合、仿真,给出其所有信号的仿真波形和时序分析数据。

--------------------------------------------------------------------------------------------------

仿真波形:

引脚锁定:

信号

旧试验箱

新试验箱No.5

管脚号

连接的器件

clk

43

Clk1

153

CLK2

rst

35

开关2

234

键2

ena

30

开关1

233

键1

Outy(3)

29

LED12

1

LED1

Outy

(2)

28

LED11

2

LED2

Outy

(1)

27

LED10

3

LED3

Outy(0)

25

LED9

4

LED4

cout

23

LED7

6

LED6

PORT(A,CLK,B:

Y:

ARCHITECTUREbehavOFCNT4IS

SIGNALCQI:

STD_LOGIC_VECTOR(3DOWNTO0);

PROCESS(A,B,CLK)

IFA='

CQI<

="

0000"

Y<

COUT<

IFB='

CQI<

Y<

COUT<

=CQI(0)ANDCQI

(1)ANDCQI

(2)ANDCQI(3);

ENDbehav;

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 异步 清零 同步 时钟 加法 计数器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

保育笔记.doc

保育笔记.doc

幼儿园日常安全检查记录表.xls

幼儿园日常安全检查记录表.xls