附录数电常用管脚内部逻辑图Word文件下载.docx

附录数电常用管脚内部逻辑图Word文件下载.docx

- 文档编号:15239359

- 上传时间:2022-10-28

- 格式:DOCX

- 页数:16

- 大小:464.98KB

附录数电常用管脚内部逻辑图Word文件下载.docx

《附录数电常用管脚内部逻辑图Word文件下载.docx》由会员分享,可在线阅读,更多相关《附录数电常用管脚内部逻辑图Word文件下载.docx(16页珍藏版)》请在冰豆网上搜索。

74ls214输入双与门74ls273输入三或非门

74ls308输入与非门74ls322输入四或门

74ls48bcd-七段译码器/驱动器74ls854位数字比较器

74ls862输入四异或门74ls90十进制计数器

74ls112负沿触发双j-k触发器(带预置端和清除端)74ls1383-8线译码器/多路转换器

74ls1488线-3线八进制优先编码器74ls160可预置十进制计数器(异步清除)

74ls161可预置四位二进制计数器(并清除异步)74ls163可预置四位二进制计数器(并清除异步)

74ls1648位并行输出串行移位寄存器74ls175四d触发器

74ls175功能表

74ls190同步可逆计数器(bcd,二进制)74ls192同步可逆计数器

74ls194四位双向通用移位寄存器74ls373八d锁存器

74ls373功能表

二.CMOS集成电路引脚图

4001 四2输入或非门4002 双4输入或非门

4011 四2输入与非门4012双4输入与非门Y=/ABCD

4013双D型触发器(带预置和清除端)40148位串入/并入—串出移位寄存器

4025三3输入或非门4027双J-K主从触发器(带置位和复位端)

4028BCD—十进制译码器4030四异或门

输入

输出

S

R

EN

Q

×

L

高阻

H

不变

不定

4043 四或非R─S(三态)4043功能表

4068 8输入与非/与门

4069六反相器4070 四异或门

4071 四2输入或门4072 双4输入或门

4073 三3输入与门4081 四2输入与门

4082 双4输入与门40106 六施密特触发器(反相)

40192、40193 可预置可逆计数器(双时钟)4514、4515 4位锁存/4-16线译码器

4515输出H电平有效,4515输出L电平有效。

4518 双BCD同步加计数器4553三数字BCD计数器

实验箱简介·

·

1

第一部分基本单元实验

实验一 TTL集成逻辑门的逻辑功能与参数测试·

4

实验二 CMOS集成逻辑门的逻辑功能与参数测试·

11

实验三组合逻辑电路的设计与测试·

14

实验四译码器及其应用·

17

实验五数据选择器及其应用·

24

实验六触发器及其应用·

30

实验七 计数器及其应用·

37

实验八 移位寄存器及其应用·

43

实验九自激多谐振荡器·

50

实验十 单稳态触发器与施密特触发器·

53

实验十一555时基电路及其应用·

58

第二部分综合性实验

实验十二智力竞赛抢答器·

63

实验十三电子秒表·

65

实验十四电子密码锁·

70

实验十五数字钟·

72

第三部分课程设计

实验十六简易脉宽设计电路·

74

实验十七 数字频率计·

77

实验十八拔河游戏机·

82

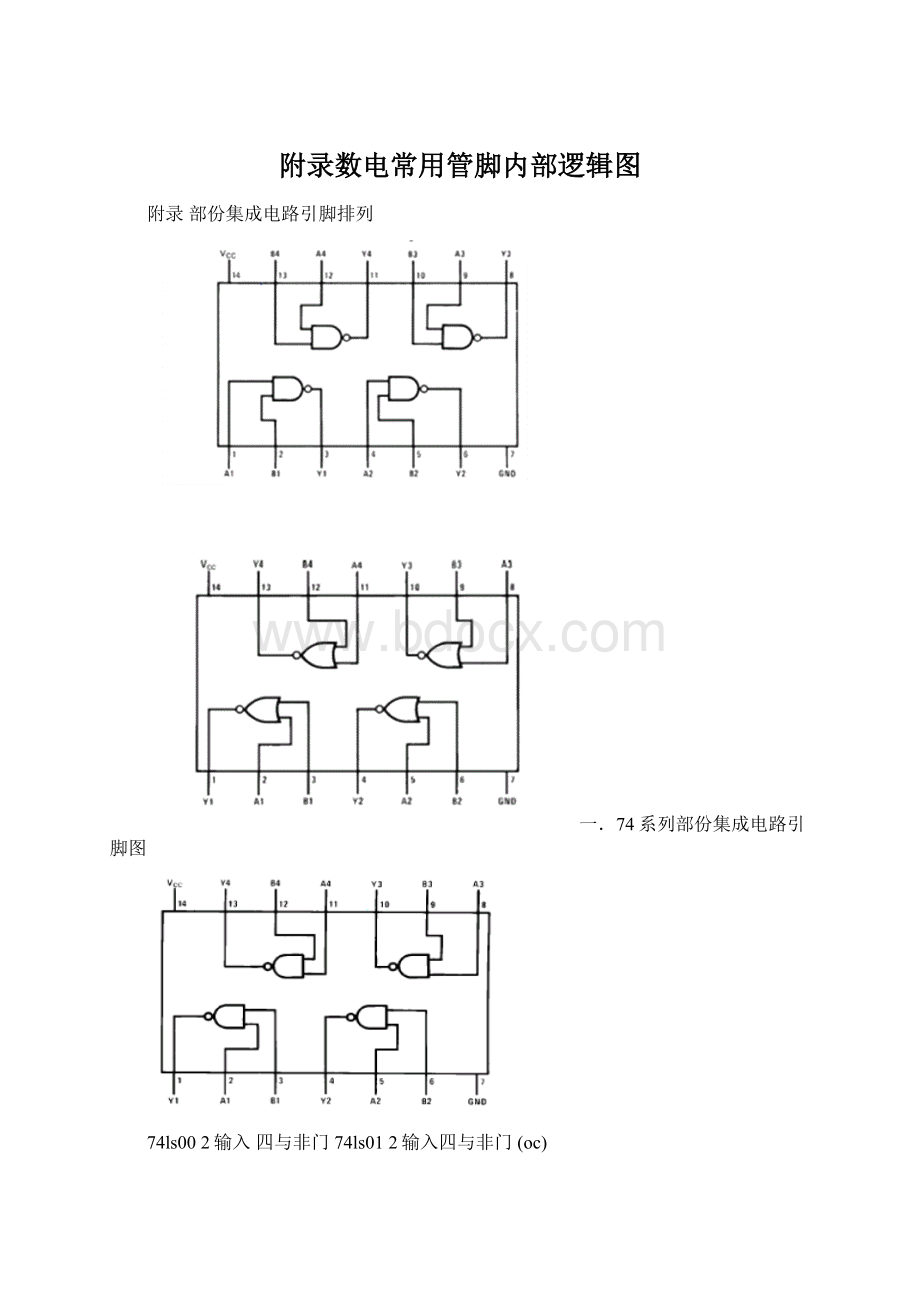

附录部份集成电路引脚排列·

87

一.74系列部份集成电路引脚图·

二.CMOS集成电路引脚图·

92

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 附录 常用 管脚 内部 逻辑

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls