数字电子技术作业文档格式.docx

数字电子技术作业文档格式.docx

- 文档编号:15236264

- 上传时间:2022-10-28

- 格式:DOCX

- 页数:64

- 大小:4.20MB

数字电子技术作业文档格式.docx

《数字电子技术作业文档格式.docx》由会员分享,可在线阅读,更多相关《数字电子技术作业文档格式.docx(64页珍藏版)》请在冰豆网上搜索。

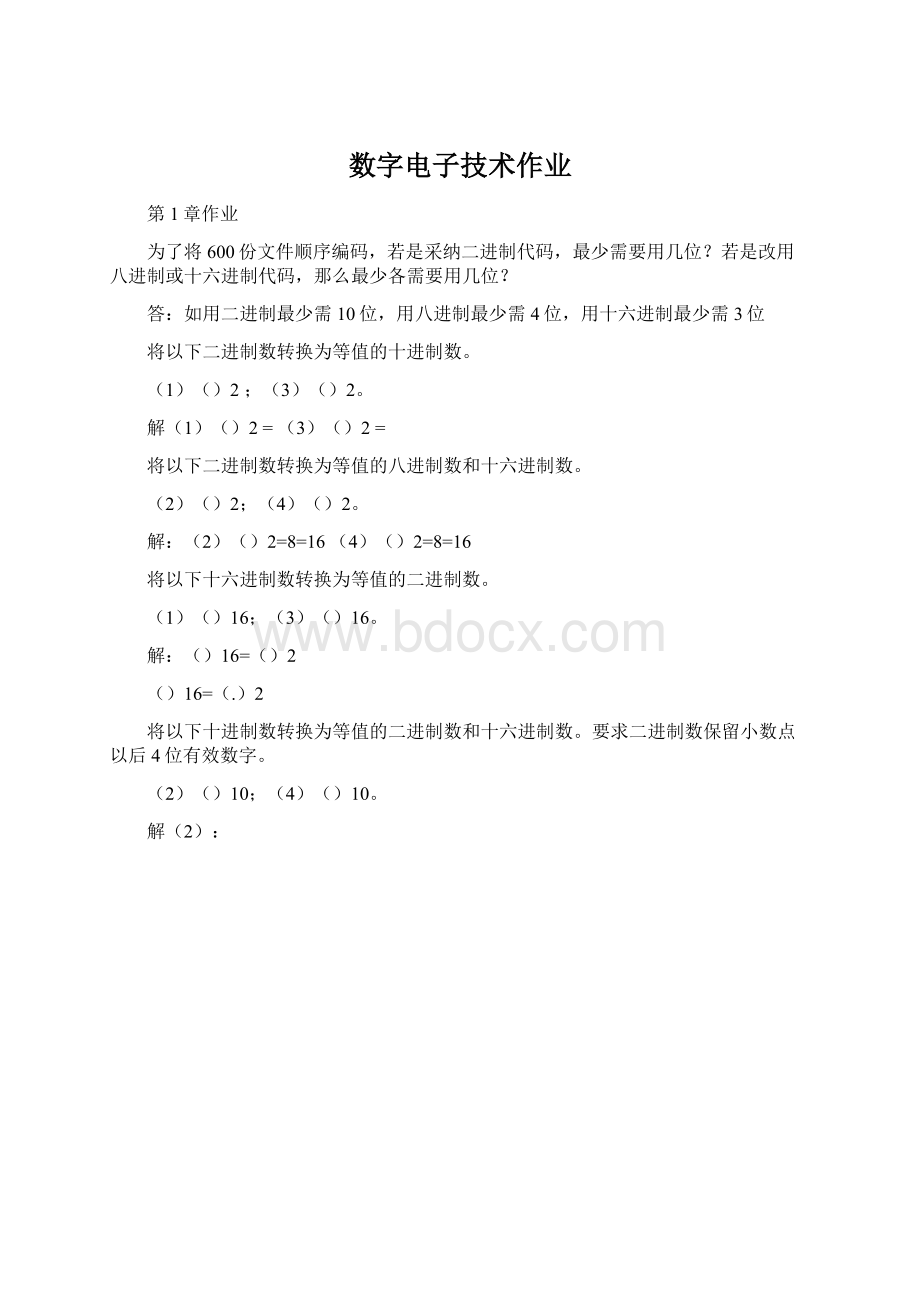

(3)()16。

()16=()2

()16=(.)2

将以下十进制数转换为等值的二进制数和十六进制数。

要求二进制数保留小数点以后4位有效数字。

(2)()10;

(4)()10。

解

(2):

用二进制补码运算计算以下各式。

式中的4位二进制数是不带符号位的绝对值。

若是和为负数,请求出负数的绝对值。

(提示:

所用补码的有效位数应足够表示代数和的最大绝对值。

)

(2)1101+1011;

(4)1101-1011;

(6)1011-1101;

(8)-1101-1011。

第2章作业

已知逻辑函数的真值表如表(a)、(b)所示,试写出对应的逻辑函数式。

表(a)表(b)

写出图(a)、(b)所示电路的输出逻辑函数式。

图

已知逻辑函数Y的波形图如下图,试求Y的真值表和逻辑函数式。

图

将以下各函数式化为最小项之和的形式。

(1)

(3)

(5)

将以下逻辑函数式化为与非–与非形式,并画出全数由与非逻辑单元组成的逻辑电路图。

(2)

(4)

电路图如下:

将以下逻辑函数式化为或非–或非形式,并画出全数由或非逻辑单元组成的逻辑电路图。

电路图如下:

用逻辑代数的大体公式和经常使用公式将以下逻辑函数化为最简与或形式。

(6)

(8)

(10)

用卡诺图化简法化简以下逻辑函数。

将以下具有约束项的逻辑函数化为最简与或形式。

(2),给定约束条件为。

(4),给定约束条件为。

第3章作业

试画出图(a)、(b)两个电路的输出电压波形,输入电压波形如图(c)所示。

图中的G1~G4是OD输出结构的与非门74HC03,它们接成线与结构。

试写出线与输出Y与输入A1、A2、B1、B2、C1、C2、D1、D2之间的逻辑关系式,并计算外接电阻RL取值的许诺范围。

在图所示的电路中,试计算当输入端别离接0V、5V和悬空时输出电压vO的数值,并指出三极管工作在什么状态。

假定三极管导通以后vBE≈,电路参数如图中所注。

三极管的饱和导通压降VCE(sat)≈,饱和导通内阻RCE(sat)=20Ω。

指出图中各门电路的输出是什么状态(高电平、低电平或高阻态)。

已知这些门电路都是74系列TTL电路。

说明图中各门电路的输出是高电平仍是低电平。

已知它们都是74HC系列CMOS电路。

在图所示的由74系列TTL与非门组成的电路中,计算门GM能驱动多少一样的与非门。

要求GM输出的高、低电平知足VOH≥,VOL≤。

与非门的输入电流为IIL≤,IIH≤40μA。

VOL≤时输出电流最大值为IOL(max)=16mA,VOH≥时输出电流最大值为IOH(max)=。

GM的输出电阻可忽略不计。

在图所示由74系列TTL或非门组成的电路中,试求门GM能驱动多少一样的或非门。

要求GM输出的高、低电平知足VOH≥、VOL≤。

或非门每一个输入端的输入电流为IIL≤,IIH≤40μA。

试说明在以下情形下,用万用表测量图中的vI2端取得的电压各为多少:

(1)vI1悬空;

(2)vI1接低电平();

(3)vI1接高电平();

(4)vI1经51Ω电阻接地;

(5)vI1经10kΩ电阻接地。

图中的与非门为74系列的TTL电路,万用表利用5V量程,内阻为20kΩ/V。

假设将上题中的与非门改成74系列TTL或非门,试问在上述五种情形下测得的vI2各为多少?

假设将图中的门电路改成CMOS与非门,试说明当vI1为题[]给出的五种状态时测得的vI2各等于多少?

在图所示电路中R1、R2和C组成输入滤波电路。

当开关S闭合时,要求门电路的输入电压VIL≤;

当开关S断开时,要求门电路的输入电压VIH≥4V,试求R1和R2的最大许诺阻值。

G1~G5为74LS系列TTL反相器,它们的高电平输入电流IIH≤20μA,低电平输入电流。

计算图电路中上拉电阻RL的阻值范围。

其中G1、G2、G3是74LS系列OC门,输出管截止时的漏电流为IOH≤100μA,输出低电平VOL≤时许诺的最大负载电流IOL(max)=8mA。

G4、G5、G6为74LS系列与非门,它们的输入电流为,IIH≤20μA。

给定VCC=5V,要求OC门的输出高、低电平知足VOH≥、VOL≤。

在图电路中,已知G1和G2、G3为74LS系列OC输出结构的与非门,输出管截止时的漏电流最大值为IOH(max)=100μA,低电平输出电流最大值为IOL(max)=8mA,这时输出的低电平为VOL(max)=。

G3~G5是74LS系列的或非门,它们高电平输入电流最大值为IIH(max)=20μA,低电平输入电流最大值为IIL(max)=。

给定VCC=5V,要求知足VOH≥34V、VOL≤,试求RL取值的许诺范围。

图所示是一个继电器线圈驱动电路。

要求在vI=VIH时三极管T截止,而vI=0时三极管T饱和导通。

已知OC门输出管截止时的漏电流IOH≤100μA,导通时许诺流过的最大电流IOL(max)=10mA,管压降小于,导通内阻小于20Ω。

三极管β=50,饱和导通压降VCE(sat)=,饱和导通内阻RCE(sat)=20Ω。

继电器线圈内阻240Ω,电源电压VCC=12V,VEE=-8V,R2=Ω,R3=18kΩ,试求R1的阻值范围。

在图(a)所示电路中已知三极管导通时VBE=,饱和压降VCE(sat)=,饱和导通内阻为RCE(sat)=20Ω,三极管的电流放大系数β=100。

OC门G1输出管截止时的漏电流约为50μA,导通时许诺的最大负载电流为16mA,输出低电平≤。

G2~G5均为74系列TTL电路,其中G2为反相器,G3和G4是与非门,G5是或非门,它们的输入特性如图(b)所示。

试问:

(1)在三极管集电极输出的高、低电平知足VOH≥、VOL≤的条件下,Ra的取值范围有多大?

(2)假设将OC门改成推拉式输出的TTL门电路,会发生什么问题?

第4章

图是一个多功能函数发生电路,试写出当S0S1S2S3为0000~111116种不同状态时输出Y的函数关系式。

有一水箱由大、小两台水泵ML和MS供水,如图所示。

水箱中设置了3个水位检测元件A、B、C,水面低于检测元件时,检测元件给出高电平;

水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C点时水泵停止工作;

水位低于C点而高于B点时MS单独工作;

水位低于B点而高于A点时ML单独工作;

水位低于A点时ML和MS同时工作。

试用门电路设计一个操纵两台水泵的逻辑电路,要求电路尽可能简单。

设计一个代码转换电路,输入为4位二进制代码,输出为4位格雷码。

能够采纳各类逻辑功能的门电路来实现。

4位格雷码见本书第节的表。

表试画出用3线–8线译码器74HC138(见图)和门电路产生如下多输出逻辑函数的逻辑图。

图用3线–8线译码器74HC138和门电路设计1位二进制全减器电路。

输入为被减数、减数和来自低位的借位;

输出为两数之差和向高位的借位信号。

用8选1数据选择器74HC151(见图)设计一个组合逻辑电路。

该电路有3个输入逻辑变量A、B、C和1个工作状态操纵变量M。

当M=0时电路实现“意见一致”功能(A、B、C状态一致时输出为1,不然输出为0),而M=1时电路实现“多数表决”功能,即输出与A、B、C中多数的状态一致。

图用8选1数据选择器设计一个函数发生器电路,它的功能如表所示。

表

第5章作业

画出图由或非门组成的SR锁存器输出端Q、的电压波形,输入端SD、RD的电压波形如图中所示。

如下图

在图所示电路中,假设CLK、S、R的电压波形如图中所示,试画出Q和端与之对应的电压波形。

假定触发器的初始状态为Q=0。

解如下图

假设主从结构SR触发器的CLK、S、R、各输入端的电压波形如下图,,试画出Q、端对应的电压波形。

假设主从结构JK触发器CLK、、、J、K端的电压波形如下图,试画出Q、端对应的电压波形。

已知CMOS边沿触发方式JK触发器各输入端的电压波形如下图,试画出Q、端对应的电压波形。

设图中各触发器的初始状态皆为Q=0,试画出在CLK信号持续作用下各触发器输出端的电压波形。

在图所示的主从JK触发器电路中,CLK和A的电压波形如图中所示,试画出Q端对应的电压波形。

设触发器的初始状态为Q=0。

试画出图所示电路输出端Y、Z的电压波形。

输入信号A和CLK的电压波形如图中所示。

设触发器的初始状态均为Q=0。

第6章作业

试分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路可否自启动。

分析图的时序逻辑电路,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路可否自启动。

分析图的计数器电路,画出电路的状态转换图,说明这是多少进制的计数器。

十六进制计数器74LS161的功能表如表所示。

表图

试分析图的计数器在M=1和M=0时各为几进制。

74160的功能表与表相同。

设计一个可控进制的计数器,当输入操纵变量M=0时工作在五进制,M=1时工作在十五进制。

请标出计数输入端和进位输出端。

图电路是由两片同步十进制计数器74160组成的计数器,试分析这是多少进制的计数器,两片之间是几进制。

、

画出用两片同步十进制计数器74160接成同步三十一进制计数器的接线图。

能够附加必要的门电路。

74160的逻辑图和功能表见图和表。

图用JK触发器和门电路设计一个4位格雷码计数器,它的状态转换表应如表所示。

设计一个操纵步进电动机三相六状态工作的逻辑电路。

若是用1表示电机绕组导通,0表示电机绕组截止,那么三个绕组ABC的状态转换图应如下图,M为输入操纵变量,当M=1时为正转,M=0时为反转。

第7章作业

试用2片1024×

8位的ROM组成1024×

8位的存储器。

试用4片2114(1024×

4位的RAM)和3线﹣8线译码器74HC138(见图)组成4096×

4位的RAM。

试用16片2114(1024×

4位的RAM)和3线﹣8线译码器74HC138(见图)组成8K×

8位的RAM。

用16×

4位的ROM设计一个将两个2位二进制数相乘的乘法器电路,列

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字 电子技术 作业

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls