VHDLQuartusII调用Modelsim进行仿真文档格式.docx

VHDLQuartusII调用Modelsim进行仿真文档格式.docx

- 文档编号:15042986

- 上传时间:2022-10-27

- 格式:DOCX

- 页数:18

- 大小:1.85MB

VHDLQuartusII调用Modelsim进行仿真文档格式.docx

《VHDLQuartusII调用Modelsim进行仿真文档格式.docx》由会员分享,可在线阅读,更多相关《VHDLQuartusII调用Modelsim进行仿真文档格式.docx(18页珍藏版)》请在冰豆网上搜索。

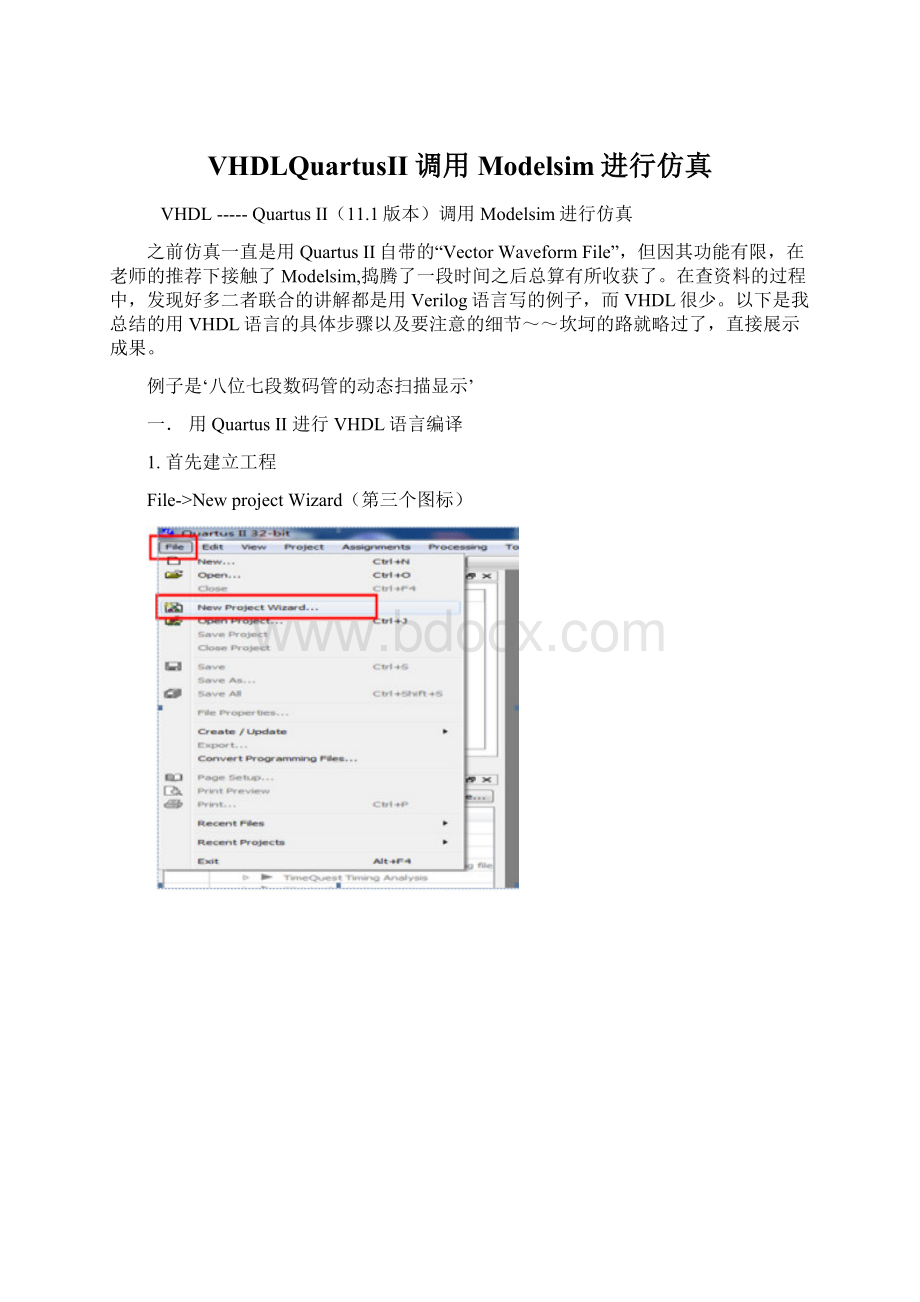

一.用QuartusII进行VHDL语言编译

1.首先建立工程

File->

NewprojectWizard(第三个图标)

填入所建工程的目录以及名称,注意稍后的源程序中实体名必须和这里的名称相同。

填好后单击finish,然后单击yes。

2.新建VHDL源程序文件

New->

VHDLFile->

OK

将程序写进去(这里只讲步骤,不讲源程序的写法)

注意:

程序中的实体名必须和之前建工程时所命名的文件名相同!

然后保存一下,不用改动,直接单击保存。

3.编译

快捷键按钮在界面中上方的红色倒三角,显示编译成功之后关闭编译报告。

4.设备设置

具体的实验器件根据提供的实验板设定

Assignment->

Device

4.引脚分配Assignment->

PinPlanner

在Location下的方格中填入对应的硬件引脚,也是根据实验板而定

6.引脚分配好之后再次编译一下,使分配的引脚起作用。

一、调用Modelsim

1、设置仿真工具为Modelsim-altera

Tool->

Options->

EDAToolOptions,

在Modelsim-Altera后面的地址改为Modelsim-Altera.exe在你电脑中的位置,然后点击OK。

2、写TestBench文件,这里使用QuartusII生成的模板

Processing->

start->

StartTestBenchTemplateWriter,

显示成功后关闭生成报告。

这时会生成后缀为.vht的文件就是我们需要的,可以在这个实验开始时所建工程名的文件夹下的simulation子文件夹下找到。

我们可以通过QuartusII左上角的打开图标打开.vht文件,注意把文件类型更改成Allfiles或者下图所示的类型,否则会找不到。

然后在simulation文件夹下找到并打开它。

模板已经给出了端口部分的代码、接口变量的声明和例化语句映射等,我们要做的就是在其后的进程Process中填入需要的测试代码。

如下:

init和always为关键字,需要改动一下

保存一下

3、将TestBench添加到工程中

单击Open

点击Add后,一直单击OK到Setting界面全部关闭。

4、可以开始仿真了

Tools->

RunsimulationTool->

RTLSimulation,这时就会自动启动Modelsim软件

如果之前的主程序以及TestBench没有错误了,就会出现下面的界面

点击上面的红点(stop),

单击Run按钮(旁边的时间根据实际需要调整),并通过Ctrl+鼠标滚动或者界面上的加号按钮,可以将波形调整到如下容易察看的间距,另外如果感觉一串0和1的组合不容易看懂,可以右击通过下面的方式将二进制数改为十进制或者十六进制的形式。

最终的波形图如下:

经检验与实验目的相符合,是正确的。

另外,可以滚动波形下方的游标来观察不同时刻的波形。

至此,QuartsII调用Modelsim已经圆满完成了,剩下的就是将程序下载到硬件实验板上进行验证了。

1.工程名称必须和主程序(.Vhd文件)中的实体名相同。

2.TestBench名称必须和TestBench程序(.Vht文件)中的实体名相同。

3.所有在进程(process)中用到的变量和信号都要进行初始化,否则会在仿真波形中得不到输出。

比如本例主程序中的变量q1,Testbench程序中的clk和key。

4.生成的TestBench模板根据需要、习惯可以任意改动。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- VHDLQuartusII 调用 Modelsim 进行 仿真

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx