串行口数据传输的仿真及硬件实现Word文档格式.docx

串行口数据传输的仿真及硬件实现Word文档格式.docx

- 文档编号:14822391

- 上传时间:2022-10-25

- 格式:DOCX

- 页数:18

- 大小:338.11KB

串行口数据传输的仿真及硬件实现Word文档格式.docx

《串行口数据传输的仿真及硬件实现Word文档格式.docx》由会员分享,可在线阅读,更多相关《串行口数据传输的仿真及硬件实现Word文档格式.docx(18页珍藏版)》请在冰豆网上搜索。

10^6÷

2=5×

10^5≈2^19。

所以需要5块74LS163芯片级联实现分频,所得频率为1MHz/2^19=1.9Hz.具体电路图如下:

2.字符发生器模块:

本次试验要求发送端产生信息码为111100010011010这个15位循环码。

字符发生模块使用由D触发器构成移位寄存器的序列信号发生器。

由于循环码为15位,2^3<

15<

2^4,故至少应该使用4位D触发器。

经检查,此序列所构成的15个4位的序列不重复,刚好可以用4为D触发器来做次序列发生器,D触发器选用74LS175四D触发器。

状态转移表:

Q4

Q3

Q2

Q1

D

1

卡诺图:

由卡诺图得:

D=Q4⊕Q3,但经过检查,通过此反馈是无法自启动的。

通过增加自由项,得D=。

经过检查,此此反馈可以自启动。

电路图如下:

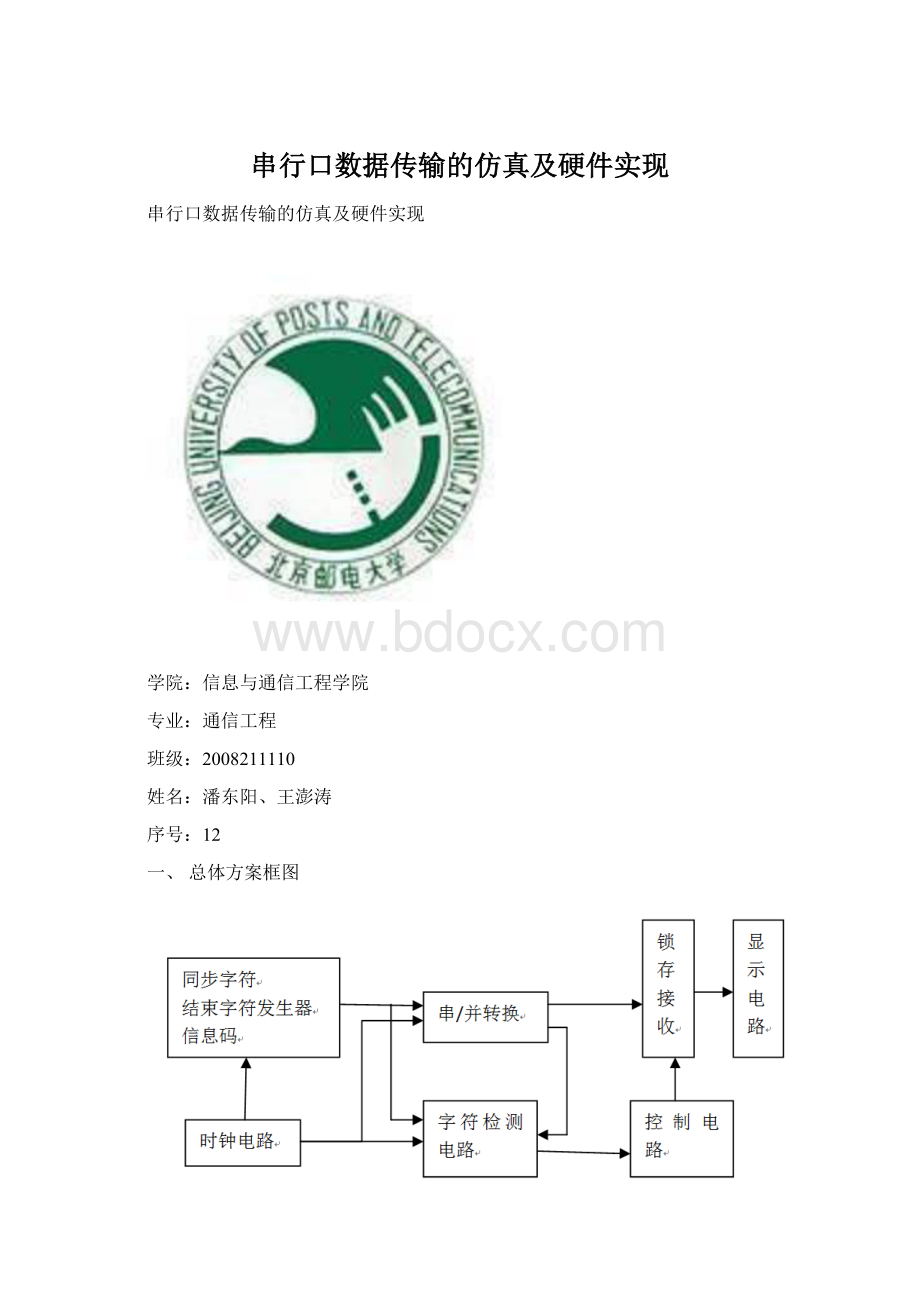

3.串/并转换模块:

串并转化的实现可以通过移位寄存器来实现,因为需要7位并行输出,所以需要两块移位寄存器74LS194级联构成。

4.并行字符检测电路模块:

相比于串行字符检测电路,并行字符检测电路相对容易。

并行字符检测电路只需要15位数据比较器即可,而该比较器可以由两个数据比较器74LS85级联得到。

具体电路图如下:

当检测到字符1111000时,输出一个高电平,作为控制电路的时钟信号。

5.控制电路模块:

控制电路完成的功能比较复杂。

首先,控制电路要保证在检测到同步码之前,锁存器关闭,没有任何输出;

其次,在检测到同步码之后,字符检测电路不能对后级有任何影响,而是由控制电路控制每个7位输出一次。

对于第一个功能可以使用一块D触发器74LS74接受字符检测电路的信号,再通过组合逻辑电路使接收到同步码产生的高电平后此部分电路输出恒定,对锁存电路没有影响;

对于第二个功能,可以由一个7进制计数器实现,这里选用同步置位的计数器74LS163。

具体如下:

6.锁存显示模块:

锁存电路比较简单,只需要一块74LS273锁存芯片就可以。

只要把数据的七个输入端分别连到串并转换的并行输出端,在把控制电路输出的控制电路接到时钟输入端即可。

7.显示电路模块:

只要把锁存器的七个输出端接到数码管相对应的a~g管脚就可以。

8.串行字符检测模块:

串行字符检测需要一位一位检测,然后每位都符合才输出信号。

若每位都检测,将会使用较多触发器,使电路复杂化。

经过观察,同步码1111000中后四位1000在整个序列111100010011010中是唯一的,所以检测1000四位即可。

当连续有4位与1000相应匹配时,则输出信号。

状态转移图如下:

对A、B、C、D分别编码为00、01、11、10,则状态转移表为:

D=0

D=1

00

01

11

10

输出为:

Z

卡诺图分别如下:

所以,由卡诺图可得:

D2=

D1=

Z=

由此可得到电路图:

9.纠错模块:

纠错模块应该包含错码发生器、检错模块和纠错模块。

实验中错码发生器产生的错码为:

111100000011010,通过类似序列发生器设计中的方法可以设计出其电路,此处使用同步计数器与数据选择器构成的信号发生器。

检错模块通过D触发器加逻辑门电路可以检测出是否有错码,若有,则输出1。

纠错部分接收到检测部分输出的1后,与原信号同一位进行异或运算,可以将其改为正确码。

此部分电路的难点是同步问题。

由于各部分之间的延时不一定相同,所以最终修改的码的位置不一定就是错码的位置。

这种问题只能在具体连接电路时通过加门电路来不断尝试来取得同步。

具体电路原理图如下:

三、总体电路原理图

四、用坐标纸画出下列波形(见坐标纸)

五、VHDL程序代码及注释

串行检测:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitychuanis

port(

vcc,clk:

instd_logic;

output:

outstd_logic_vector(6downto0));

endchuan;

architecturetaoofchuanis

signalsignalout:

std_logic;

signalsignalcomposer:

integerrange0to14;

signalsignalaccept:

std_logic_vector(6downto0);

signaltmp:

integerrange0to4999999;

signalsignaltest:

signalos:

signaltestout:

std_logic;

signalcontrolcout:

signalfinalout:

typestate_typeis(s0,s1,s2,s3,s4);

signalstate:

state_type;

--signaltest:

std_logic_vector(6downto0);

begin

p0:

process(clk)

begin

ifclk'

eventandclk='

1'

then

iftmp=4999999then

tmp<

=0;

else

=tmp+1;

endif;

endprocessp0;

p7:

process(tmp)

os<

='

;

elseos<

0'

endprocessp7;

--p0andp7shifenpinmokuai

p1:

process(os)

ifos'

eventandos='

ifsignalcomposer=14then

signalcomposer<

=signalcomposer+1;

casesignalcomposeris

when4|5|6|8|9|12|14=>

signalout<

whenothers=>

endcase;

endprocessp1;

--youjishiqishixiandexuliefashengqi

p2:

process(signalout)

signalaccept(6)<

=signalaccept(5);

signalaccept(5)<

=signalaccept(4);

signalaccept(4)<

=signalaccept(3);

signalaccept(3)<

=signalaccept

(2);

signalaccept

(2)<

=signalaccept

(1);

signalaccept

(1)<

=signalaccept(0);

signalaccept(0)<

=signalout;

endprocessp2;

--yicunqishixianchuanbingzhuanhuan

p3:

process(signalaccept)

--ifclk'

finalout<

=signalaccept;

--endif;

endprocessp3;

--shuchu

p4:

iftestout='

signaltest<

=vcc;

controlcout<

endprocessp4;

--kongzhishuchu

p6:

if(os'

)then

casestateis

whens0=>

if(signalout='

)thenstate<

=s1;

elsestate<

=s0;

testout<

whens1=>

=s2;

whens2=>

=s3;

whens3=>

=s4;

whens4=>

endprocessp6;

--chuanxinjiance11000

p5:

process(signaltest,signalaccept)

if(signaltest='

)then

output<

=notsignalaccept;

endprocessp5;

--jiucuo

--p6:

process(signa

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 串行口 数据传输 仿真 硬件 实现

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《巴黎圣母院》3000字读书心得范文.docx

《巴黎圣母院》3000字读书心得范文.docx