CMOS二级运算放大器设计Word文档格式.docx

CMOS二级运算放大器设计Word文档格式.docx

- 文档编号:14784565

- 上传时间:2022-10-24

- 格式:DOCX

- 页数:10

- 大小:450.08KB

CMOS二级运算放大器设计Word文档格式.docx

《CMOS二级运算放大器设计Word文档格式.docx》由会员分享,可在线阅读,更多相关《CMOS二级运算放大器设计Word文档格式.docx(10页珍藏版)》请在冰豆网上搜索。

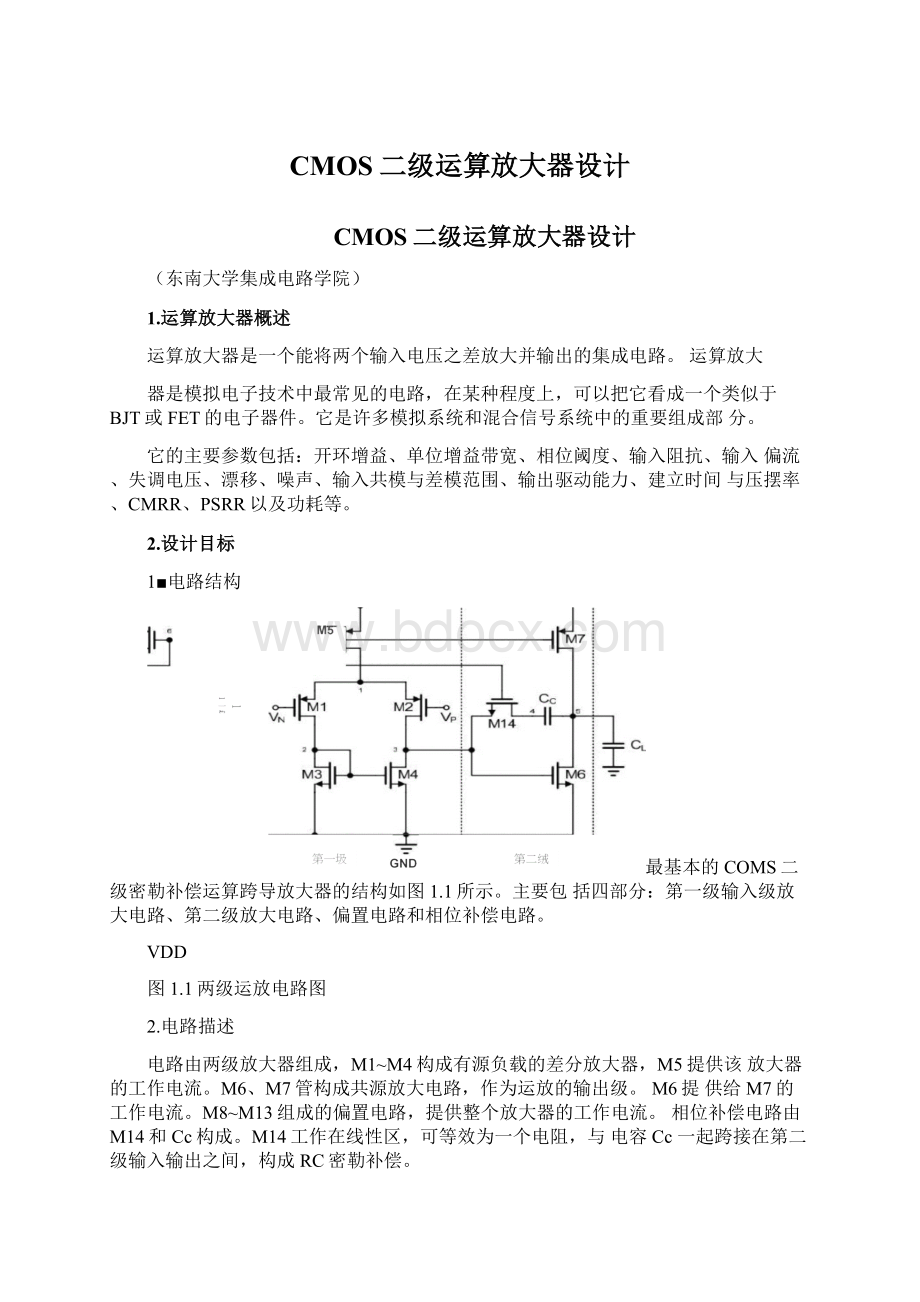

M14工作在线性区,可等效为一个电阻,与电容Cc一起跨接在第二级输入输出之间,构成RC密勒补偿。

3■设计指标

两级运放的相关设计指标如表1。

电源电压

0~5V

共模输入电压

固定在(VDD+VSS)/2

开环直流增益

>

80dB

单位增益带宽

30MHz

相位裕度

60degree

转换速率

30V/卩s

静态功耗(电流)

<

1mA

负载电容

=3pf

表1两级运放设计指标

3.电路设计

第一级的电压增益:

A二gm2(r°

2l|r°

4)(3.1)

第二级电压增益:

A2二-Gm2R2二gm6(r°

6||「。

7)(3.2)

所以直流开环电压增益:

Ao=AA2--gm2gm6(r°

2||r°

4)(r°

6||r°

7)(3.3)

单位增益带宽:

GBWAOfd(3.4)

2兀Q

偏置电流:

根据系统失调电压:

转换速率:

相位补偿:

以上公式推导过程简略,具体过程可参考相关专业书籍。

根据这些公式关系,经过手算得到一个大致的器件参数如表2。

M1

120/1

M9

3.2/1

M2

M10

6/1

M3

40/1

M11

M4

M12

24/1

M5

16/1

M13

M6

160/1

M14

20/1

M7

32/1

Cc

1.5pf

M8

Rb

6KQ

表2二级运放器件参数

四.HSPICE仿真

根据已经计算好的器件参数,写成电路网表。

.titletest

•libE:

\h05mixddst02v231.libtt

vddvdd05

vssvss00

.subcktopampvnvpoutvddvss

ml2vn11mpw=120ul=1u

m23vp11mpw=120ul=1u

m322vssvssmnw=40ul=1u

m432vssvssmnw=40ul=1u

m516vddvddmpw=16ul=1u

m6out3vssvssmnw=160ul=1u

m7out6vddvddmpw=32ul=1u

*biascircuit

m866vddvddmpw=3.2ul=1u

m976vddvddmpw=3.2ul=1u

m10678vssmnw=6ul=1u

m11779vssmnw=6ul=1u

m128910vssmnw=24ul=1u

m1399vssvssmnw=6ul=1u

rb10vss6k

*miller

cc4out1.5p

cloutvss3p

m14473vssmnw=20ul=1u

.ends

x1vnvpoutvddvssopamp*ADM

x2vpvpout1vddvssopamp*ACM

x3out2viout2vddvssopamp*SRx4vnvnout3vdcvssopamp*pPSRR

x5vnvnout4vddvscopamp*nPSRRvpvp0dc2.5ac1

vnvn0dc2.5

vivi0pulse(2320ns0.1ns0.1ns200ns400ns)vdcvdc0de=5ac=1v

vsevsc0ac=1v

.acdec101k100meg

.trans1n400n

.ptintacv(vout)v(3)

.printtransv(out2)

.printacvdb(out)vp(out)

.printacvdb(out1)

.printacvdb(out3)

.printacvdb(out4)

.measureacGBWwhenvdb(out)=0.measureacVPWwhenvp(out)=-120.op

.end

1■直流增益、带宽和相位裕度

把ac信号全部放在一个输入端(或正端或负端),使用Hspice分析输出增益和相位裕度。

差模放大测试电路如图4.2。

vac

图4.2差模增益测试电路图

对应的网表是:

将vac=1V,这样得到的输出电压值就是增益值,方便观察。

仿真得到的差模增

益和相位裕度如图所示。

分别扫描了100Mhz和1Ghz情况下的波形如图4.3和4.4。

图4.3lOOMhz带宽扫描差模增益和相位波形

为了得到准确的直流增益值,单位增益带宽和相位裕度值,通过以下两条语句:

.measureacGBWwhenvdb(out)=0

.measureacVPWwhenvp(out)=-120

观察.lis文件,发现直流增益为80.4288dB,单位增益带宽为52.036Mhz,相位裕

度为65degrea

******acanalysistnonF

25.000tenip=25.000水****

freq

voltdb

voltphase

out

1.00000k

80.4288

-10.6762

1.25893k

80.3425

-13-3513

1.58489k

80.2092

-16-6355

1.99526k

r>

hb-SAl

80.0058

rt'

斗4

-20-6139

HLS六W

y

gbw=

5.2036E+07

vp沪

6.3347E+07

共模放大测试电路如图4.5

图4.5共模增益测试电路图

x2vpvpoutlvddvssopamp*ACM

.printacvdb(outl)

共模增益波形如图4.6。

共模增益在OdB以下说明具有较好的共模抑制共模抑制比如图4.7:

共模抑制比达到83dB

2■电源抑制比

图4.8为电源和地到输出增益的测试电路图,用差模增益除以电源增益即得电源抑制比。

图4.9为仿真得到的正、负电源抑制比,从图中可知,低频时正电源抑制比为98dB,负电源抑制比为89dB。

图4.8电源增益测试电路图

图4.9仿真的电源抑制比

3■压摆率

将运放接成单位增益负反馈形式,如图4.10所示。

对输入施加正负阶跃信号,得到阶跃特性如图4.11所示,给输出负载充电时的压摆率为30.44V/放电时的压摆率大约为44.78V/us

对应的网表:

x3out2viout2vddvssopamp*SR

vivi0pulse(2320ns0.1ns0.1ns200ns400ns)

.trans1n400n.printtransv(out2)

图4.10压摆率测试电路图

设计指标

实际值

80.4288dB

52.036Mhz

65degree

30.44V/卩s

300uA

3pf

通过比较设计指标与实际值,满足系统要求的设计要求

图4.11仿真的瞬态建立特性

五.总结

进行模拟IC设计的第一步是根据要求确定需要的电路结构,第二步是掌握

这种结构的原理和参数之间的联系,第三步根据指标手算电路参数,这个参数只是初步仿真值,可能无法达到系统指标,然后需要手工调整相关参数。

如果始终无法满足,就需要重新考虑电路结构是否合适,初始参数设置是否合适。

通过这些调整最终满足要求。

参考文献

[1]钟文耀.CMOS电路模拟与设计-基于Hspice[M].北京:

科学出版社,2007.

[2]尹睿.二级密勒补偿运算放大器设计教程[M].上海:

复旦大学出版社,2007

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- CMOS 二级 运算放大器 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《巴黎圣母院》3000字读书心得范文.docx

《巴黎圣母院》3000字读书心得范文.docx