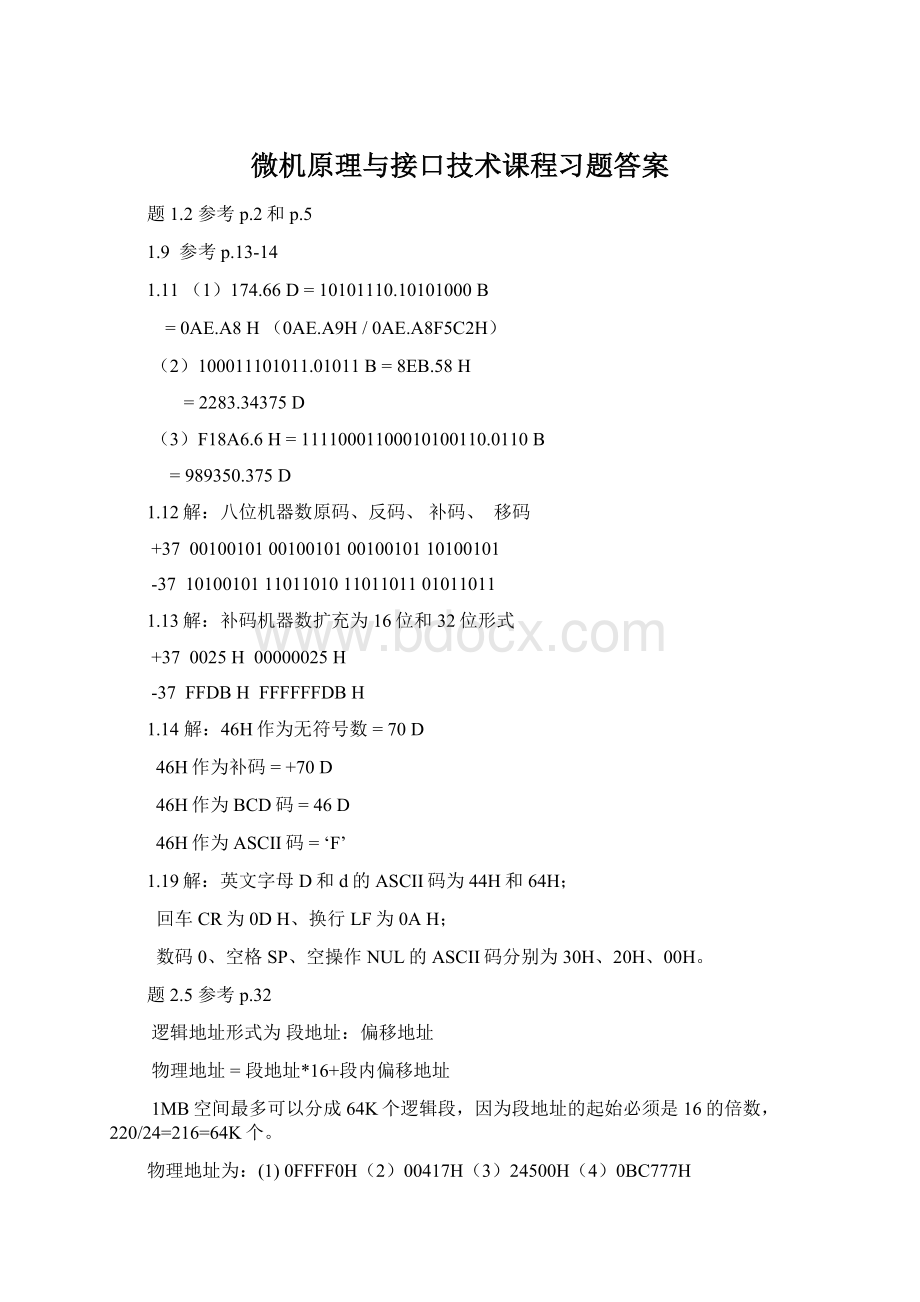

微机原理与接口技术课程习题答案Word文件下载.docx

微机原理与接口技术课程习题答案Word文件下载.docx

- 文档编号:14717366

- 上传时间:2022-10-24

- 格式:DOCX

- 页数:33

- 大小:234.39KB

微机原理与接口技术课程习题答案Word文件下载.docx

《微机原理与接口技术课程习题答案Word文件下载.docx》由会员分享,可在线阅读,更多相关《微机原理与接口技术课程习题答案Word文件下载.docx(33页珍藏版)》请在冰豆网上搜索。

英文字母D和d的ASCII码为44H和64H;

回车CR为0DH、换行LF为0AH;

数码0、空格SP、空操作NUL的ASCII码分别为30H、20H、00H。

题2.5参考p.32

逻辑地址形式为段地址:

偏移地址

物理地址=段地址*16+段内偏移地址

1MB空间最多可以分成64K个逻辑段,因为段地址的起始必须是16的倍数,220/24=216=64K个。

物理地址为:

(1)0FFFF0H

(2)00417H(3)24500H(4)0BC777H

2.9略

2.13解:

运算公式为[v-(x*y+z-540)]/x

结果商存放在ax中,余数在dx中。

2.16解:

求有效地址

(1)EA=1256H

(2)EA=32F7H

2.19解:

求首地址为array的20个字的数组的元素之和,结果存放于地址为total的字单元中。

---------------------------

题4.1参见p.14-15

8088具有20根地址线。

在访问内存时使用地址A0~A19,可直接寻址1MB容量的内存范围;

在访问外设时使用地址线A0~A15,共能寻址64K个输入输出端口。

实际上PC/XT在寻址外设时,只使用地址线A9~A0;

若A9=1,说明它要寻址的IO端口位于IO插卡上。

4.2参见p.106-107

总线操作指的是发生在总线上的某些特定操作,总线周期指的是完成一次特定总线操作所需的时间。

对8088而言其典型的总线周期由4个T状态组成。

PC/XT所采用的时钟频率为4.77MHz,每个T状态的持续时间为210ns。

如果CLK引脚接5MHz的时钟信号,那么每个T状态的持续时间为200ns。

4.4解答:

当8088进行读写存储器或I/O接口时,如果存储器或I/O接口无法满足CPU的读写时序(来不及提供或读取数据时),需要CPU插入等待状态TW。

(在T3前沿检测Ready信号,若无效则插入TW。

)

具体在读写总线周期的T3和T4之间插入TW。

4.6参见p.99,p.110

8088的某些输出线有三种状态:

高电平、低电平、悬空(高阻态),称为三态能力。

在高阻状态,CPU放弃其了对该引脚的控制权,由连接它的设备接管。

具有三态能力的引脚有:

AD7~AD0,A15~A8,A19/S6~A16/S3,ALE,IO/M*,WR*,RD*,DEN*,DT/R*。

4.11

总线周期

IO/M*

WR*

RD*

存储器读

低

高

低

存储器写

I/O读

I/O写

4.12答:

取该指令时引发存储器读总线操作。

执行该指令时引发I/O读总线操作。

(时序图略)

4.138088系统最小组态下,对指令ADD[2000H],AX(长度3B)。

答:

取该指令时需要3个总线周期,均为存储器读周期。

执行该指令时需要4个总线周期,2个为存储器读总线周期(读出字操作数参与运算),2个为存储器写总线周期(保存16位运算结果)。

4.15参见p.106图

74LS373的G为电平锁存引脚,控制选通且转为无效时锁存数据。

OE*输出允许引脚,信号来自ALE。

4.16参见p.106图

数据收发器74LS245是8位双向缓冲器,G*控制端为低电平有效,可传输数据;

DIR控制导通方向:

DIR=1,A→B;

DIR=0,A←B。

4.17参见p.111-112

归纳为:

1、8086数据总线变为16位,数据地址线复用为AD15~AD0。

2、8086指令队列程度变为6字节长,当有2个字节空才取下一指令。

3、8088引脚IO/M*,8086变为M/IO*;

4、引脚SS0*变为BHE*/S7,BHE*的作用是使D15~D8有效。

5、8086存储器组织为奇偶分块,偶地址取字只要读1次,奇地址取字需要读两次。

6、I/O端口大都采用偶地址,目的是引导8位数据到低8位总线AD7~AD0上,以提高效率。

=========================

5.1

Cache、主存和辅存的作用——参见p.120~121

虚拟存储器——参见p.121

在CPU看来,访问主存和访问辅存有什么不同?

访问主存:

通过存储器访问机器指令,按字随机访问。

访问辅存:

通过操作系统,按块顺序访问。

5.2在半导体存储器中,RAM指的是随机存取存储器,它可读可写,但断电后信息一般会丢失;

而ROM指的是只读存储器,正常工作时只能从中读取信息,但断电后信息不会丢失。

以EPROM芯片2764为例,其存储容量为8K×

8位,共有8条数据线和13条地址线。

用它组成64KB的ROM存储区共需8片2764芯片。

5.4一个容量为4K×

4位的假想RAM存储芯片,他应该有多少根地址线引脚和多少根数据线引脚?

如果让你来进行设计,那么它还需要哪些控制引脚?

这些引脚分别起什么样的控制作用?

解答:

4K×

4的芯片应该有12根地址线引脚和4根数据线引脚。

控制引脚应该有:

读取信号OE*:

有效时,表示读取存储单元的数据

写入信号WE*:

有效时,表示将数据写入存储单元

片选信号CS*:

有效时,表示选中该芯片,可以进行读写操作。

5.7什么是存储芯片的位扩充和地址扩充?

采用静态RAM的芯片2114(1K*4位)或动态RAM的芯片4116(16K*1位)来组成32KB的RAM存储区,请问各需要多少芯片?

在位方向和地址方向各需要进行什么样的扩充?

(参见p.140)使用多个芯片来扩充存储数据位的宽度,称为位扩充。

采用多个芯片在地址方向上进行扩充,称为地址扩充或字扩充。

用SRAM2114组成32KBRAM存储区:

2片为一组,得1KB,所以组成32KB就要32组,共需要64片SRAM2114。

用DRAM4116组成32KBRAM存储区:

8片为一组,得16KB,所以组成32KB只要2组,共需要16片DRAM4116。

5.8存储芯片为什么要设置片选信号?

它与系统地址总线有哪些连接方式?

采用何种连接方式可避免地址重复?

采用哪些连接方式可节省用于译码的硬件?

片选信号说明该存储器芯片是否被选中正常工作,设置它可以比较方便地实现多个存储器芯片组成大容量的存储空间。

存储器片选信号通常与CPU地址总线的高位地址线相关联,可以采用“全译码”、“部分译码”、“线选译码”方式。

采用全译码方式可以避免地址重复。

采用部分或线选译码可以节省译码硬件。

5.9在一个针对存储器的译码系统中,如果有4个地址线未参与译码,那么每个存储单元会同时拥有几个地址?

理论上每个存储单元会同时拥有16个地址。

5.10解答:

p.144图5.33中4个存储芯片的可用地址范围:

6264

(1)

6264

(2)

2732

(1)

2732

(2)

00000~01FFFH

02000~03FFFH

04000~04FFFH

05000~05FFFH

40000~41FFFH

42000~43FFFH

44000~44FFFH

45000~45FFFH

80000~81FFFH

82000~83FFFH

84000~84FFFH

85000~85FFFH

C0000~C1FFFH

C2000~C3FFFH

C4000~C4FFFH

C5000~C5FFFH

重复地址由于A19A18的不定性,每片各有4段范围。

5.11采用全译码方式和6264芯片(SRAM,容量8K×

8位),在内存40000H~43FFFH区段扩充RAM,请画出这些芯片与最大组态的系统总线的连接示意图。

解:

方法为:

容量=末地址-首地址+1=214=16KB,所以要2片6264芯片。

A12~A0为片内地址,A15~A13作片选译码的输入CBA,

A19~A16

A15~A13

A12~A0

地址范围

1

2

0100

000

001

全0~全1

40000H~41FFFH

42000H~43FFFH

5.13采用3:

8译码器74LS138和2764芯片(EPROM,8K×

8位),通过全译码方式在8088系统的地址最高端组成32KB的ROM区,请画出各2764芯片与8088最大组态下形成的线条总线的连接示意图。

注意地址最高端组成32KB的ROM区,意味着地址范围是F8000H~FFFFFH,这样最高五根地址线A19~A15上要全为1。

2764芯片的片内地址是13根即A12~A0,它们是全0到全1变化;

现在需要4片来构成32KB存储区,采用3:

8译码器的话,A15~A13应该取后4种情况,即取100~111分别产生Y4~Y7。

其余地址线可以以多种方式组合产生控制信号。

3

4

1111

100

101

110

111

F8000H~F9FFFH

FA000H~FBFFFH

FC000H~FDFFFH

FE000H~FFFFFH

考虑:

如果要求地址从低端开始的话,高5位全0,即00000H~07FFFH,如何连接?

5.16

访问的局部性原则

——P122第1行。

高速缓存和虚拟存储的目的

——p121下部。

=======================

6.1在80x86系统中,I/O端口的地址采用独立编码方式,访问端口时要使用专门的I/O指令,有2种寻址方式,其具体形式是:

直接寻址和DX间接寻址。

6.2一般的I/O接口电路安排有哪三类寄存器?

他们各自的作用是什么?

(参见p.154)

⑴数据寄存器

保存外设给CPU和CPU发往外设的数据。

⑵状态寄存器

保存外设或接口电路的状态。

⑶控制寄存器

保存CPU给外设或接口电路的命令。

6.4

K0单独按下:

输入0FEH,控制L0—〉L7依次循环亮灯,

K1单独

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 微机 原理 接口 技术 课程 习题 答案

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls