VHDL序列检测器Word格式.docx

VHDL序列检测器Word格式.docx

- 文档编号:14589016

- 上传时间:2022-10-23

- 格式:DOCX

- 页数:12

- 大小:72.78KB

VHDL序列检测器Word格式.docx

《VHDL序列检测器Word格式.docx》由会员分享,可在线阅读,更多相关《VHDL序列检测器Word格式.docx(12页珍藏版)》请在冰豆网上搜索。

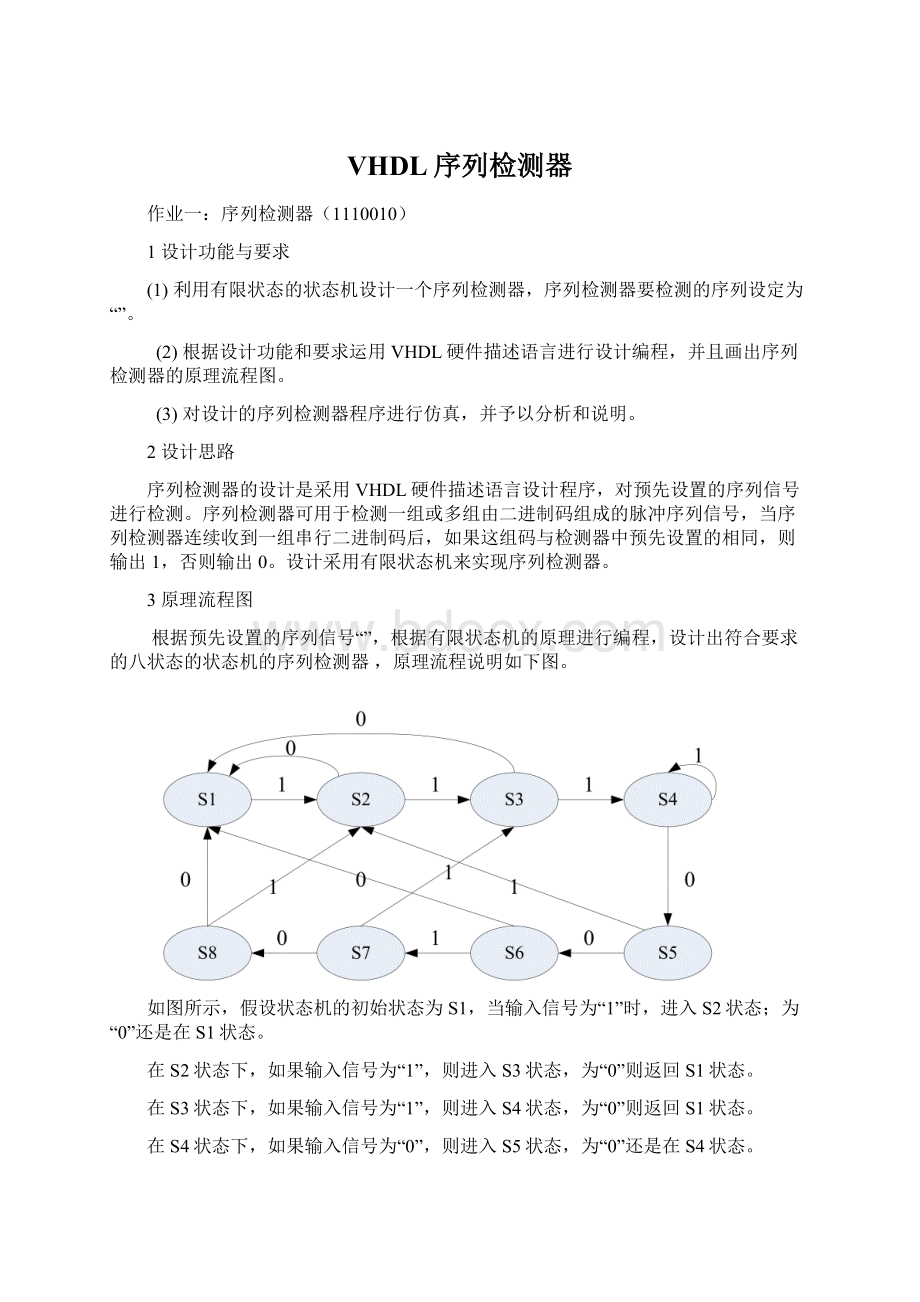

在S3状态下,如果输入信号为“1”,则进入S4状态,为“0”则返回S1状态。

在S4状态下,如果输入信号为“0”,则进入S5状态,为“0”还是在S4状态。

在S5状态下,如果输入信号为“0”,则进入S6状态,为“1”则进入S2状态。

在S6状态下,如果输入信号为“1”,则进入S7状态,为“0”则返回S1状态。

在S7状态下,如果输入信号为“0”,则进入S8状态,为“1”则进入S3状态。

在S8状态下,如果输入信号为“1”,则进入S2状态,为“0”则返回S1状态,并输出序列信号1110010。

4序列检测器VHDL程序代码

在序列检测器的程序代码中采用cin表示输入序列信号,clr为复位控制信号,clk为时钟信号,cout为输出信号。

当检测到序列信号中出现““序列的时候,cout输出为高电平,否则为低电平,详细程序代码如下。

libraryieee;

useieee.std_logic_1164.all;

entitysq_detis

port(cin,clr,clk:

instd_logic;

cout:

outstd_logic);

endsq_det;

architecturebehavofsq_detis

typestateis(s1,s2,s3,s4,s5,s6,s7,s8);

signalc_state,n_state:

state;

begin

process(clk,clr)

begin

if(clr='

1'

)then

c_state<

=s1;

elsif(clk'

eventandclk='

)

thenc_state<

=n_state;

endif;

endprocess;

process(c_state,cin)

begin

case(c_state)is

whens1=>

cout<

='

0'

;

if(cin='

n_state<

=s2;

else

endif;

whens2=>

=s3;

whens3=>

=s4;

else

n_state<

whens4=>

=s5;

whens5=>

=s6;

whens6=>

=s7;

else

whens7=>

)then

=s8;

whens8=>

endcase;

endarchitecturebehav;

5仿真结果与说明

序列检测器程序仿真结果如下图,cin为输入序列信号,clr为复位控制信号,高电平复位清零准备进入工作状态,clk为时钟信号,cout为输出信号。

当检测到序列信号cin中出现““序列的时候,cout输出为高电平。

当没有出现“”序列时,cout输出低电平,如下如所示。

作业二:

三位任意二值序列检测器

(1)利用有限状态的状态机设计一个序列检测器,序列检测器可以检测输入序列中的任意一个3位2进制数。

序列检测器可用于检测任意三位2进制数,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的相同,则输出1,否则输出0。

4.RTL级表示

5.程序

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYdetect_3IS

PORT(Din:

INSTD_LOGIC;

Clk:

reset:

Dout_000,Dout_001,Dout_010,Dout_011,Dout_100,Dout_101,

Dout_110,Dout_111:

OUTSTD_LOGIC

);

ENDdetect_3;

ARCHITECTURERTLOFdetect_3IS

TYPESTATEIS(S0,S1,S2,S3,S4,S5,S6,S7,S8,S9,S10,S11,S12,S13,S14);

SIGNALpre_state,next_state:

STATE;

BEGIN

PROCESS(Din,pre_state)--InputCombinationalLogic

BEGIN

CASEpre_stateIS

WHENS0=>

IF(Din='

)THEN

next_state<

=S2;

ELSE

=S1;

ENDIF;

WHENS1=>

=S4;

=S3;

WHENS2=>

=S6;

=S5;

WHENS3=>

=S8;

=S7;

WHENS4=>

=S10;

=S9;

WHENS5=>

=S12;

=S11;

WHENS6=>

=S14;

=S13;

WHENS7=>

WHENS8=>

WHENS9=>

WHENS10=>

WHENS11=>

WHENS12=>

WHENS13=>

WHENS14=>

ENDCASE;

ENDPROCESS;

PROCESS(Clk,reset)

BEGIN

IF(reset='

pre_state<

=s0;

ELSIF(clk'

pre_state<

=next_state;

ENDIF;

PROCESS(pre_state)

IF(pre_state=S7)THEN

Dout_000<

ELSE

IF(pre_state=S8)THEN

Dout_001<

IF(pre_state=S9)THEN

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- VHDL 序列 检测器

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整版)固定资产盘点表.xls

(完整版)固定资产盘点表.xls