四川大学《数字电子技术》期末考试必备通关指导Word文件下载.docx

四川大学《数字电子技术》期末考试必备通关指导Word文件下载.docx

- 文档编号:14520003

- 上传时间:2022-10-23

- 格式:DOCX

- 页数:24

- 大小:419.67KB

四川大学《数字电子技术》期末考试必备通关指导Word文件下载.docx

《四川大学《数字电子技术》期末考试必备通关指导Word文件下载.docx》由会员分享,可在线阅读,更多相关《四川大学《数字电子技术》期末考试必备通关指导Word文件下载.docx(24页珍藏版)》请在冰豆网上搜索。

而A0⊙B0=()。

A、0,0B、0,1C、1,0D、1,1

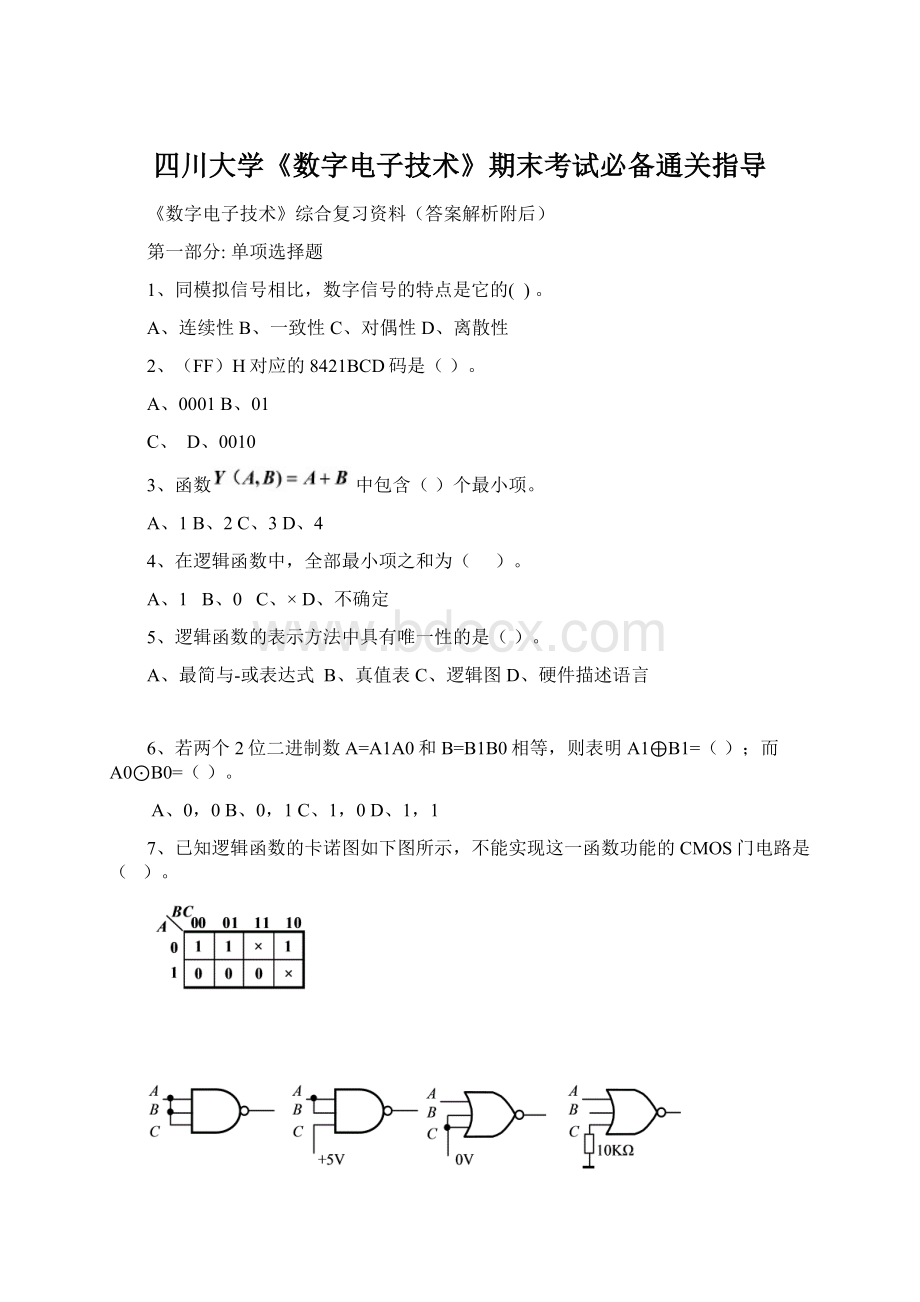

7、已知逻辑函数的卡诺图如下图所示,不能实现这一函数功能的CMOS门电路是()。

A、B、C、D、

8、可以通过()来消除组合逻辑电路竞争冒险。

A、增加冗余项B、减少冗余项C、增加变量D、减少变量

9、下图为双四选一数据选择器74HC153构成的组合逻辑电路,输入变量为A、B、C,输出逻辑函数F1(A,B,C)、F2(A,B,C)的表达式和电路的逻辑功能分别为()。

A、F1=∑m(1,2,4,7),F2=∑m(3,5,6,7),全加器

B、F1=∑m(1,2,4,7),F2=∑m(1,3,6,7),全减器

C、F1=∑m(1,2,4,7),F2=∑m(4,5,6,7),全加器

D、F1=∑m(1,2,3,7),F2=∑m(3,5,6,7),全减器

10、下图为八选一数据选择器构成的组合逻辑电路,输入变量为A、B、C、D,输出逻辑函数F的表达式为()。

A、F(A,B,C,D)=∑m(4,8,9,13);

B、F(A,B,C,D)=∑m(6,8,9,13);

C、F(A,B,C,D)=∑m(6,7,8,9,12,15);

D、F(A,B,C,D)=∑m(6,8,13,14,15);

11、中的多余项是()。

12、下列各种门电路中,输入信号既可以是数字信号又可以是模拟信号的是()。

A、TSL门B、TTL门C、OD门D、CMOSTG门

13、优先编码器同时有两个及以上有效输入信号时,按输入信号的()编码。

A、优先级B、大小C、高电平D、低电平

14、右图为全加器逻辑符号,当0,0,1时,Ci和Si分别为()。

A、

B、

C、

D、

15、七段显示译码器,当译码器七个输出端状态为abcdefg=0110011时(高电平有效),

输入为()。

A、0011B、0110C、0100D、0111

16、电路下图所示。

已知输入X、Y波形,输出Q的波形应为()。

触发器的初始状态为0。

17、欲将一个移位寄存器中的二进制数乘以(32)10,需要()个CP脉冲?

A、32B、5C、10D、16

18、某512位串行输入串行输出右移寄存器,已知时钟频率为4MHZ,数据从输入端到达输出端被延迟()。

A、128µ

sB、256µ

sC、512µ

sD、1024µ

s

19、用异步清零计数器7416l连接成下列计数器,其进制数为()。

A、九进制计数器B、十进制计数器

C、十一进制计数器D、十二进制计数器

2021进制集成加计数器,通过异步置数端构成N(N<

M)进制加法计数器,若预置数据为0,则应将()所对应的状态译码后驱动控制端。

A、MB、N-1C、ND、N+1

21、下列描述不正确的是()。

A、译码器、数据选择器、EPROM均可用于实现组合逻辑函数

B、寄存器、存储器均可用于存储数据

C、移位寄存器首尾相连可构成环形计数器

D、上面描述至少有一个不正确

22、下列存储器中,()存储器在掉电后仍能保证所存的数据不丢失。

A、SRAMB、SSRAMC、DRAMD、E2PROM

23、美国Atmel公司生产的128K×

8位的OTPEPROM芯片,有()条地址总线,8条数据线,欲将它扩展成容量为256K×

32位的存储系统,则需要()片该芯片。

A、7,8B、17,8C、17,4D、7,8

24、一个ROM有16根地址输入线,8根数据输出线(位线),该ROM的存储容量为()。

A、216×

8B、28×

16

C、16×

8D、162×

8

25、多谐振荡器可产生()信号。

A、正弦波B、矩形脉冲C、三角波D、锯齿波

26、以下各电路中,()可以产生定时脉冲。

A、多谐振荡器B、施密特触发器

C、单稳态触发器D、石英晶体多谐振荡器

27、施密特触发器是()触发器。

A、单稳B、双稳C、无稳D、边沿

28、由555定时器构成的施密特触发器,改变控制电压VIC时,则()改变。

A、回差电压ΔVT

B、输出电压VO的高电平值

C、输出电压VO的低电平值

D、输出电压VO的幅值范围

29、8位D/A转换器当输入数字量只有最高位为高电平时输出电压为5V,若只有最低位为高电平,则输出电压约为()。

若输入为,则输出电压约为()。

A、2021,

B、40mV,

C、40mV,

D、80mV,

30、FPGA器件开发系统的组成不含有()。

A、计算机B、开发软件C、编程器D、编程电缆

答案及解析

1-6:

DACABB

7-12:

DAACCD

13-18:

ACCBBA

19-24:

BCDDBA

25-30:

BCBABC

第二部分:

判断题(正确的打√,错误的打×

)

()1、在二进制与十六进制的转换中,有下列关系:

(001)B=(9DF1)H

()2、十进制数10与16相等。

()3、逻辑函数的卡诺图和真值表都具有唯一对应关系,这说明它的最简逻辑函数的表达式也是唯一的。

()4、TTL与非门电路的某一输入端接上10KΩ的大电阻到地,则该输入端相当于接高电平,即逻辑1。

()5、两输入端四与非门器件74LS00与74HC00的逻辑功能完全相同。

()6、三态门的三种状态分别为:

高电平、低电平、不高不低的电压。

()7、利用三态门可以实现数据的双向传输。

()8、n变量逻辑函数,其全部最小项有2n个。

()9、某种门的输入全部为高电平时,输出也为高电平,则这种门一定是与门。

()10、OC门在使用时须在输出与输入之间接一电阻。

()11、OD与非门的输出端可以并联运行,实现“线与”关系,即L=

()12、由与非门构成的都是组合逻辑电路。

()13、使用比较器比较两个二进制数时应先比较最低位。

()14、SR触发器、JK触发器均具有状态翻转功能。

()15、逻辑电路正逻辑体制中,低电平用逻辑0表示,高电平用逻辑1表示。

()16、可编程逻辑器件(programmablelogicdevice即PLD)是由用户通过编程来定义逻辑功能的一种通用集成电路。

()17、HardwareDescriptionLanguage(简称:

HDL)是能对硬件逻辑电路的功能进行描述的一种高级编程语言,主要有VHDL和Verilog两种。

()18、时序电路的输出状态仅与此刻输入变量有关。

()19、SR触发器的约束条件SR=0表示不允许出现R=S=1的输入。

()2021密特触发器可用于将三角波变换成正弦波。

()21、施密特触发器的特点是电路具有两个稳态且每个稳态需要相应的输入条件维持。

()22、在同步时序电路的设计中,若最简状态表中的状态数为2n,而又是用n级触发器来实现其电路,则不需检查电路的自校正性。

()23、D触发器的特性方程为Qn+1=D,与Qn无关,所以它没有记忆功能。

()24、设计异步时序逻辑电路时,需要额外考虑输入信号。

()25、单稳态触发器输出脉冲的宽度是由该电路中的定时元件C、R值来决定的。

()26、D/A转换器是指将模拟信号转换成数字信号的电路。

()27、可用ADC将麦克风信号转换后送入计算机中处理。

()28、A/D转换器的二进制数的位数越多,量化单位△越小。

()29、RAM和ROM基本结构中都有存储阵列,因此都属于时序逻辑电路,RAM与ROM的最大区别是数据的易失性。

()30、555定时器构成的施密特触发器常用于对脉冲波形的整形和产生。

正确选项:

√√×

×

√×

√√√×

√√√√×

第三部分:

分析设计

1、将逻辑函数式P(A,B,C)=∑m(3,5,6,7),化简成最简与或式。

P(A,B,C)=AB+AC+BC

2、化简逻辑函数:

3、逻辑电路如图所示,写出输出F的最简与或表达式。

4、试画出用最少与非门和反相器实现下面函数的逻辑图(只有原变量输入)。

5、A、B均为4位二进制数,试用一片4位加法器74HC283实现Y=4A+B。

(提示:

二进制数每乘一次2,向左移一位,即2×

A3A2A1A0=A3A2A1A00)

Y=4A+B=A3A2A1A000+B3B2B1B0

6、由3/8译码器74HC138和八选一数据选择器74HC151构成电路如图所示,试分析该电路的的逻辑功能。

【电路输入X(X2X1X0)、Z(Z2Z1Z0),电路输出L】

比较电路,当输入相等时输出为0,否则为1。

7、试根据所给图形符号及输入波形画出输出Q的波形,假设初始状态Q=1(画波形时不考虑延迟时间,只需画出CP和Q的波形)。

8、已知电路及CP、A的波形如图(a)和(b)所示,设触发器的初态均为“0”,试写出状态转换方程,画出输出端B和C的波形。

状态转换方程:

,

输出端B和C的波形如图所示。

9、逻辑电路如图所示,列出状态转换方程,已知CP脉冲和输入X的波形,画出输出,的波形(设,的初始状态均为0)。

特性方程:

激励方程组:

状态转换方程组:

波形图:

10、把负边沿JK触发器转换为正边沿D触发器。

写出这2种触发器的特性方程,画出逻辑图。

激励方程:

逻辑图:

11、试写出图示电路的状态转换方程,画出在给定信号的作用下Q的波形,触发器初态为“0”。

在给定信号的作用下,输出Q的波形如下图:

12、用最少与非门设计一个组合逻辑电路,其输入为4位无符号二进制数A(A3A2A1A0)(无反变量输入),当0≤A<8或12≤A<15时,输出F为1,否则,输出F为0。

(1)真值表:

A3

A2

A1

A0

F

1

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 数字电子技术 四川大学 数字 电子技术 期末考试 必备 通关 指导

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls