EDA实验指导书分析Word下载.docx

EDA实验指导书分析Word下载.docx

- 文档编号:14419621

- 上传时间:2022-10-22

- 格式:DOCX

- 页数:11

- 大小:73.63KB

EDA实验指导书分析Word下载.docx

《EDA实验指导书分析Word下载.docx》由会员分享,可在线阅读,更多相关《EDA实验指导书分析Word下载.docx(11页珍藏版)》请在冰豆网上搜索。

1

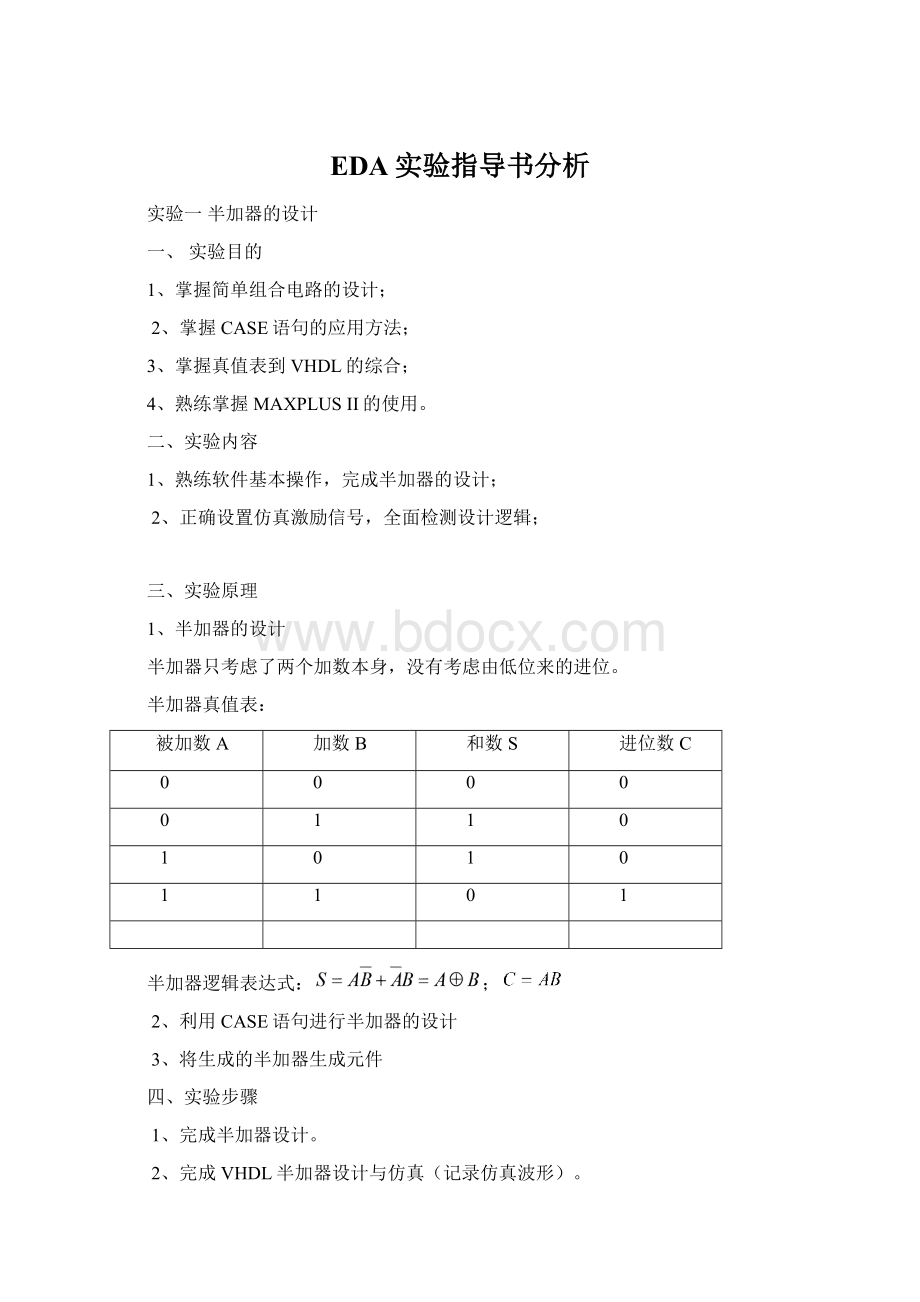

半加器逻辑表达式:

;

2、利用CASE语句进行半加器的设计

3、将生成的半加器生成元件

四、实验步骤

1、完成半加器设计。

2、完成VHDL半加器设计与仿真(记录仿真波形)。

3、生成半加器元件。

五、思考题:

1、怎样自建元件?

自建元件的调用要注意什么?

实验二全加器的设计

二、实验目的

1、掌握图形的设计方式;

2、掌握自建元件及调用自建元件的方法;

3、熟练掌握MAXPLUSII的使用。

1、熟练软件基本操作,完成全加器的设计;

1、全加器的设计

全加器除考虑两个加数外,还考虑了低位的进位。

全加器真值表:

0

全加器逻辑表达式:

2、利用半加器元件完成全加器的设计

图形方式(其中HADDER为半加器元件)

1、完成图形全加器设计。

2、完成VHDL全加器设计与仿真(记录仿真波形)。

3、利用半加器元件进行图形的全加器设计。

附加自选实验二位加法计数器的设计

一、实验目的

1、掌握二位加法计数器的原理;

2、掌握二位加法计数器的VHDL描述。

3、深入理解VHDL中元件例化的意义。

二、实验内容

1、完成带进位功能二位加法计数器的VHDL设计;

3、综合下载,进行硬件电路测试。

1、二位加法计数器中使用了矢量类型的数据,用来表示计数的数值。

2、元件的例化就是元件的调用,是层次化设计的基础。

具体设计程序由学生自己完成。

1、了解二位加法计数器的工作原理。

2、用VHDL文本方式设计二位加法计数器。

3、进行二位加法计数器的设计仿真(记录仿真波形)。

4、进行二位加法计数器的设计下载与测试。

五、思考题

1、怎样设计“减法”计数器?

2、进位信号的设置应注意什么?

实验三十进制计数器的设计

一、实验目的

1、掌握流程控制语句(IF语句和CASE语句)的使用。

2、掌握计数器进制的设置原理。

3、熟练掌握矢量类型数据与进程语句的使用。

4、掌握IF语句的嵌套使用方法,

1、完成多功能十进制加法计数器的VHDL设计。

2、正确设置仿真激励信号,全面检测设计逻辑。

三、实验说明

十进制计数器的VHDL设计的关键在于计数位宽的设置与进制的设置,通常应具有以下功能:

清零、使能、向高位进位。

要注意进位信号的处理,进位信号的脉宽处理与产生时间处理。

1、了解十进制计数器的工作原理。

2、用VHDL文本方式设计十进制加法计数器。

3、进行十进制加法计数器的设计仿真(记录仿真波形)。

4、进行十进制加法计数器的设计下载与测试。

五、实验报告要求及思考题:

1、进制数与计数最大值的关系是什么?

2、能否设计出可改变参数的通用的计数器?

怎样设计?

实验四八位双向移位寄存器的设计

1、掌握八位双向移位寄存器的基本原理。

2、掌握八位双向移位寄存器的VHDL描述。

1、完成八位双向移位寄存器的VHDL设计;

八位双向移位寄存器具有数据左移、右移和预置数功能。

其输出Q和置数输入DATA为八位口;

方式控制输入MODE为2位口。

SL_IN,SR_IN分别为左移输入和右移输入;

CLK为时钟信号(输入);

RESET为复位信号(输入,高电平有效)。

1、了解八位双向移位寄存器的工作原理。

2、用VHDL文本方式设计八位双向移位寄存器。

3、进行八位双向移位寄存器的设计仿真(记录仿真波形)。

4、进行八位双向移位寄存器的设计下载与测试

五、实验报告要求及思考题

1、八位双向移位寄存器的外部引脚在测试时应怎样连接?

实验五数控分频器

1、学会数控分频器的设计、分析和测试方法;

2、根据仿真结果分析设计的优缺点。

二、实验原理

数控分频器的功能就是当输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比。

三、实验内容

1、用VHDL语言写出源程序,输入不同的CLK和预置值D,仿出时序波形;

2、通过编译仿真、波形分析来验证设计;

3、下载验证(用示波器)。

四、实验报告要求

1、写出数控分频器源程序;

2、分析设计和仿真结果;

3、详细叙述数控分频器的工作原理。

1、如何利用2个上述所设计的模块来设计一个电路,使其输出方波的正负脉冲的宽度分别由两个8位输入数据控制?

实验六计数译码显示电路的设计

1、掌握译码电路的设计原理。

2、掌握静态显示和动态显示电路的原理。

3、熟练多进程的VHDL程序设计。

1、完成七段译码器的VHDL设计。

2、完成静态和动态显示电路的VHDL设计。

3、正确设置仿真激励信号,全面检测设计逻辑。

4、综合下载,进行硬件电路测试。

LED显示电路分为静态方式与动态方式两种。

静态方式显示电路的设计比较简单,只需完成七段译码器的设计。

动态方式显示电路除了要完成七段译码器的设计外,还要进行扫描模块的设计。

动态扫描模块要能够输出位选信号和相应的待译码值。

1、了解静态和动态显示电路的工作原理。

2、完成静态显示电路的方案设计和七段译码器的VHDL设计。

3、完成动态扫描模块的VHDL设计。

4、利用七段译码器和动态扫描模块完成动态显示电路的设计。

5、进行设计仿真与下载测试。

1、静态显示与动态显示的区别是什么?

2、动态扫描的时钟频率应怎样设置?

附加实验数码扫描显示电路设计

1、学会数码扫描显示电路的设计;

2、掌握数码扫描显示电路的分析和测试方法;

3、根据仿真结果分析设计的优缺点。

电路有8个数码扫描显示电路,每个数码管的8个段h、g、f、e、d、c、b、a都分别连在一起,通过选通信号选择数码管,被选择的数码管显示数据,其余关闭,8个选通信号独立工作,可以使得8个数码管同时显示,在段信号输入口加上希望在该对应数码管上显示的数据,从而显示。

1、用VHDL语言写出源程序,仿出时序波形;

1、写出数码扫描显示电路源程序;

3、详细叙述数码扫描显示电路的工作原理。

附加实验LPM应用

1、掌握LPM中RAM、ROM等模块参数的设置方法。

2、掌握LPM模块的设计、应用方法。

1、完成基于ROM的4位乘法器设计的设计。

2、正确设置ROM的参数。

LPM即是参数可设置模块库,这些可以以图形或硬件语言模块形式方便调用的宏功能块,使得基于EDA技术的电子设计的效率和可靠性有了很大的提高。

硬件乘法器的设计方法有很多,但相比之下,由高速ROM构成的乘法表达方式的乘法器的运算速度最快。

1、调用LPM下LPM_ROM模块。

2、参数设置,其中地址位宽LPM_WIDTH为8,地址线位宽LPM_WIDTHAD也为8,地址输入由时钟inclock的上升沿来控制,即令LPM_ADDRESS_CONTROL=

”REGISTERED”,输出为非寄存方式,即:

LPM_OUTDATA

=”UNREGISTERED”,最后为ROM配置乘法表数据文件。

3、完成ROM中的数据配制。

4、进行设计仿真与下载测试。

1、如何文本进行调用LPM模块?

附加实验优化设计

l、熟悉状态机(Moore型)的工作原理;

2、用VHDL语言设计状态机电路;

3、学会使用状态机设计电路。

Moore型状态机的输出与状态有关而与输入无关,如以下图所示:

若目前处于S0时,输入为0则状态机将维持状态0不变;

若输入为l则下个状态将改变为Sl,但不论输入是什么,此时输出均为0。

1、用VHDL语言写出源程序。

1、写出状态机的VHDL源程序;

2、详细叙述状态机的工作原理;

3、画出工作时序波形图。

1、状态机两种描述方式的区别?

2、MEALY和MOORE的描述有何不同?

附加实验多路选择器

1.熟练掌握多路选择器的设计方法;

2.用VHDL语言中不同的语句来描述。

四选一多路选择器的原理如下图及下表,由Sl,S0来选择d0,dl,d2,d3的信号,并使其能在Q上输出。

S1

S0

Q

d0

1

d1

d2

d3

X

1、用VHDL语言的不同语句分别描述任务选择器,并通过编译仿真比较不同语句描述的区别。

2、通过仿真下载并通过硬件验证实验结果。

l、写出几种不同的VHDL源程序;

2、画出电路的时序仿真波形;

3、分析不同VHDL语句的优劣;

4、写出设计心得体会。

1、如何设计一个3选1的选择器?

附加实验JK触发器的设计

1、掌握JK触发器的原理;

2、掌握JK触发器的VHDL描述;

3、掌握VHDL中信号的特性与使用方法。

1、完成JK触发器的VHDL设计;

JK触发器是基本的时序电路。

在这次实验中要注意时钟信号的设置与判断,要求设计上升沿触发的JK触发器。

1、了解JK触发器的工作原理。

2、用VHDL文本方式设计一个时

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 实验 指导书 分析

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

转基因粮食的危害资料摘编Word下载.docx

转基因粮食的危害资料摘编Word下载.docx