直流数字电流表的设计Word格式.docx

直流数字电流表的设计Word格式.docx

- 文档编号:14279672

- 上传时间:2022-10-21

- 格式:DOCX

- 页数:12

- 大小:148.16KB

直流数字电流表的设计Word格式.docx

《直流数字电流表的设计Word格式.docx》由会员分享,可在线阅读,更多相关《直流数字电流表的设计Word格式.docx(12页珍藏版)》请在冰豆网上搜索。

数码管

TSEG-MP*4-CC-BLUE

开关

按键开关

电容

C1、C2

33uF

2

电解电容

C3

10uF

电阻

R1

1K

排阻

RP1

200

变阻器

RV1

晶振

X1

1MHz

第二章达到的技术指标

1、可以测量0-5V的8路输入电压值;

2、测量结果可在四位LED数码管上轮流显示后单路选择显示;

3、测量最小分辨率为0.019A;

4、测量误差约为+0.0AV;

第三章数字式电流表的硬件设计

三.1主要元器件的介绍

三.1.1单片机AT89S51

AT89S51是美国ATMEL公司生产的低功耗、高性能CMOS8位单片机。

图4.2和4.3分别为其实物图和内部总体结构图。

AT89S51的引脚

AT89S51芯片为40引脚双列直插式封装,其引脚排列如图4.2所示。

图4.2AT89S51的引脚图

(1)VCC:

电源电压;

(2)GND:

接地;

(3)P0口:

P0口是一组8位漏极开路双向I/O口,每位引脚可驱动8个TTL逻辑门路。

(4)P1口:

P1口是一个内部提供上拉电阻的8位双向I/O口,P1口的输出缓冲器可驱动4个TTL逻辑门电路。

有第二功能,如表4.1所示。

表4.1P1口的第二功能

端口引脚

第二功能

P1.5

MOSI(用于ISP编程)

P1.6

MISO(用于ISP编程)

P1.7

SCK(用于ISP编程)

(5)P2口:

P2口是一个内部提供上拉电阻的8位双向I/O口,P2口的输出缓冲器可驱动4个TTL逻辑门电路。

。

(6)P3口:

P3口是一个内部提供上拉电阻的8位双向I/O口,P3口的输出缓冲器可驱动4个TTL逻辑门电路。

P3口除了一般I/O线的功能外,还具有更为重要的第二功能,如表4.2所示。

P3口同时为FLASH编程和编程校验接收一些控制信号

表4.2P3口的第二功能

P3.0

RXD(串行输入口)

P3.1

TXD(串行输出口)

P3.2

/INTO(外部中断0)

P3.3

/INT1(外部中断1)

P3.4

T0(定时器0外部输入)

P3.5

T1(定时器1外部输入)

P3.6

/WR(外部数据存储器写选通)

P3.7

/RD(外部数据存储器读选通)

(7)RST:

复位输入。

当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。

(8)ALE//RPOG:

当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。

在FLASH编程期间,此引脚用于输入编程脉冲。

(9)/PSEN:

外部程序存储器的选通信号。

在由外部程序存储器取指期间,每个机器周期两次/PSEN有效。

但在访问外部数据存储器时,这两次有效的信号将不出现。

(10)/EA/VPP:

当保持低电平时,则在此期间外部程序存储器(0000H-FFFFH),不管是否有内部程序存储器。

注意加密方式1时,/EA将内部锁定为RESET;

当/EA端保持高电平时,此间内部程序存储器。

在FLASH编程期间,此引脚也用于施加12V编程电源(VPP)。

·

定时器0和定时器1:

AT89S51的定时器0和定时器1的工作方式与AT89C51相同。

定时和计数功能由特殊功能寄存器TMOD的控制位C/T进行选择,这两个定时/计数器有4种操作模式,通过TMOD的M1和M0选择。

其中模式0、1和2都相同,模式3不同。

定时器2:

定时器2是一个16位定时/计数器。

它既可当定时器使用,也可作为外部事件计数器使用,其工作方式由特殊功能寄存器T2CON的C/T2位选择。

定时器2有三种工作方式:

捕获方式,自动重装载(向上或向下计数)方式和波特率发生器方式,工作方式由T2CON的控制位来选择。

定时器2由两个8位寄存器TH2和TL2组成,在定时器工作方式中,每个机器周期TL2寄存器的值加1,由于一个机器周期由12个振荡时钟构成,因此,计数速率为振荡频率的1/12。

在计数工作方式时,当T2引脚上外部输入信号产生由1至0的下降沿时,寄存器的值加1,在这种工作方式下,每个机器周期的5SP2期间,对外部输入进行采样。

若在第一个机器周期中采到的值为1,而在下一个机器周期中采到的值为0,则在紧跟着的下一个周期的S3P1期间寄存器加1。

由于识别1至0的跳变需要2个机器周期(24个振荡周期),因此,最高计数速率为振荡频率的1/24。

为确保采样的正确性,要求输入的电平在变化前至少保持一个完整周期的时间,以保证输入信号至少被采样一次。

可编程时钟输出:

定时器2可通过编程从P1.0输出一个占空比为50%的时钟信号。

P1.0引脚除了是一个标准的I/O口外,还可以通过编程使其作为定时/计数器2的外部时钟输入和输出占空比50%的时钟脉冲。

当时钟振荡频率为16MHz时,输出时钟频率范围为61Hz—4MHz。

UART:

AT89S51的工作方式与AT89C51工作方式相同。

串口为全双工结构,表示可以同时发送和接收,它还具有接收缓冲,在第一个字节从寄存器读出之前,可以开始接收第二个字节。

(但是如果第二个字节接收完毕时第一个字节仍未读出,其中一个字节将会丢失)。

串口的发送和接收寄存器都是通过SFRSBUF进行访问的。

写入SBUF的数据装入发送寄存器,对SBUF的读操作是对物理上分开的接收寄存器进行访问。

该串口有4种操作模式(模式0、模式1、模式2和模式3),在这4种模式中,发送过程是以任意一条写SBUF作为目标寄存器的指令开始的,模式0时接收通过设置R0=0及REN=1初始化,其他模式下如若REN=1则通过起始位初始化。

中断:

AT89S51共有6个中断向量:

两个外中断(INT0和INT1),3个定时器中断(定时器0、1、2)和串行口中断。

这些中断源可通过分别设置专用寄存器IE的置位或清0来控制每一个中断的允许或禁止。

IE也有一个总禁止位EA,它能控制所有中断的允许或禁止。

定时器2的中断是由T2CON中的TF2和EXF2逻辑或产生的,当转向中断服务程序时,这些标志位不能被硬件清除,事实上,服务程序需确定是TF2或EXF2产生中断,而由软件清除中断标志位。

定时器0和定时器1的标志位TF0和TF1在定时器溢出那个机器周期的S5P2状态置位,而会在下一个机器周期才查询到该中断标志。

然而,定时器2的标志位TF2在定时器溢出的那个机器周期的S2P2状态置位,并在同一个机器周期内查询到该标志。

时钟振荡器:

AT89S51中有一个用于构成内部振荡器的高增益反相放大器,引脚XTAL1和XTAL2分别是该放大器的输入端和输出端。

这个放大器与作为反馈元件的片外石英晶体或陶瓷谐振器一起构成自激振荡器,振荡电路。

外接石英晶体(或陶瓷谐振器)及电容C1、C2接在放大器的反馈回路中构成并联振荡电路。

对外接电容C1、C2虽然没有十分严格的要求,但电容容量的大小会轻微影响振荡频率的高低、振荡器工作的稳定性、起振的难易程序及温度稳定性,如果使用石英晶体,我们推荐电容使用30pF±

10pF,而如使用陶瓷谐振器建议选择40pF±

10F。

用户也可以采用外部时钟。

采用外部时钟的电路。

这种情况下,外部时钟脉冲接到XTAL1端,即内部时钟发生器的输入端,XTAL2则悬空。

由于外部时钟信号是通过一个2分频触发器后作为内部时钟信号的,所以对外部时钟信号的占空比没有特殊要求,但最小高电平持续时间和最大的低电平持续时间应符合产品技术条件的要求。

Flash存储器的编程:

AT89S51单片机内部有8k字节的FlashPEROM,这个Flash存储阵列出厂时已处于擦除状态(即所有存储单元的内容均为FFH),用户随时可对其进行编程。

编程接口可接收高电压(+12V)或低电压(Vcc)的允许编程信号。

低电压编程模式适合于用户在线编程系统,而高电压编程模式可与通用EPROM编程器兼容。

·

数据查询:

AT89S51单片机用DataPalling表示一个写周期结束为特征,在一个写周期中,如需读取最后写入的一个字节,则读出的数据的最高位(P0.7)是原来写入字节最高位的反码。

写周期完成后,所输出的数据是有效的数据,即可进入下一个字节的写周期,写周期开始后,DataPalling可能随时有效。

Ready/Busy:

字节编程的进度可通过“RDY/BSY输出信号监测,编程期间,ALE变为高电平“H”后,P3.4(RDY/BSY)端电平被拉低,表示正在编程状态(忙状态)。

编程完成后,P3.4变为高电平表示准备就绪状态。

程序校验:

如果加密位LB1、LB2没有进行编程,则代码数据可通过地址和数据线读回原编写的数据,采用如图12的电路。

加密位不可直接校验,加密位的校验可通过对存储器的校验和写入状态来验证。

芯片擦除:

利用控制信号的正确组合并保持ALE/PROG引脚10mS的低电平脉冲宽度即可将PEROM阵列(4k字节)和三个加密位整片擦除,代码阵列在片擦除操作中将任何非空单元写入“1”,这步骤需再编程之前进行。

三.1.2A/D转换芯片ADC0809

ADC0809是典型的8位8通道逐次逼近式A/D转换器,其实物如图1-3所示。

它可以和微型计算机直接接口。

ADC0809转换器的系列芯片是ADC0808,可以相互替换。

三.1.3ADC0809内部逻辑结构

图4.3ADC0809的内部逻辑结构图

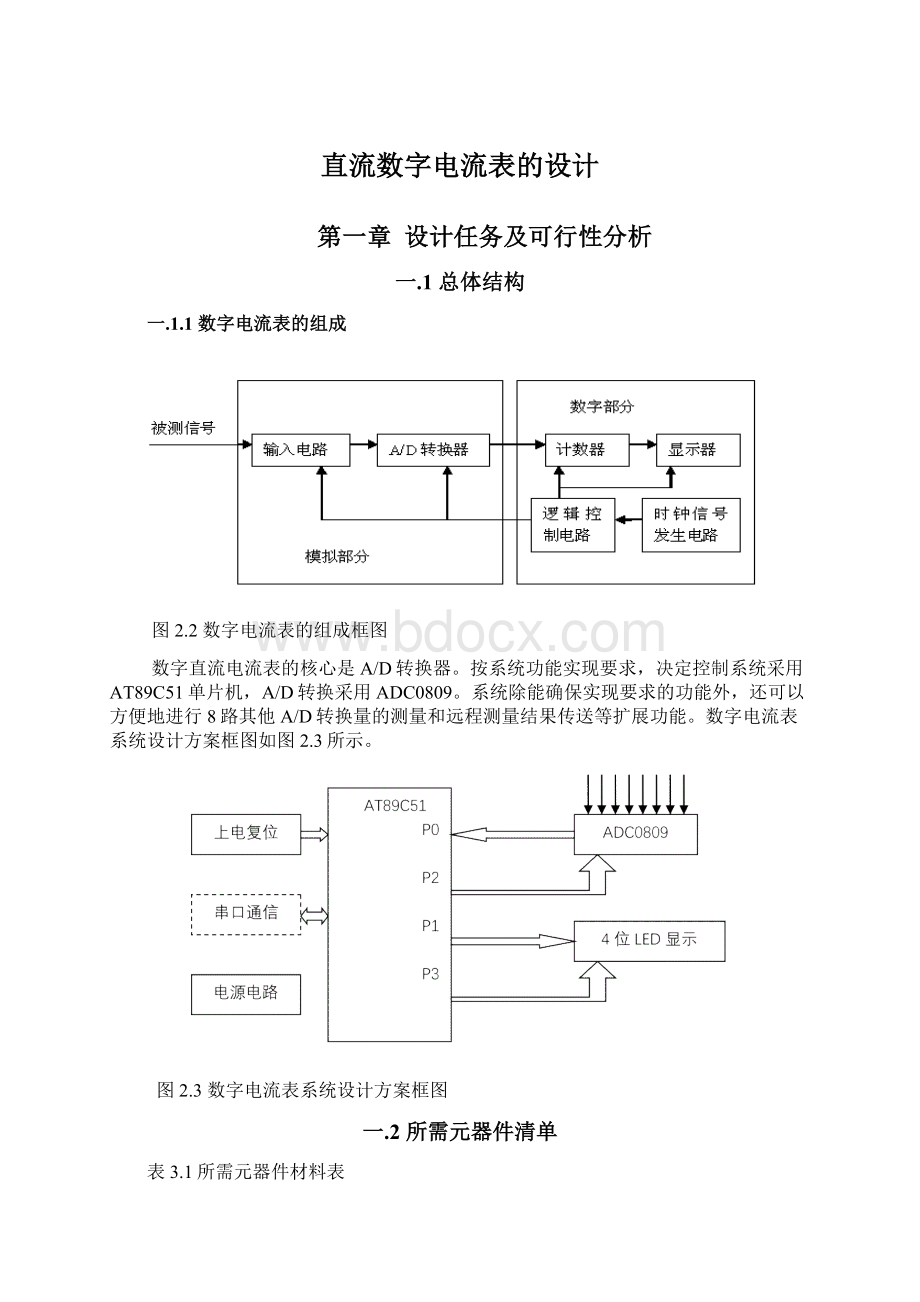

ADC0809的内部逻辑结构如图4.7所示。

图中多路模拟开关可选通8路模拟通道,允许8路模拟量分时输入,并共用一个A/D转换器进行转换。

地址锁存与译码电路完成对A、B、C三个地址位进行锁存与译码,如表4.3所示。

表4.3ADC0809通道选择表

C(ADDC)

B(ADDB)

A(ADDA)

选择的通道

IN0

IN1

IN2

IN3

IN4

IN5

IN6

IN7

三.1.4ADC0809的引脚

ADC0809芯片为28引脚双列直插式芯片,其主要功能:

(1)IN0~IN7:

8路模拟量输入通道。

(2)A、B、C:

模拟通道地址线。

这3根地址线用于对8路模拟通道的选择,其译码关系如表4.3所示。

其中,A为低地址,C为高地址,引脚图中为ADDA,ADDB和ADDC。

(3)ALE:

地址锁存允许信号。

对应ALE上跳沿,A、B、C地址状态送入地址锁存器中。

(4)START:

转换启动信号。

START上升沿时,复位ADC0809;

START下降沿时启动芯片,开始进行A/D转换;

在A/D转换期间,START应保持低电平。

本信号有时简写为ST。

(5)D7~D0:

数据输出线。

为三

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 直流 数字 电流表 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

12处方点评管理规范实施细则_精品文档.doc

12处方点评管理规范实施细则_精品文档.doc

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls

17种抗癌药纳入国家基本医疗保险工伤保险和生育保险药品目录_精品文档.xls