EDA整体教学设计Word文件下载.docx

EDA整体教学设计Word文件下载.docx

- 文档编号:14144411

- 上传时间:2022-10-19

- 格式:DOCX

- 页数:35

- 大小:23.72KB

EDA整体教学设计Word文件下载.docx

《EDA整体教学设计Word文件下载.docx》由会员分享,可在线阅读,更多相关《EDA整体教学设计Word文件下载.docx(35页珍藏版)》请在冰豆网上搜索。

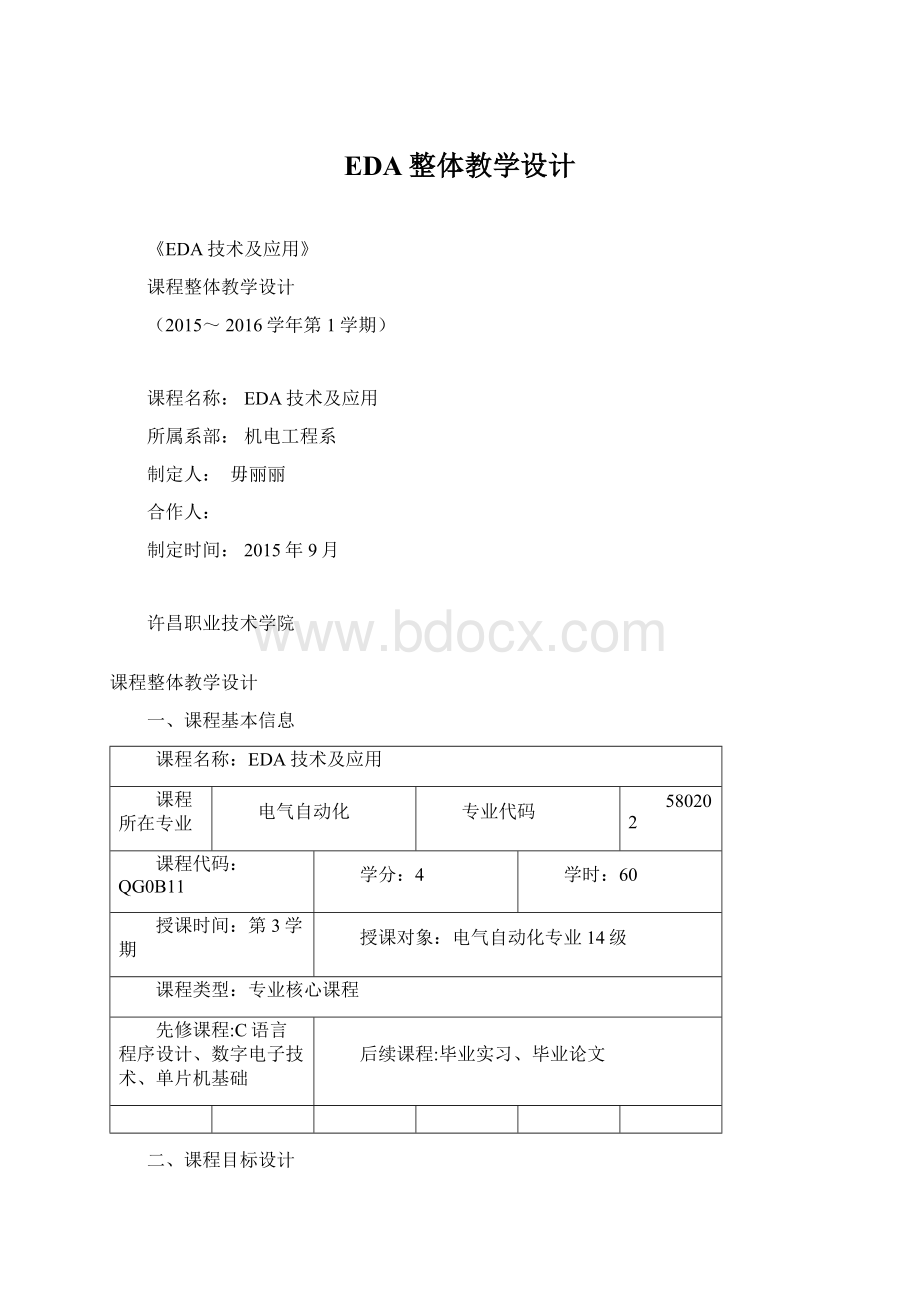

QG0B11

学分:

4

学时:

60

授课时间:

第3学期

授课对象:

电气自动化专业14级

课程类型:

专业核心课程

先修课程:

C语言程序设计、数字电子技术、单片机基础

后续课程:

毕业实习、毕业论文

二、课程目标设计

总体目标:

通过本课程的学习,使学生掌握现代电子技术的设计方法,掌握VHDL语言的基本知识、编程技巧;

使学生具备使用QuartusII软件和VHDL语言设计简单数字电路和系统并进行仿真的能力,具备使用EDA实验箱进行硬件下载、调试的能力。

培养学生良好的操作规范,良好的团队合作精神和务实、上进、刻苦钻研的精神,为未来进一步的学习和工作奠定基础。

能力目标:

1、会安装和破解QuartusII软件;

2、能够使用QuartusII软件设计简单数字电路和系统;

3、能够使用QuartusII软件进行仿真,且会分析仿真结果;

4、能够使用VHDL语言编写简单程序、修改稍复杂程序;

5、能够使用EDA实验箱进行硬件下载、验证、调试;

6、能够对部分FPGA开发的电子系统进行故障检测、维修;

知识目标:

1、了解EDA的应用、发展,FPGA/CPLD芯片的结构、分类、厂商及常用芯片的特点;

2、熟悉可编程逻辑器件的结构、原理和选用原则。

3、掌握QuartusII软件设计简单数字电路和系统的方法;

4、掌握VHDL语言的结构、语法、语句的使用方法和编程技巧;

5、掌握数字电路和系统的功能仿真和时序仿真方法;

6、掌握EDA实验箱的引脚配置、硬件下载、调试方法;

素质目标:

1、具备良好的团队合作能力和专业技术交流能力;

2、具备善于勤于思考,发现问题、解决实际问题的能力;

3、踏实、务实、善于钻研的精神;

4、良好的操作规范和敬业精神;

三、课程内容设计:

序号

模块(或子模块)名称

学时

1

加法器的设计

8

2

四路抢答器的设计

3

电子表决器的设计

译码器的设计

6

5

计数器的设计

10

数字时钟的设计

7

数字频率计的设计

信号发生器的设计

9

交通灯控制器的设计

合计

四、能力训练项目设计

编号

能力训练项目名称

子项目编号、

名称

能力目标

知识目标

训练

方式、

手段及

步骤

可展示的结果

1-1

半加器的设计

1、会安装QuartusII软件。

2、能运用QuartusII软件设计图形文件。

3、能运用软件进行功能仿真并会分析仿真结果。

4、能初步进行引脚配置、实验箱连线,硬件的下载、调试。

5、能简单解决编译、仿真,调试中出现的问题。

1、了解可编程逻辑器件的发展、特点、内部结构、开发流程等。

2、掌握基本门的图形符号和文本符号。

3、掌握图形法设计半加器的方法和步骤。

4、掌握软件的编译和仿真方法。

5、掌握引脚配置、硬件连线下载步骤。

1.教学做一体化

2.示范教学

3.项目导向、任务驱动法

发放任务单,对设计任务分析;

讲解半加器的设计原理,演示半加器的设计步骤,学生设计;

教师巡视、指导、答疑;

结果检查,评价、总结,布置作业

半加器的设计、仿真结果和实验箱显示结果

1-2

全加器的设计

1、能运用文本法、图形法和混合输入的层次化法设计全加器。

2、能进行功能仿真并会分析仿真结果。

3、能进行引脚的配置、实验箱连线,文件的下载和硬件调试。

4、能解决编译、仿真,调试中出现的问题。

1、理解全加器的设计原理并能看懂真值表。

2、掌握文本法、图形法和混合输入的层次化设计方法。

3、掌握软件的功能仿真方法。

4、掌握器件选择、引脚配置、实验箱连线、文件下载和硬件调试步骤。

讲解全加器的设计原理,演示半加器的设计步骤,学生设计;

全加器的设计、仿真结果和实验箱显示结果

1、能调用74系列的集成电路完成原理图设计。

2、能对设计文件进行时序仿真并会分析仿真结果。

3、能够进行器件选择、引脚分配。

4、能够进行实验箱连线、文件下载和硬件调试。

1、理解四路抢答器的设计原理。

2、掌握时序逻辑电路的原理图设计方法。

3、掌握时序仿真方法和步骤。

发放任务单,讲解设计原理,演示设计步骤;

学生设计、仿真、下载;

项目结果检查、评价、总结

四路抢答器的设计、仿真结果和实验箱显示结果

3-1

三人表决器的设计

1、能够用图形法设计三人表决器。

2、能用with-select语句和when-else语句设计三人表决器。

3、能够进行功能仿真、引脚配置、硬件连线、下载调试。

4、会分析仿真结果和硬件下载结果。

1、掌握VHDL语言的基本结构、标准数据类型和常用操作符等。

2、掌握with..select语句和when-else语句的用法。

3、掌握三人表决器的VHDL语言和图形化设计方法。

4、掌握三人表决器的功能仿真方法。

5、掌握三人表决器的硬件下载、调试方法。

三人表决器的任务分析;

相关语句的知识点讲解、学习;

三人表决器的设计、仿真、硬件下载;

巡回指导、答疑;

项目检查、总结。

三人表决器的设计、仿真结果和实验箱显示结果

3-2

多人表决器的设计

1、能够用for语句和loop语句设计多人表决器。

2、能够进行功能仿真、引脚配置、硬件连线、下载调试。

3、会分析仿真结果和硬件下载结果。

1、掌握for语句和loop语句的用法。

2、掌握多人表决器的VHDL语言设计方法。

3、掌握多人表决器的仿真方法。

4、掌握多人表决器的硬件下载、调试方法。

多人表决器的任务分析;

多人表决器的设计、仿真、硬件验证;

巡指导、答疑;

项目提交、检查、总结。

多人表决器的编译、仿真和硬件下载结果

4-1

3-8译码器的设计

1、能够应用文本法设计3-8译码器。

2、能够熟练运用process和case语句设计程序。

3、能够对设计好的程序进行仿真和硬件下载调试。

1、理解3-8译码器的设计原理。

2、掌握process语句和case语句的使用方法。

3、掌握功能仿真方法和硬件下载方法。

步骤:

教师下发任务下达书、共同分析任务;

然后讲解知识点并示范教学;

学生上机实操练习,分组完成设计,上交作业;

最后学生互评、自评,教师总评并布置课后的任务和下次课的任务。

3-8译码器的仿真结果

4-2

七段译码器静态显示设计

1、能够应用文本法设计七段数码管静态显示电路。

2、能够熟练运用case语句。

3、能够对设计好的程序进行仿真和硬件下载验证。

1、理解七段译码器静态显示原理。

3、掌握七段数码管静态显示电路的设计方法。

4、掌握七段译码器的仿真、硬件下载验证方法。

布置任务、任务分析;

学生设计、仿真、硬件下载;

七段译码器的静态设计、仿真和实验箱显示结果

4-3

七段译码器动态显示设计

1、能够应用文本法设计七段数码管动态显示电路。

2、能够熟练运用case语句设计。

1、理解七段译码器动态扫描原理。

3、掌握七段数码管动态显示电路设计方法。

4、掌握七段数码管译码器的仿真、硬件下载验证方法。

七段译码器的动态设计、仿真结果和实验箱显示结果

5-1

1位计数器的设计

1、能够利用if-else语句设计带功能端(清零,复位等)的1位计数器。

2、能够进行功能仿真并会分析仿真结果。

3、能够进行引脚配置、硬件连线下载调试并会分析结果。

1、了解同步计数器和异步计数器的区别。

2、掌握1位计数器的VHDL语言设计方法。

3、掌握VHDL语言中变量的使用方法。

4、掌握计数器的仿真方法和硬件下载验证方法。

1位计数器的仿真结果和实验箱显示结果

5-2

2位计数器的设计

1、能够利用if-elsif-else语句设计带功能端的2位计数器。

1、掌握if-elsif-else语句的编程方法。

2、掌握2位计数器的VHDL语言设计方法。

3、掌握计数器的仿真方法和硬件下载验证方法。

学生设计、仿真、硬件验证;

2位计数器的仿真结果和实验箱显示结果

5-3

LPM宏功能模块设计各计数器

1、能够利用LPM宏功能模块设计各种进制的计数器。

1、掌握用LPM宏功能模块设计常用计数器的方法。

2、掌握计数器的仿真方法和硬件下载验证方法。

然后讲解并示范教学;

学生上机实操练习,分组完成硬件下载测试,上交作业;

任意进制计数器的仿真结果和实验箱显示结果

1、能够进行方案论证和比较。

2、能够对数字钟进行总体设计和子模块设计。

3、能够利用上次课的24进制和60进制计数器设计数字钟。

4、能够设计具有调时、调分功能和闹铃功能的数字钟。

5、能够进行模块仿真、系统仿真和硬件下载调试并解决常见问题。

1、熟悉数字钟整体设计方案。

2、掌握调时、调分的设计原理。

3、掌握数字时钟的自顶向下混合输入的层次化设计方法。

4、掌握子模块和系统

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 整体 教学 设计

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰豆网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整word版)信息论与编码期末考试题----学生复习用.doc

(完整版)固定资产盘点表.xls

(完整版)固定资产盘点表.xls